Instructor

Bevan Baas

Teaching Assistant

Yechengnuo Zhang

ycnzh@ucdavis.edu

Office hours

Mon 11:50 am after lecture

Wed 11:50 am after lecture

Fri 2–3pm, Kemper 2101 (Feb 21, Kemper 2157)

Lecture

MW 10:30–11:50 am

Bainer 1062

Prerequisites: EEC 151 (formerly 150B), EEC 170, and EEC 180; or consent of instructor

Catalog description

Digital signal processors, building blocks, and algorithms. Design and implementation of processor algorithms, architectures, control, functional units, and circuit topologies for increased performance and reduced circuit size and power dissipation.

Goals: Through this course, students will develop the necessary skills to design simple synthesizable processors suitable for numerically intensive processing with an emphasis on small chip area and high-performance. Secondly, students will learn to design processors for simple digital signal processing tasks through the simultaneous design of DSP algorithms, processor architectures, and hardware design.

Grading

The exam covers material covered during the entire quarter. You may bring one page of double-sided hand-written (no photocopying) notes to the quizzes.

Other references

| Read by | Paper | Comments |

| Wed, Jan 8 | Programmable DSP Architectures: Part I, Edward A. Lee, ASSP Magazine, October 1988. | Easy to read article on the most notable features of programmable DSP processors. These first-generation DSP processors were more clearly distinguished from general-purpose processors than they are today. Note the publication date of 1988—many of the technical specifications are impressive only when considered in the context of the technology available at that time. |

| Reference | Programmable DSP Architectures: Part II, Edward A. Lee, ASSP Magazine, January 1989. | Easy to read article presenting an overview of issues of programming pipelined DSP processors with complex organizations. |

| When needed |

linux: ECE machines and tool setup

linux: A few useful commands, linux: Example linux intro video linux: A few Common Problems Make Frequent Backups of Your Work |

Notes on logging into ECE linux machines and your CAD tool environment setup

Notes on a few useful linux commands |

| When needed |

verilog: notes to run Cadence NC and Simvision verilog: common pitfalls with suggestions verilog: example code |

Notes on running ncverilog here at UC Davis |

| When needed |

verilog: Quick Reference For

Verilog, R. Madhavan

[2up]

verilog: Verilog Quick Reference Guide, S. Sutherland, skim it verilog: Verilog tutorial, Deepak Tala |

A helpful and handy reference.

Convenient and very nicely presented. Note it covers constructs that shouldn't be used for sythesizable code such as signal strengths and primitives. [original] |

| When needed | Synopsys Design Compiler notes |

Notes and starter files for Synopsys' Design Compiler, and details on our standard cell library |

| Reference | A Signed Binary Multiplication Technique, A. D. Booth, Quarterly Journal of Mechanics and Applied Mathematics, June 1951. | Classic paper introduces the Booth Algorithm. |

| Reference | High-speed Arithmetic in Binary Computers, O. L. MacSorley, Proceedings of the IRE, January 1961. | Classic paper that introduces the Modified Booth's Algorithm which is commonly used in hardware implementations. |

| Mon, Feb 3 | SPIM: A Pipelined 64 x 64-bit Iterative Multiplier, M. Santoro and M. Horowitz, IEEE Journal of Solid-State Circuits, April 1989. | Classic paper is that apparently the first to describe the 4:2 adder. It certainly contributed to the popular use of the 4:2 and its use in adding multiplier partial products. |

| When needed |

matlab: notes for

running matlab: tips and functions for 281 |

Notes for running matlab here at UC Davis, and some functions and examples |

| Th, Feb xx Skim. |

An Algorithm for the Machine Calculation of Complex Fourier Series, James W. Cooley and John W. Tukey, Mathematics of Computation, April 1965. | The paper that popularized FFTs. |

| Th, Feb xx Skim. |

Historical Notes on the Fast Fourier Transform, James W. Cooley, Peter A. W. Lewis, and Peter D. Welch; Proceedings of the IEEE, October 1967. | Some notes on FFT history 2 years after the seminal Cooley & Tukey paper. |

| Reference | Trends in Multicore DSP Platforms, Karam, AlKamal, Gatherer, Frantz, Anderson, Evans, IEEE Signal Processing Magazine, November 2009. | A paper with a thorough and detailed survey of modern multicore DSP processors |

| Number | Due Date | Tentative % course grade | Material covered |

1 |

Sun, Jan 26, 11:59 pm | 18% | Binary arithmetic and conversion, verilog, and many-input adders |

2 |

Sun, Feb 9, 11:59 pm | 14% | Synthesis, adders, pipelining |

3 |

Sun, Mar 2, 11:59 pm | 18% | Digital filter tools, design, and optimization; saturation; rounding |

4 |

Wed, Mar 19, 11:59 pm | 25% | tan(θ) generator, convolutional neural net engine |

All work for a particular hwk/project must be submitted at one time.

If an assignment is reviewed in class, no credit is possible for late work. If an assignment was not reviewed in class, there will be a 1/3 reduction of remaining credit per day (i.e., 100% → 67% → 44% → 30% ...).

Normally late work can not be accepted after its deadline however if a serious issue such as an illness prevents you from completing work on time, obtain a verifiable written excuse, bring it to the instructor, and something will be worked out.

To request a regrade, submit: 1) a short description of the suspected grading error, 2) the following statement on your regrade request with your signature immediately below it: "I certify that I have not altered this work in any way after it was returned to me. I understand that such altering would constitute a violation of the Code of Academic Conduct."

.

.

| Date | Topics | Handouts |

| Mon, January 6 |

Course introduction DSP overview |

Course Introduction Key attributes of DSP processors |

| Wed, January 8 |

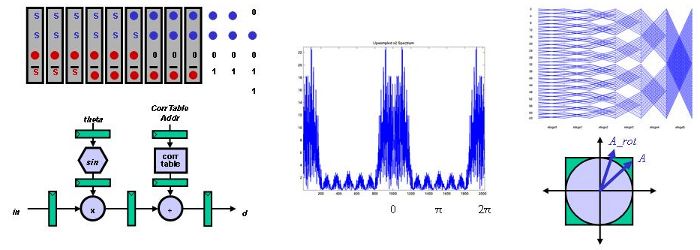

Seven basic diagrams Chip design methodologies, Multiply-accumulator (MAC), Convolution, FIR, dot products Quantization noise, word width, and SNR |

Basic diagrams Chip design methodologies |

| Mon, January 13 |

Number representation I: fixed-pt integer Sign extension for 2's complement Number representation II: fixed-pt fractional Number representation III: Floating point Number representation IV: Block floating point |

Quantization Noise and Word Size Sign Extension Floating Point |

| Wed, January 15 |

Number representation V: Redundant (carry-save) 3:2 carry-save adders 4:2 carry-save adders Fast carry-save addition Floating pt to fixed pt conversion Adders & subtractors |

Float-Fixed conversion Adders & subtractors |

Mon, January 20 |

Martin Luther King Jr. Day | |

| Wed, January 22 |

Adders: multiple-input Verilog Overview Verilog Language basics Verilog Time and delay |

Adders: Efficient Multiple Input Verilog 1: Overview Verilog 2: Language basics Verilog 3: Time and delay |

| Mon, January 27 |

Verilog Common mistakes Verilog Hardware vs. testing Verilog decoder examples Adders: faster carry-propagate Carry-Select adders Carry-Lookahead adders FFs, registers, and The 9 Rules |

Verilog 4: Common mistakes Verilog 5: Testing Verilog 6: Decoder example Adders: Faster CPAs Flip-flops and registers |

| Wed, January 29 |

Robust clock design Critical timing relationships Synthesis Hardware multipliers Booth encoding of multipliers I Read paper by M. Santoro |

Robust clock design Critical timing relationships Synthesis  JAN 29, SLIDE 133 JAN 29, SLIDE 133Multipliers  JAN 29, Many edits. MAR 10, Slide 191 JAN 29, Many edits. MAR 10, Slide 191Booth encoding |

| Mon, February 3 |

Booth encoding of multipliers II Example multiplier Squaring Fixed-input multiplication |

Example Multiplier Squaring Fixed Input Multiplication |

| Wed, February 5 |

dB Digital filters Time-domain convolution Frequency-domain multiplication Digital filter coefficient design Parks-McClellan and remez() Seeing the freq. response of filters Estimating spectral magnitude of signals FIR filter hardware FIR scaling |

dB Digital Filter Coefficient Design Estimating Spectral Magnitude FIR filter hardware  FEB 10 FEB 10 |

| Mon, February 10 |

Saturation Compression Rounding I |

Saturation Rounding  FEB 12, SLIDE 368 FEB 12, SLIDE 368 |

| Wed, February 12 |

Rounding II Drive through processing Complex addition, multiplication, rotation, format conversion |

Drive Through Processing FEB 12, Many edits FEB 12, Many editsComplex Arithmetic  FEB 12, Many edits FEB 12, Many edits |

Mon, February 17 |

Presidents' Day | |

| Wed, February 19 |

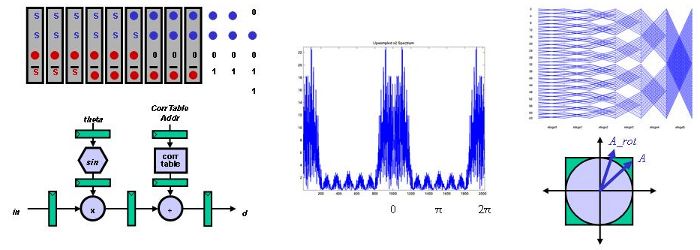

Complex magnitude estimation Multiplication scaling Control circuits Counters |

Complex Signal Magnitude Estimation Multiplication Scaling Control and counters |

| Mon, February 24 |

Finite state machine design Memories: categories, structures, types |

FSMs Memories |

| Wed, February 26 |

Memories: macros, synthesized, off-chip Memories: using in standard-cell ASIC designs Generating complex functions I |

Gen Complex Functions |

| Mon, March 3 |

Generating complex functions II Signals in time and frequency Multi-rate processing Upsampling, decimation I |

Signals in Time and Frequency Multi-rate signal processing |

| Wed, March 5 |

Upsampling, decimation II Nyquist filters Nyquist filters with upsampling Discrete Fourier transform (DFT) Fast Fourier transform (FFT) |

downsamp_movie.m Nyquist Filters DFT & FFT Background |

| Mon, March 10 |

Various FFT algorithms The RRI-FFT Linear convolution using DFT/FFTs Viterbi decoders |

FFT Algorithms The RRI FFT Viterbi Decoding |

Wed, March 12 |

Exam | |

Extra office hours:

|

||

Last update: March 18, 2025