| Mon | Tue | Wed | Thur | Fri | |

|

Alireza Zeraatkar abolhasani@ucdavis.edu |

3:00–4:00pm Kemper 2110 |

8:00am–11:50am Lab A01 Lab Assistant: Savio Esmailzadeh |

|||

|

Derek Li dsli@ucdavis.edu |

12:00pm–3:50pm Lab A03 Lab Assistant: Liam Peck |

11:00–12:00pm Kemper 2110 |

|||

| Dr. Baas | 7:30–8:00pm |

7:30–8:00pm | 2:00–3:00pm Email to meet by zoom |

|

Homeworks will normally be due Friday at 11:59 pm. Unfortunately, late homeworks cannot be accepted for a number of reasons.

Each major portion of each problem will be graded on a three-point scale: 0 (not a full effort), 1 (close but fundamental problem), and 2 (correct or with a very minor problem). For more challenging problems, points may be multiplied; e.g., [0,2,4 pts] or [0,3,6 pts].

Quizzes are designed such that students that keep up with material should earn high scores. Students that do not keep up with material will likely receive much lower scores. Unless stated otherwise, potential quiz and exam topics include material covered up to and including the previous lecture, and generally emphasize material since the last quiz/midterm.

The midterm and final exam are mandatory components of this course. They are designed to test a working knowledge and understanding of concepts, not just mechanical procedures. Unfortunately, no early or late exams are possible. If an unavoidable emergency prevents your attendance at the midterm or final, you will be required to submit written proof of the emergency and the make-up exam will likely be given as an oral exam with the instructor.

Quizzes, the midterm, and the final exam will cover material from:You may bring one page of double-sided hand-written (no photocopying) notes to the quizzes, midterm and final. All are otherwise closed-book and closed-notes.

The final exam is cumulative but with an emphasis on material since the midterm.

Notify the instructor of clear and significant grading errors within a week of being returned. Due to the inherent subjectiveness of grading and to be fair to all students, only truly significant mis-grades will result in a grade change. Submit to the instructor: 1) a short description of the suspected grading error, 2) the following statement on your regrade request with your signature immediately below it: "I certify that I have not altered this work in any way after it was returned to me. I understand that such altering would constitute a violation of the Code of Academic Conduct." Note that to discourage falsified regrading, some number of all graded assignments/labs/exams will be photocopied after the initial grading.

Unfortunately it is generally impossible to make exceptions to the normal flow of the course (e.g., deadlines, rescheduling exams, etc.) other than for highly unusual circumstances (e.g., a medical emergency), in which case you must submit a written verifiable excuse to the instructor.

In this course unless stated otherwise, all work must be done individually—meaning done entirely by the student whose name is on the work. At the same time, discussing appropriate high-level concepts with other students are important steps in the learning process and are strongly encouraged.

The course Collaboration Policy explains the fine line between working together appropriately and inappropriately..

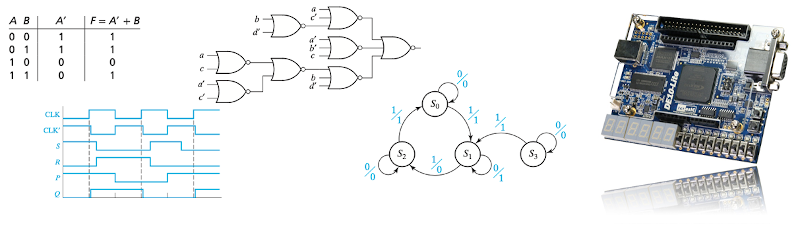

We will use the Quartus design tool to synthesize verilog designs to

run on the FPGAs. A free version has all the capabilities needed for

this class so that is what we will use. Downloading details are given

in posted handouts. Other versions which require a license are available

and may appear on workstations in Kemper 2110

however the operation of the functions are

the same as with the free version.

Quartus may also be run on the linux workstations in Kemper 2107 with

the command:

/software/Altera/16.1/quartus/bin/quartus &

Printing in 2110 Lab. Use the printer named "\\foa-repo-print1.ou.ad3.ucdavis.edu". Once selected, a window will pop up asking you to enter your kerberos ID and password. Once the credentials are verified, go to the printer and swipe your Aggie card to finish the printing process. The cost is $0.10/page.

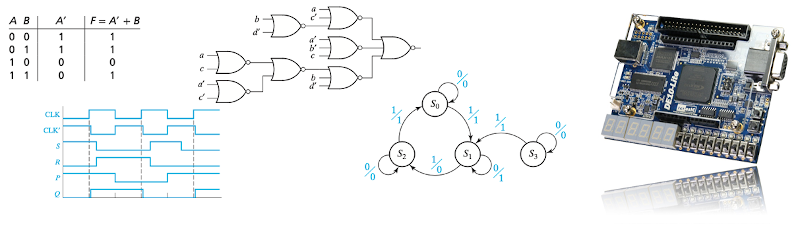

Each lab period has four major components:

Prelab checkoff. Except for Lab 1, prelabs are due at the beginning of the lab section. Unfortunately, points can not be given for late prelabs. They will be graded quickly on a scale from 0–5 points by your TA.

Come to lab prepared to show your prelab work to your TA.

Submit your Prelab to your TA as soon as you arrive and they will be checked-off and returned in the first ~10 minutes of the period.

Your TA will perform your prelab checkoff at the beginning of lab.

Checkoffs of your design and simulation work must be checked off by a TA. See the Assignments table below for the week labs are due. Checkoffs should ideally be done right after the prelabs are checked but can usually be done before the end of the lab period.

Checkoffs have three main steps:

Get ready to calculate the hash, compile your design, and demonstrate it on your FPGA board

Notify your TA that you are ready for your checkoff

Checkoffs have five main steps: 1) Finalize your code and have your report ready to submit. 2) Your TA will verify the code used in your project is the same as your printed code. 3) The code is compiled and run, and you demo your design to your TA. 4) Submit your report. 5) When a lab requires you to upload your code, sometime before the end of your lab period, upload the code you wrote to canvas and you're done!

Checkoffs are graded on the following scale (note there is no "4"):

For several logistical reasons, you may have your designs checked off during only these time periods:

General lab work. Most of the lab period is spent on the current week's lab.

Upload material to be submitted such as Verilog, simulation printouts, etc. must be uploaded to canvas before the end of your lab session

Due to the large amount of grading for TAs and the fast pace of material in lab, credit for late lab work is not possible or minimal.

Normally TAs will not be able to debug students' circuits in detail so they are available for other students. If your TA agrees to assist you in debugging your circuit, show your TA your design materials such as block and timing diagrams first. Normally, TAs will focus on teaching debugging techniques rather than finding a particular bug in your design.

Because TAs are almost always 100% busy in lab, you may unfortunately not attend other lab sessions.

The labs are mandatory components of this course.

Lab grades will be adjusted at the end of the quarter so the average grade for each section is the same—this removes unavoidable differences in grading from different TAs.

No food or drinks are allowed in the lab. Unfortunately violations of this rule have gotten worse lately so the ECE staff is getting pretty strict on this rule.

Take care of your FPGA board. You will need to buy a new one if you lose or break yours. They can be purchased from Terasic for $55 (plus expensive shipping) or much more from amazon.

Quartus display fix for problems such as clipped text or very small icons when using high resolution displays

Lab circuit schematics - 3 types that you should draw for circuits you build when applicable

| Date | Reading | Lecture | Notes and Handouts |

| Wed, Sept. 25 | Unit 1 |

Course introduction Digital processing trends |

Lecture 1 slides |

| Mon, Sept. 30 | Unit 2 |

Binary arithmetic Unsigned and signed number review Boolean basic operators |

Unit 1 Unit 2a |

| Wed, Oct. 2 | Unit 3 |

Boolean algebra basic theorems I Sum of products Product of sums |

Unit 2b |

| Mon, Oct. 7 | Unit 4.1–4.6 |

Boolean algebra basic theorems II Minterms |

Unit 3 LawsAndTheoremsOfBooleanAlgebra [Roth] Unit 4 |

| Wed, Oct. 9 | Unit 5 |

Minterms II Maxterms Incompletely specified functions Karnaugh Maps |

Minterms.ppt Minterns.pdf Unit 5 |

| Mon, Oct. 14 |

Karnaugh Maps II Karnaugh Map Extras |

Unit 5 Extra |

|

| Wed, Oct. 16 |

Unit 6 Unit 7 |

Quiz 1 5 input variable K-Maps Multiplexers Implicants Minimum expressions |

|

| Mon, Oct. 21 |

Unit 9.1-9.2 |

Quine-McCluskey Multi-level circuits I Functional completeness Multi-level circuits II NAND, NOR 2-level circuit conversions |

Unit 6 Unit 7 Ex: Multi-level NOR |

| Wed, Oct. 23 |

Unit 4.7 (adders & subtracters) Unit 9 |

Half adder Full adder Ripple carry adder Logic using multiplexers Buses |

Handout: Adders Unit 9, muxes II Unit 9: MSI |

| Mon, Oct. 28 |

Unit 9.6 Unit 8 |

Tri-state drivers Decoders Encoders ROMs |

|

| Wed, Oct. 30 |

FPGAs Clockless latches Level-sensitive latches Flip-flops |

Unit 11: Latches, FFs |

|

| Mon, Nov. 4 |

Midterm

New location: TLC 1010 Histogram |

||

| Wed, Nov. 6 |

Unit 11 |

Reset and preset Clocks Registers Enable-able registers Accumulators |

Handout: Flip-flop reset and preset Unit 12: Registers, counters |

| Mon, Nov. 11 | Happy Veteran's Day

|

||

| Wed, Nov. 13 |

Unit 12 Unit 13 |

Clocks II Shift registers PLDs, PLAs, wired AND/OR Binary counters, General counters |

Handout: clocks Unit 9.6: PLDs Handout: PLA example Datasheet: CPLD example, see pgs. 15–18 |

| Mon, Nov. 18 |

Unit 14 |

Timing and hazards Analysis of sequential circuits |

Unit 8: Hazards CounterEx.ppt |

| Wed, Nov. 20 | Unit 15 |

New location: Everson 176

Quiz 2 Intro to Moore & Mealy FSMs Analysis of Moore FSMs Analysis of Mealy FSMs Moore vs. Mealy input to output timing |

Unit 13 Unit 14 |

| Mon, Nov. 25 | Unit 16 |

Design of FSMs Moore design example Mealy design example |

Handout: Sync vs. Async reset & preset |

| Wed, Nov. 27 | Unit - |

One-hot design example Moore vs. Mealy critical path Elimination of redundant states |

Unit 15 Handout: 7 diagrams |

| Th–Fri, Nov. 28–29 | Happy Thanksgiving

|

||

| Mon, Dec. 2 | Unit 18 |

Implication table Efficient state assignments Sequence detection FSM |

Unit 16 Critical timing relationships |

| Wed, Dec. 4 |

New location: TLC 1020 Sequential circuits using ROMs, PLAs Critical timing relationships HDL--Verilog basics |

Lecture 20 notes Unit 18 Handout: HDLs |

|

| Extra office hours—subject to change, re-check

before coming to office hour Wed, Dec 4, 4 pm–5 pm (2110) Th, Dec 5, 3 pm–5 pm (2110) Fri, Dec 6, 11 am–1 pm (2110) Fri, Dec 6, 2 pm–3 pm (Kemper 2037) Fri, Dec 6, 4 pm–6 pm (2110) Mon, Dec 9, 12 pm–2 pm (2110) Mon, Dec 9, 3 pm–6 pm (2110) Tue, Dec 10, 8 am–4 pm (2110) |

|||

| Tue, Dec. 10 8:00am–4:00pm |

Last chance Lab 6 checkoffs—sign up

for ONE time slot only See Dec 4, 6:22pm email announcement with subject "Tuesday 12/10 Lab 6 Check Off Appointments: EEC 18, Fall '24" for the Sheet link (not publicly posted here). Come early enough to make sure your design is working by the start of your 5-minute appointment. |

||

|

Wed, Dec. 11 8:30pm–10:30pm |

Final exam New location: TLC 1010 |

||

Notes from Fall 2021:

| Week | Prelab due and work in Lab |

Lab report due at end of lab section |

Hwk due Friday 11:59pm |

Homework problems (Problems in italics have their solution in the textbook) (The comment "do not submit" applies to only the problems on that line) |

| Sep 25 – Sep 27 | No lab | – | – |

|

| Sep 30 – Oct 4 | Lab 1 |

– | 1 |

Unit 1: 1, 2, 4, 5 (do subt. by adding 2's comp),

7de (2's comp only), 8,

10 Unit 2: Study Guide 1–10 (do not submit) 1, 2 |

| Oct 7 – Oct 11 | – | Lab 1 | 2 |

Unit 2:

4, 5a, 11ace, 13ac, 15b, 16a, 23bd Unit 3: Study Guide 1&5 (do not submit) Programmed Exercises 1–5 (do not submit) 6b, 7b, 8, 18f, 21a, 29 |

| Oct 14 – Oct 18 | Lab 2 | – | 3 |

Unit 4:

Study Guide 2–6 (do not submit) 1, 3, 9, 14, 20, 29 Unit 5: Study Guide 5–8 (do not submit) Programmed Exercises 1–2 (do not submit) 3, 6, 9a, 20abc, 25cd, 33 |

| Oct 21 – Oct 25 | Lab 3 | Lab 2 | – |

Unit 6:

Study Guide 2bdhi, 3, 4, 6ab (do not submit) Programmed Exercise 6.1 (do not submit) 2, 3 (do not submit) |

| Oct 28 – Nov 1 | – | Lab 3 | 4 |

Unit 7:

Study Guide 1, 2, 4, 5 (do not submit) 1, 4, 7, 20a, 21b, 32 |

| Nov 4 – Nov 8 | Lab 4 | – | 5 |

Unit 9:

Study Guide 2–5 (do not submit) 1, 4, 14, 20, 27, 32a Unit 11: Study Guide 2b–e, 3b–c, 4b–e 5a–c, 6b–c, 7b, 8a–d (do not submit) Programmed Exercise 11.35 (do not submit) 1, 7 |

| Nov 11 – Nov 15 | – | Lab 4 | 6 |

Unit 9:

Study Guide 6 (do not submit) 8, 32b Unit 11: 2, 10, 11, 16, 22, 24, 26 Unit 12: Study Guide 2a–d, 3a–g, 4a–k (do not submit) |

| Nov 18 – Nov 22 | Lab 5 |

– | 7 |

Unit 8:

Study Guide 5, 6 (do not submit) 1, 2, 9, 10 Unit 12: 3, 6, 7b, 8b, 13, 17abe Unit 13: Study Guide 2–6 (do not submit) Programmed Exercise 1 (do not submit) 7, 18 |

| Nov 25 – Nov 29 | Lab 6 DEC 2 DEC 2 |

Lab 5

|

8 Mon, Dec 2 noon |

Unit 13:

21 Unit 14: Programmed Exercise 1–3 (do not submit) 12, 31, 45 Unit 15: Study Guide 7, 11 (do not submit) 9 |

| Dec 2 – Dec 6 | – | Lab 6

Due Tue, Dec. 10, 4pm |

Do not submit |

Unit 15:

Study Guide 9 (do not submit) 23 Unit 16: Study Guide 2, 3, 5 (do not submit) 2, 15, 23 (do not submit) Unit 18: Study Guide 1, 2 (do not submit) |