Normally lab will be held in Kemper 2107.

Due to the large amount of grading for TAs and the fast pace of material in lab, credit for late lab work is not possible or minimal.

Checkoffs: late checkoffs are normally not possible.

Lab reports: late reports can not be accepted

Canvas uploads: the entire lab's grade will be reduced by 10% if late up to one day and reduced to zero after that. Please verify your upload to avoid penalty.

Incorrect canvas submissions (e.g., not matching demo code or with extraneous files) must be corrected by the student and will be considered late

Normally the TA will not be able to debug students' circuits in detail so they are available for other students. If the TA agrees to assist you in debugging your circuit, show your TA your design materials such as block and timing diagrams first. Normally, TAs will focus on teaching debugging techniques rather than finding a particular bug in your design.

Take care of your FPGA board and camera. You must buy a new one if you lose or break yours. They can be purchased from Terasic (plus expensive shipping) or perhaps other sources online.

CAD Tool Installation and Setup

-

Installing Quartus, Modelsim, and SystemBuilder

The Quartus Prime Standard Edition is needed for the DE1-SoC board. -

A few useful linux commands, Example linux intro tutorial

JAN 14

JAN 14

CAD Tool Usage

Finding key metrics of your FPGA design

Tips and tutorials for using various FPGA and board features

-

Notes on active high/low inputs/outputs for the DE-10 Lite and DE1-SoC

-

Displaying to a VGA monitor

-

Creating verilog-ready bitmaps from image files

Using the accelerometer on the DE10-LITE board (different for the DE1-Soc)

-

Misc: http://www.asic-world.com/ (some examples, however do not use if they conflict with class guidelines)

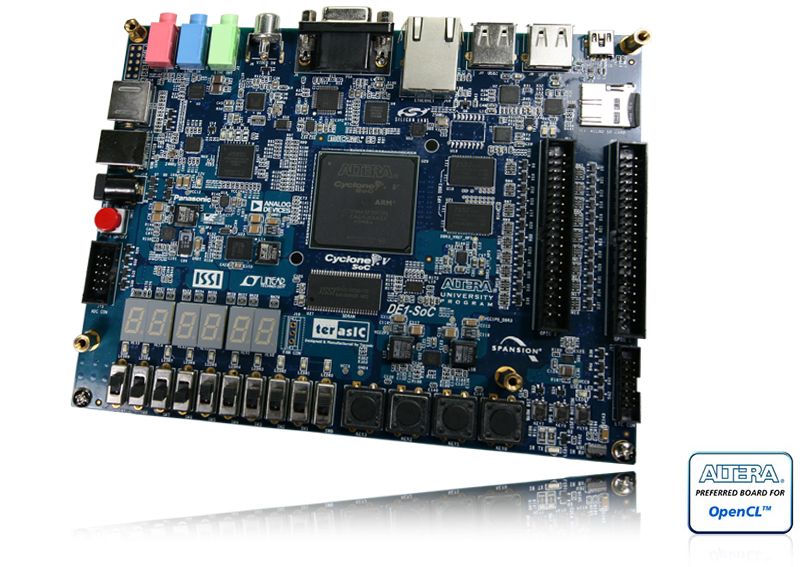

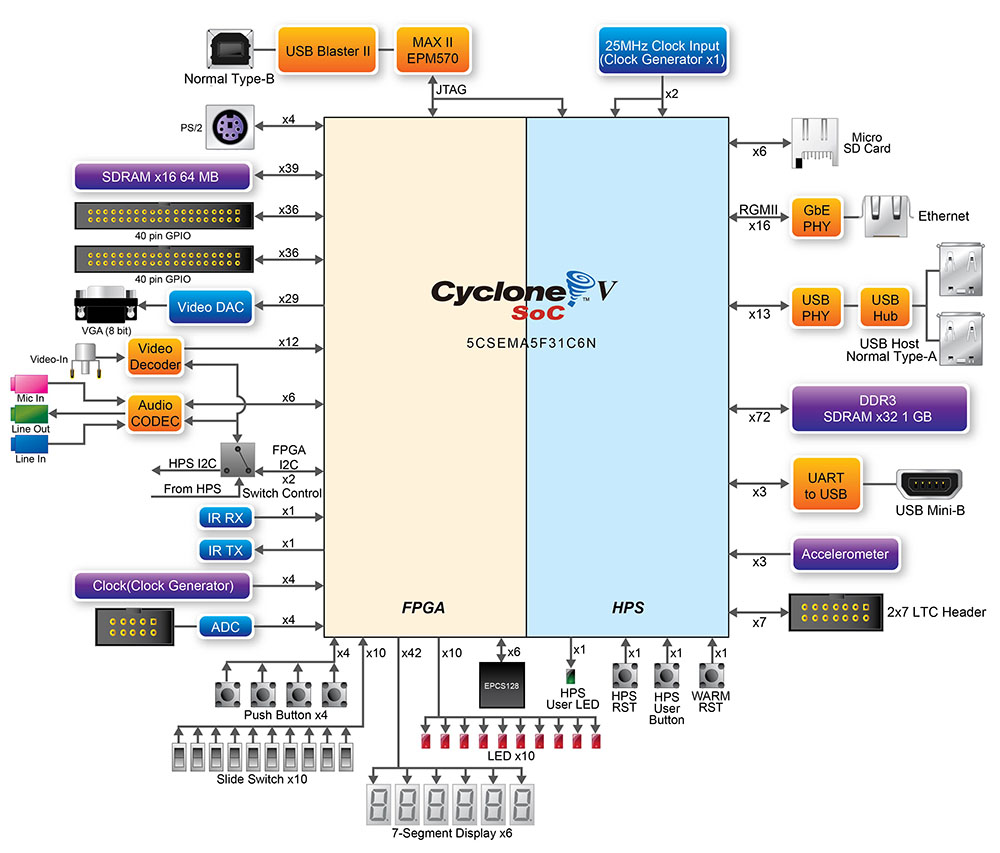

The Terasic DE1-SoC FPGA board

-

In lab you will use a Terasic DE1-SoC board which contains a Cyclone V SoC 5CSEMA5F31C6 chip.

- DE1-SoC User Manual (rev.F/rev.G Board)

- Cyclone V Device Overview

5C: Cyclone V

SE: SoC with enhanced logic/memory

M: No hard PCIe and 1 hard memory controller

A5: 85K logic elems,

32,070 Adaptive Logic Modules (ALMs),

397 M10K blks,

768 Memory Logic Array Blocks (MLAB) @ 640 bits each = 480 Kb,

174 18x18 multipliers,

87 variable precision DSP blocks

F: Fine line BGA package type

31: 896 pins

C: Commercial temperature range (0° C – 85° C)

6: Fastest FPGA fabric speed grade

-

The Cyclone V Device Handbook (best source of details for structures such as the DSP blocks)