### UNIVERSITY OF CALIFORNIA, DAVIS Department of Electrical and Computer Engineering

#### **EEC 181A**

Winter 2025

### Lab 4: Using the VGA Interface on a DE1-SoC Board

#### **I. Introduction**

The DE1-SoC board has a 15-pin D-SUB connector designed for VGA (Video Graphics Array) video output. The VGA synchronization signals are generated directly from the Cyclone V SoC FPGA. The Analog Devices ADV7123 triple 10-bit (only the highest 8-bits [9:2] are used) high-speed video DAC transforms the three color signals (red, green, and blue) from digital to analog form. Although the VGA interface can operate at multiple resolutions, this document is written for 640 × 480 pixel resolution, which contains 307,200 pixels per image and 18,432,000 pixels per second @ 60 frames per second.

#### **II. VGA Timing Specifications**

For more details of the timing specification for VGA synchronization and RGB (red, green, blue) data, search the web for a good tutorial.

Figure 1 illustrates the basic timing requirements for each row (horizontal) displayed on a VGA monitor. The *vga\_col\_sync* (HSYNC) signal is pulsed low to signify the beginning ("back porch") of a row of pixels ("display interval"), and is again pulsed low ("front porch") after the end of the row. During the display interval, pixel RGB data drives each pixel ideally at a rate of 25.175 MHz (39.72 ns per pixel) from left to right across the pixel row. To simplify the FPGA's setup, we use the 50.000 MHz default clock which divides conveniently to 25.000 MHz.

Figure 1. VGA Timing Specifications. [https://www.epanorama.net/documents/pc/vga\_timing.html]. (Note: the 25.17  $\mu$ s "Active video time" seems to be in error; it should probably be 39.72 ns × 640 = 25.42  $\mu$ s.)

The timing of vertical synchronization using *vga\_row\_sync* is similar to timing of a single row, except that a pulse signifies the end of one frame and the start of the next, and the data in between comprises all of the rows within a single video frame.

# III. The VGA\_controller.v Module

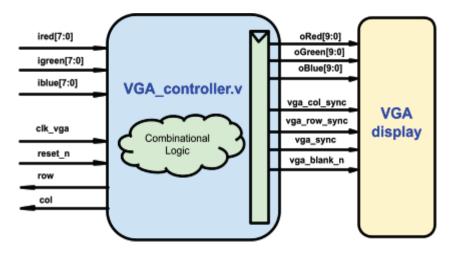

The VGA\_controller.v module is designed so that the colors that are driven on the signals *ired*, *igreen*, and *iblue* will appear at the pixel location indicated by *col* and *row*.

Figure 2. VGA\_controller module block diagram

| Port names (Verilog) | Direction | Width | Description                             |

|----------------------|-----------|-------|-----------------------------------------|

| clk_vga              | Input     | 1     | VGA clock @ 25.000 MHz                  |

| reset_n              | Input     | 1     | VGA reset, active low, asynchronous     |

| ired                 | Input     | 8     | The input value of red color            |

| igreen               | Input     | 8     | The input value of green color          |

| iblue                | Input     | 8     | The input value of blue color           |

| vga_col_sync         | Output    | 1     | VGA horizontal synchronization signal   |

| vga_row_sync         | Output    | 1     | VGA vertical synchronization signal     |

| vga_sync             | Output    | 1     | VGA synchronization signal              |

| vga_ blank_n         | Output    | 1     | VGA blank signal, active low            |

| ored                 | Output    | 8     | The value of red color to VGA           |

| ogreen               | Output    | 8     | The value of green color to VGA         |

| oblue                | Output    | 8     | The value of blue color to VGA          |

| col                  | Output    | 13    | Indicates the horizontal pixel position |

| row                  | Output    | 13    | Indicates the vertical pixel position   |

Table 1. Ports of Interface

The timing of when a pixel is displayed is indicated by two signals, *col* and *row*. *col* indicates the current horizontal pixel position, and *row* indicates the current vertical pixel position. *col* ranges from 0–639 and *row* ranges from 0–479.

# **IV. Sample Project Description**

To prepare for the future possibility of using the 50.000 MHz SDRAM, the example code is written with a main 50.000 MHz clock and a 25.000 MHz divided clock (done in a risky way that you should *not* do as described in Rule #7 in the *Single-bit Memories* handout). So the example code requires the mildly-awkward situation where your control circuits operate at 50.000 MHz and the pixel rate controller operates at 25.000 MHz. Fortunately the situation is entirely handled by merely calculating and outputting an RGB pixel color appropriately coordinated by the *row* and *col* signals, even though *row* and *col* will change value only *every other* cycle.

A module or always block is needed to control all of the signals in Table 2. The signals *row* and *col* indicate the row and column position for RGB information on the VGA monitor.

For example, to display the color white at the pixel position (10, 10), when the *row* and *col* signals are (13' d0010, 13' d0010), the circuit must drive the *ired*, *igreen*, and *iblue* signals all to 8' hFF.

The overall system reset signal is called *reset\_n*, is asserted low, and is driven by the push button KEY[0].

# V. Design Descriptions [100 points]

Download and modify the sample project contained in the posted file vga\_top.zip Details not specified must be chosen by you and listed in your final submission.

1) [10 points] Modify the verilog code in the sample project to draw 2 squares plus 2 rectangles that overlap each other on the VGA monitor. The color of each is selectable from one of two values chosen by the SW switches. Choose colors, sizes, and locations on the screen.

2) [25 points] Draw a 25-pixel wide  $\times$  25-pixel tall red square in the center of the display, then grow the square larger by one pixel in each direction per video frame until the whole display is red; then continuously repeat the process.

3) [10 points] When one of the SW switches is switched, change the color of the growing square dynamically such that the color of the non-black pixels change each cycle. Design, implement, and describe in your report, an algorithm of your choosing.

4) [40 points] Draw a square on the screen that moves a specified number of pixels each video frame. The number of pixels of movement is determined by four SW switches: two switches determine the horizontal speed (1, 2, 3, 4 pixels per frame) and two determine the vertical speed (1, 2, 3, 4 pixels per frame). When the square hits a frame boundary, it must bounce appropriately as a ball would bounce.

Submitted work [15 points] Submit a pdf document to Canvas with the following for each of the designs:

- Choices you made for your designs (e.g., colors, object sizes, key signals, etc.)

- Circuit diagram of the circuits you designed

- All verilog code

Extra credit [5 points max] Add two more squares to part (4) that bounce independently. Choose some method to set the velocity of each square to a different value.