This tutorial describes a method to obtain an estimate of the power dissipated by the Cyclone V FPGA on the Terasic DE1-SoC board.

-

Pull down the "Assignment" menu, then click "Settings...".

Select "PowerPlay Power Analyzer Settings"

Check the box next to "Run PowerPlay Power Analyzer during compilation".

Figure 1. Example power information shown by Quartus. Click image to show in a larger resolution. -

Select the operating temperature or voltage conditions (Optional). You may keep these values at their default settings.

Figure 2. Setting Temperature information. Click image to show in a larger resolution.

Figure 3. Setting Voltge information. Click image to show in a larger resolution. -

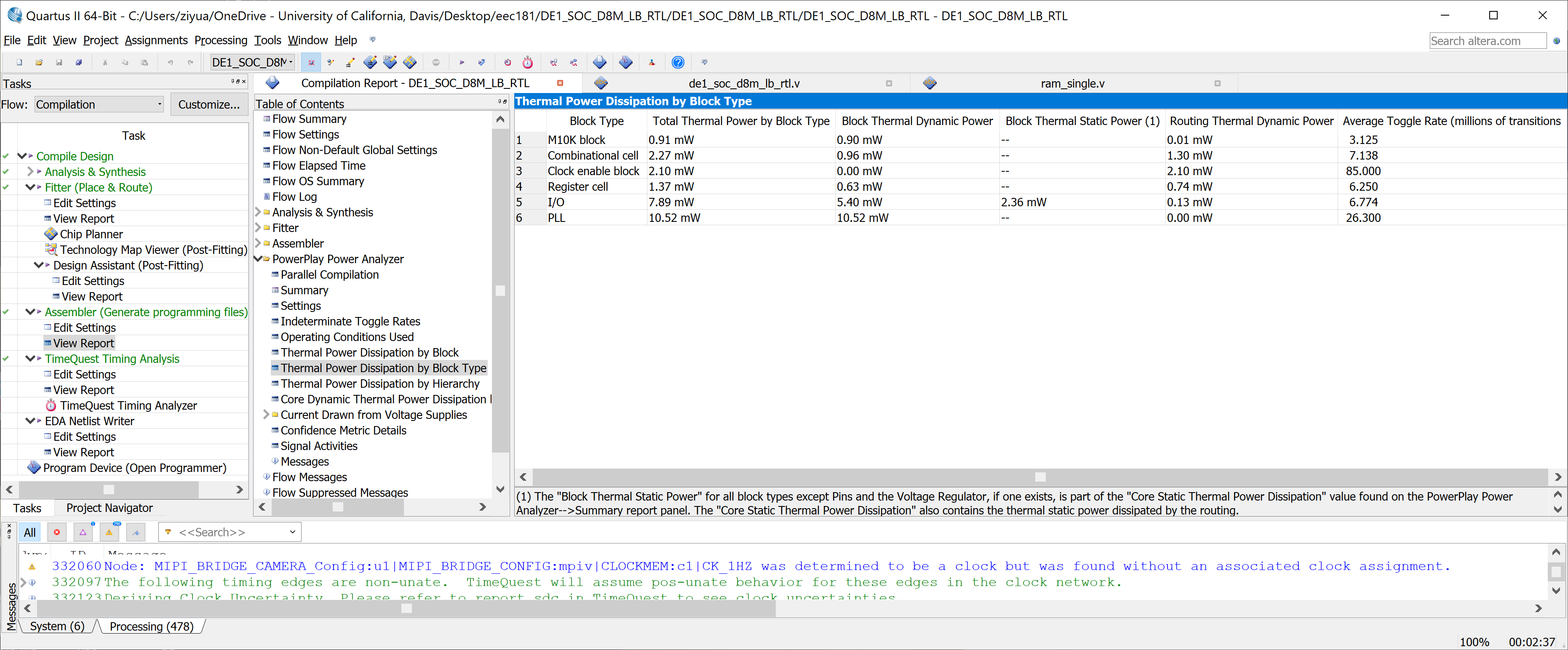

Start Compilation and the result is shown under the Table of Contents. The most interesting values include:

- Total Thermal Power Dissipation

- Core Dynamic Thermal Power Dissipation

- Core Static Thermal Power Dissipation

- I/O Thermal Power Dissipation

Figure 4. Output power report. Click image to show in a larger resolution.

Figure 5. Output power report. Click image to show in a larger resolution.

Reference page: https://www.intel.com/content/www/us/en/programmable/quartushelp/17.0/report/rpt/rpt_file_powerplay_analyzer.htm