| Mon | Tue | Wed | Thur | Fri | |

| Satyabrata Sarangi ssarangi@ucdavis.edu |

9:00am–12:50pm Lab A01 |

9:00am–10:00am |

|||

| Shifu Wu ucdwu@ucdavis.edu |

9:00am–10:00am |

4:10pm–8:00pm Lab A02 |

|||

| Harichandana Chitturi hchitturi@ucdavis.edu |

9:00am–10:00am |

9:00am–12:50pm Lab A03 |

|||

| Terry ONeill toneill@ucdavis.edu |

1:00pm–2:00pm |

3:10pm–7:00pm Lab A04 |

|||

| Tony Tsoi wctsoi@ucdavis.edu |

3:00pm–4:00pm |

3:10pm–7:00pm Lab A04 |

|||

| Ziyuan Dong ziydong@ucdavis.edu |

10:00am–11:00am |

4:10pm–8:00pm Lab A02 |

|||

| Bevan Baas |

12:00pm–1:00pm |

3:00pm–4:00pm |

3:00pm–4:00pm |

Homeworks will normally be due late Friday afternoon. Unfortunately, late homeworks cannot be accepted.

Each major portion of each problem will be graded on a three-point scale: 0 (not a full effort), 1 (close but fundamental problem), and 2 (correct or with a very minor problem). For more challenging problems, points may be multiplied; e.g., [0,2,4 pts] or [0,3,6 pts].

Several closed-book, closed-notes quizzes will be given during the quarter. They are designed such that students that keep up with material should earn high scores. Students that do not keep up with material will likely receive much lower scores. Unless stated otherwise, potential quiz topics include material covered up to and including the previous lecture, and generally emphasize material since the last quiz.

The final exam is a mandatory component of this course. It is designed to test a working knowledge and understanding of concepts, not just mechanical procedures. Unfortunately, no early or late exams are possible.

Quizzes, the midterm, and the final exam will cover material from:You may bring one page of double-sided hand-written (no photocopying) notes to the midterm and final exam.

The final exam is cumulative but with an emphasis on material since the midterm.

The quiz, the midterm, and the final exam will be proctored through zoom by your TA.

As a rule, your proctor will not be able to answer any questions during the quizzes and exams. If you are unsure about a question: 1) Make an assumption that you belive is reasonable, 2) Write your assumption clearly, 3) Answer accordingly. If your assumption is reasonable, you will receive full credit.

Normally late work can not be accepted after its deadline however if a serious issue such as an illness prevents you from completing work on time, obtain a verifiable written excuse, bring it to the instructor, and something will be worked out.

Please request grading corrections within a week of being returned to you. Non-obvious or very minor grading issues will not be considered—due to fairness to all students, the inherent subjectiveness of grading results in both missing-points and additional-points imperfections, and because it is physically impossible to go through submitted work of every student in minute detail (which would be required for ideal fairness).

In this course, all work must be done "individually"—meaning done entirely by the student whose name is on the work.

Make sure you fully understand the course Collaboration Policy and talk to the instructor if you have any questions.

We will use the Quartus design tool to synthesize verilog designs to

run on the FPGAs. A free version has all the capabilities needed for

this class so that is what we will use. Downloading details are given

in posted handouts. Other versions which require a license are available

however the operation of the functions are

the same as with the free version.

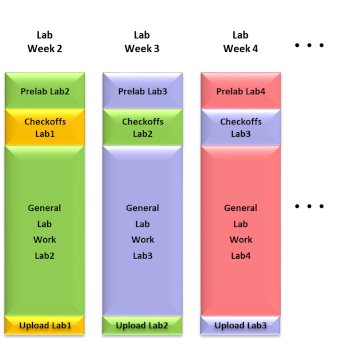

Each lab period has four major components: 1) the prelab checkoff, 2) the final checkoffs from the previous lab, 3) general lab work, and 4) uploading all required work from the previous lab.

Prelabs. Except for Lab 1, prelabs are due at the beginning of the lab section. Unfortunately, points can not be given for late prelabs. They will be graded quickly on a scale from 0–5 points by your TA.

Come to lab prepared to show your prelab work to your TA—likely by sharing your screen but possibly by another method such as sending a jpeg, as appropriate.

Your TA will perform your prelab checkoff at the beginning of lab by assigning you to a breakout room.

Main checkoffs of your design and simulation work must be checked off by a TA and is due near the beginning of the lab section one (or two) weeks after prelab checkoffs (see the Assignments table below).

Checkoffs have three main steps:

Get ready to calculate the hash, compile your design, and demonstrate it on your FPGA board

Notify your TA through slack that you are ready for your checkoff—do not use zoom chat because your TA cannot read those messages when they are in a breakout room with another student

Once you have joined a zoom breakout room with your TA, share your screen and perform the hash generation, compilation, and board download. Lastly share your camera and demonstrate your design running on your FPGA board

Checkoffs are graded on the following scale (note there is no "4"):

For several logistical reasons, you may have your designs checked off during only these time periods:

General lab work. Most of the lab period is spent on the current week's lab.

Material to be uploaded such as Verilog, simulation printouts, etc. must be uploaded to canvas before the end of your lab session

Due to the large amount of grading for TAs and the fast pace of material in lab, credit for late lab work is not possible or minimal.

Normally TAs will not be able to debug students' circuits in detail so they are available for other students. If your TA agrees to assist you in debugging your circuit, show your TA your design materials such as block and timing diagrams first. Normally, TAs will focus on teaching debugging techniques rather than finding a particular bug in your design.

Because TAs are almost always 100% busy in lab, you may unfortunately not attend other lab sessions.

The labs are mandatory components of this course.

Lab grades will be adjusted so the average grade for each section is the same—this removes unavoidable differences in grading from different TAs.

Take care of your FPGA board. You will need to buy a new one if you lose or break yours. They can be purchased from Terasic for $55 (plus expensive shipping) or much more from amazon.

Tutorial: Instantiating and using a PLL on the DE10-LITE board

Tutorial: Displaying to a VGA monitor using a combinational circuit

Misc: http://www.asic-world.com/ (some examples, however do not use if they conflict with class guidelines)

| Date | Reading | Lecture | Notes, Handouts, and Reading |

| Tue, Mar 30 | Chapter 1, 2 Chapter 3 if needed |

Course introduction Digital design overview Basics of digital systems |

Lecture 1 slides Lecture 1 notes |

| Th, Apr 1 |

Chapter 6 if needed Chapter 7 (Verilog) Appendix A |

Basic units Basic diagrams Design flow HDL to HW Verilog Overview |

Lecture 2 notes Basic units Seven basic diagrams Chip design methodologies HDL to HW |

| Tue, Apr 6 |

Verilog Language basics I |

Lecture 3 notes Verilog 1: Overview Verilog 2: Basics |

|

| Th, Apr 8 | Chapter 8 (Comb. Blocks) |

Verilog Language basics II Verilog wire, assign Verilog reg, always block |

Lecture 4 notes Example: NAND2 Verilog quick ref guide, S. Sutherland (skim quickly) [orig] |

| Tue, Apr 13 | Chapter 9 (Comb. Examples) |

Verilog Language basics III Verilog Time and delay Verilog Common mistakes Verilog Testing I |

Lecture 5 notes Verilog 3: Time and delay Verilog 4: Common mistakes Verilog 5: Testing |

| Th, Apr 15 |

Chapter 10 (Binary #s, Arith) |

Verilog Testing II Binary number formats Binary coded decimal (BCD) Binary fractional |

Lecture 6 notes Binary number formats  APR 15 APR 15 |

| Tue, Apr 20 |

Chapter 11 (Fixed/Float Pt) |

Addition Subtraction Design example: Decoders Sign extension for 2's complement Memories |

Lecture 7 notes Addition/subtraction Verilog 6: Decoder example Sign extension FFs and registers |

| Th, Apr 22 |

Chapter 13 (Arith. examples) |

Quiz

— (zoom instructions)

Single-bit memory elements Flip-flops and 9 rules of using them |

Lecture 8 notes |

| Tue, Apr 27 |

Flip-flops with reset, preset, enable Four structures in HW verilog Control circuits Counters |

Lecture 9 notes Four verilog constructs Control Circuits and Counters |

|

| Th, Apr 29 |

Chapter 14 (Seq. Logic) |

Finite state machines |

Lecture 10 notes Finite State Machines  APR 29 APR 29Example FSM circuit diagram Counter example with four views (view in slide show mode) |

| Tue, May 4 |

Chapter 16 (Datapath Seq. Logic) |

FSM design example Clocks Critical timing requirements of digital systems |

Lecture 11 notes Clocks Critical timing requirements |

| Th, May 6 |

Chapter 17 (Factoring FSMs) Chapter 19 (Seq. Examples) |

Interfacing with unsync inputs: debouncing, edge detection |

Lecture 12 notes Interfacing input signals |

| Tue, May 11 |

Chapter 15 (Timing) |

Multiple/variable freq clock hardware |

Lecture 13 notes Variable-freq clock hardware Midterm overview |

| Th, May 13 |

Midterm

— (zoom instructions)

|

||

| Tue, May 18 |

Chapter 23 (Pipelines) |

Pipelines Pipeline throughput and latency Pipelining systems |

Lecture 14 notes Pipelining |

| Th, May 20 |

Chapter 25 (Memory Sys) |

Memories I |

Lecture 15 notes Total grade class histogram as of May 20 Memories |

| Tue, May 25 |

Memories II Bit-slicing memory arrays Banking memory arrays |

Lecture 16 notes |

|

| Th, May 27 |

Chapter 21 (Sys-Level Design) |

Memory timing M9K memory blocks |

Lecture 17 notes M9K memories |

| Tue, Jun 1 |

Chapter 22 (Interface & Sys-Level Timing) Chapter 24 (Interconnect) |

System-Level design Block interfaces, timing, interconnect |

Lecture 18 notes Steps to design systems |

| Th, Jun 3 |

Field-Programmable Gate Arrays (FPGAs) Estimating circuit complexity Data word growth Binary multiplication Arithmetic: Rounding Arithmetic: Saturation |

Lecture 19 notes FPGA tutorial, 7 pages FPGA vendors and major internal components Estimating chip area Multipliers  JUN 3 JUN 3Rounding Ref: Saturation |

|

| Fri, June 4 3:30pm–5:30pm |

Final Exam

— (zoom instructions)

|

||

| Saturday, June 5 |

Office hour 9–11am, Satyabrata Sarangi Office hour 11–1pm, Tony Tsoi Office hour 1–3pm, Harichandana Chitturi |

||

| Sunday, June 6 |

Office hour 9–11am, Ziyuan Dong Office hour 11–1pm, Shifu Wu |

||

| Monday, June 7 |

Final chance for Lab 7 checkoffs. To reserve a time slot, click here: https://forms.gle/YkWDTtmcK8agvu7J6 |

||

|

12–2pm Tue, June 8 12–1:30pm Wed, June 9 11–1pm Thur, June 10 |

Return DE10-Lite

FPGA Boards Bring to Kemper Courtyard at these times, or ship it |

||

| Week | Prelab due and work in Lab |

Checkoffs and uploads due |

Hwk due Friday, 5pm |

Homework problems (Problems are tentative until approximately the Thurs 8 days before the due date, depending on material covered in lecture) |

| Mar 29 – Apr 2 |

No lab | - | - | - |

| Apr 5 – Apr 9 |

Lab 1 Cover sheet not needed |

- | - | - |

| Apr 12 – Apr 16 |

Lab 2 |

Lab 1 | 1 |

2.3, 2.10, 2.17 7.1, 7.7 (assume true=1), 7.24 (no need to test) 8.4, 8.15, 8.18, repeat 8.18 writing verilog not using building blocks |

| Apr 19 – Apr 23 |

Lab 3 APR 21 APR 21 |

Lab 2 | - |

- |

| Apr 26 – Apr 30 |

Lab 4 |

Lab 3 | 2 |

9.1, 9.14 10.14, 10.15, 10.23 (circuit diagram), 10.25–10.28 (sign mag and 2's comp only), 10.29 (use A + (-B), 10.40 11.3, 11.11 |

| May 3 – May 8 |

Lab 5 |

Lab 4 |

- |

- |

| May 10 – May 14 |

No new lab |

- | 3 |

13.14 14.6, 14.7, 14.8, 14.18, 14.19 15.1, 15.8, 15.10 16.17–16.19 (no need to simulate) |

| May 17 – May 21 |

Lab 6 MAY 18 MAY 18Video demo |

Lab 5 |

- |

- |

| May 24 – May 28 |

Lab 7 JUN 2 JUN 2Video demo |

Lab 6 |

4 |

19.1, 19.6 25.1, 25.2 using primitive in "Memory" Handout instead |

| May 31 – Jun 4 |

- |

- |

- |

- |

| Mon June 7, 4pm |

- |

Lab 7 |

|

Lab 6, 2021 spring: An Add/Subtract Calculator with an Accelerometer-Based Input

Lab 7, 2019 winter: An Image Processor using ROM Storage, with extra credit additions, by Eric Truong

Lab 5, 2018 winter: A Register-Based LED Light Display Ring, by Mark Hildebrand

Lab 7, 2018 winter: An Accelerometer-Based Video Display with extra credit additions, by Ryan Atkins

2020 summer project: An Asteroid + Spaceship Video Game on the DE10-Lite, by Christian Lum

Last update: January 17, 2024