Department of Electrical &

Computer Engineering

University of California,

Davis

EEC-282 – Embedded

System Design (formerly known as hardware/software Codesign)

Spring Quarter 2005

Overview

of the Course

Embedded systems are everywhere. The key features

of embedded systems are:

- Real-time

- Flexibility

- Adaptive

- Low Power

- Cost

- Size

- Diverse

Design and analysis of real-time systems

encompasses many disciplines:

a)

Applications

b)

Models and

Abstractions

c)

Optimization

Algorithms

d)

Networking

e)

Software Development

f)

Operating Systems

g)

System-level

Architecture

h)

Processors

There are separate courses for each of these

topics. I will assume that you have a basic (undergraduate level) understanding

of operating systems, programming languages, networking, algorithms, computer

systems and processor architectures. Furthermore, I will assume you have basic

training in mathematics, especially calculus and probability.

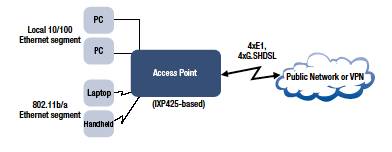

We will explore the issues in embedded system

design from computer systems architecture perspective. We will use multimedia (video)

streaming as the application to study embedded systems. Specifically we will

consider the design issues of an intelligent media gateway, which is

shown in the figure below where it is called an Access Point.

An intelligent media gateway is device

that connects a home or an office network to the Internet and provides a

variety of services to the end-users. We will focus on delivering streaming

media (video) to the laptops and handhelds efficiently by adapting the video

stream to the resource constraints of the client device and the local network.

We will explore the tradeoffs between resource utilization at the receiver and

in the network and the resultant quality of the video streaming. We will use

the latest network processor for Intel and the associated development kit and

software to study the various aspects of embedded system design.

|

Instructor |

Dr. Venkatesh Akella, 2117 Kemper Hall |

|

Email and Office Hours |

Tuesday 5PM-6PM |

|

Classroom |

PHYGEO 130 |

|

Class Timing |

Tuesday-Thursday 9:00 – 10:20 AM |

Plan

for the quarter

As noted above, embedded

systems engineering is not a single subject but a discipline much like computer

engineering or structural engineering or RF/microwave or control engineering.

So, there is no single book or syllabus that covers the whole field. So, the

best way to proceed is to treat this as a team research project, where we will

learn by solving a real-world problem, taking all the related constraints into

account. So, you should pay

particular attention to the following:

- This is an advanced graduate course in computer engineering, which means

you should be really interested in this material to take this class.

- The course will be research oriented, which means you have to be a proactive

participant in the course and be prepared to explore new things on your

own and come up with creative solutions.

- There is no TA for this class, so don’t expect

any babysitting whatsoever. We will work as a team and learn from each

other.

- There will be no exams.

- Your grade will depend on the final research

paper, homework and class participation.

References

- http://scholar.google.com/

(Google research paper search engine)

- http://citeseer.nj.nec.com/

(You can find most computer science related papers here)

- http://ieeexplore.ieee.org/ (IEEE Online Journals and Conferences)

- http://gateway2.ovid.com/ (University of California, Online Databases)

- http://portal.acm.org/

(ACM Digital Library)

- http://ixp4xx-osdg.sourceforge.net/ (Project Related Information)

Project Related References - Application

(a) D. Wu, Yiwei Hou, H. J. Lee, T. Chiang, Y. Zhang

and Jonathan Chao On End-to-End Architecture For Transporting MPEG-4

Video Over the Internet,

IEEE Transactions on Circuits and

Systems for Video Technology, Sept. 2000.

A

Nice Overview of MPEG-4 Streaming Over the Internet

(b) B. Girod and N. Farber, Wireless Video, Chapter 12, Compressed Video over

Networks, Editors: M. T. Sun and A. Reibman, November, 1999

A

Nice Overview of Wireless Video

(c) B. Girod and M. Kalman, Y. J. Liang, and R. Zhang, Advances in Channel-Adaptive Video Streaming, ICIP 2002, Invited Paper

Overview

of channel adaptive streaming, Figure 1 has some architectures for a media

gateway that might be useful.

(d) Philip A. Chou and Z. Miao, Rate-Distortion Optimized Streaming of

Packetized Media, IEEE Transactions on Multimedia, 2001.

This

is the paper that introduced Rate-Distortion Optimized Packet Scheduling. This

is what you will try to implement.

(e) M. van der schaar and D. S. Turaga, Content-Based Cross-layer Packetization and Retransmission Strategies

for Wireless Multimedia Transmission, University

of California, Davis, 2005

This

is a paper on packet aggregation

Project Related References – Architecture and Hardware

(f) M. Venkatachalam, P. Chandra, and R. Yavatkar, A Highly Flexible, Distributed Multiprocessor

Architecture for Network Processing, Computer Networks, vol. 41, pages 563-586, 2003

This

paper described IXP2400 architecture and ATM Traffic Shaping and Voice Gateway

Application.

(g) A. N. SLOSS, D. SYMES and C. Wright, ARM SYSTEM DEVELOPER’S GUIDE, Designing and

Optimizing System Software,

Morgan Kauffman, 2004

This

is good textbook on ARM software development. Worth Buying

(h)Intel XScale Architecture Manual

The

definitive guide to Intel XScale Core

(i) Intel IXP425 Hardware Development Manual

The

definitive guide to the Intel IXP platform

(j) http://ixp4xx-osdg.sourceforge.net

One-stop

shop for Programming IXP425 Platform. Contains pointers to ARM simulators,

compilers, emulators and everything else that you might need.

Homework 1

- Read papers (a), (b), (c), (d), (e) and (f)

- Write a one-page summary for paper number (a),

(d), (e) and (f) paper.

- Due Thursday April 14, 2005

Project Milestone 1 (DEADLINE MAY 3, 2005)

- Demuxing the video/audio stream, extracting

the packet dependency graph and packet attributes

- Submit a short 3 page writeup including an

excerpt of the video trace data which should look like this:

-

Frame

Number, Deadline, FrameType, Qy Qu Qv

0 0.000000 I 6528 28.385500 34.609100 35.005299

3 0.100000 P 696 28.009600 34.429699 34.790401

1 0.033333 B 344 28.328400 34.446701 34.807499

2 0.066667 B 384 28.201599 34.259899 34.894501

6 0.200000 P 576 27.970100 34.294201 34.827499

4 0.133333 B 272 28.186501 34.501900 34.904999

5 0.166667 B 248 28.161800 34.233398 34.922401

9 0.300000 P 456 28.231100 34.664799 34.521400

7 0.233333 B 152 28.292101 34.688400 34.630699

8 0.266667 B 168 28.280899 34.439899 34.543301

12 0.400000 I 6440 28.352900 34.682499 34.896900

10 0.333333 B 1192 28.853600 34.680401 34.812500

11 0.366667 B 1040 28.718800 34.527500 35.125401

15 0.500000 P 912 30.606400 35.915401 36.275101

13 0.433333 B 560 29.374500 35.617298 35.939701

14 0.466667 B 616 30.734600 36.384602 36.354401

18 0.600000 P 200 30.917500 36.342701 36.143200

16 0.533333 B 80 30.885700 36.046299 36.339500

17 0.566667 B 80 31.162100 36.026199 36.058899

21 0.700000 P 264 30.790199 36.397598 36.180302

…..

Video Trace References

- Video Trace Data from Arizona State University

– http://trace.eas.asu.edu/

- Patrick Seeling, Martin

Reisslein, and Beshan Kulapala

Network

Performance Evaluation Using Frame Size and Quality Traces of Single-Layer

and Two-Layer Video: A Tutorial" IEEE Communications Surveys

and Tutorials Vol. 6, No. 2 Pages 58—78 Third Quarter 2004

- Traffic and Quality

Characterization of Scalable Encoded Video: A Large-Scale Trace-Based

Study, Part 1: Overview and Definitions

ARM/Xscale Simulation Tools

· Simple Scalar Website www.simplescalar.com

· Princeton

University ARM Architecture Simulator

Project Milestone 2 (Deadline May 10, 2005)

- PACKETIZER - Convert the video traces into packets and estimate the

distortion

- SIMPLE SCHEDULER - Implement

a simple EDF scheduler

- REPACKETIZER – Optimized Packetizer

Implement

them in C and estimate their performance using Simplescalar on the XScale

Processor

Project Milestone 3 (Deadline May XX, 2005)

- EXPLORE JOINT PACKETIZATION and SCHEDULING FOR

ENERGY and NETWORK BANDWIDTH OPTIMIZATION