**Other DRAM Architectures**

| DRAM Memory Latency & Bandwidth Milestone |      |              |                  |                  |               |              |

|-------------------------------------------|------|--------------|------------------|------------------|---------------|--------------|

|                                           | DRAM | Page<br>DRAM | FastPage<br>DRAM | FastPage<br>DRAM | Synch<br>DRAM | DDR<br>SDRAM |

| Module Width                              | 16b  | 16b          | 32b              | 64b              | 64b           | 64b          |

| Year                                      | 1980 | 1983         | 1986             | 1993             | 1997          | 2000         |

| Mb/chip                                   | 0.06 | 0.25         | 1                | 16               | 64            | 256          |

| Die size (mm <sup>2</sup> )               | 35   | 45           | 70               | 130              | 170           | 204          |

| Pins/chip                                 | 16   | 16           | 18               | 20               | 54            | 66           |

| BWidth (MB/s)                             | 13   | 40           | 160              | 267              | 640           | 1600         |

| Latency (nsec)                            | 225  | 170          | 125              | 75               | 62            | 52           |

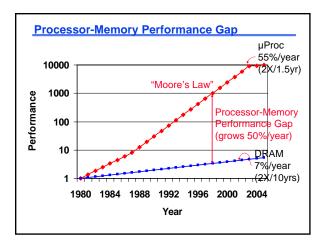

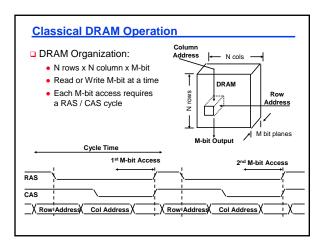

In the time that the memory to processor bandwidth

doubles the memory latency improves by a factor of only 1.2 to 1.4

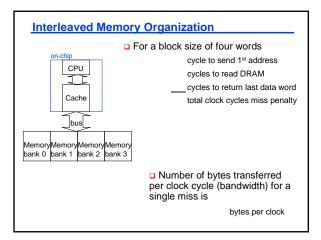

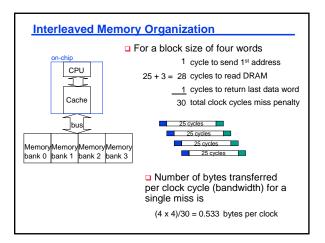

To deliver such high bandwidth, the internal DRAM is organized as interleaved memory banks

## DRAM Memory System Summary

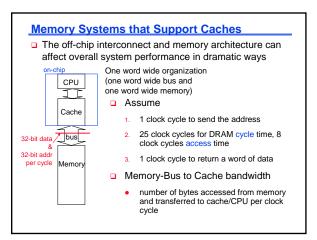

- Lts important to match the cache characteristics

- caches access one block at a time (usually more than one word)

- with the DRAM characteristics

- use DRAMs that support fast multiple word accesses, preferably ones that match the block size of the cache

- with the memory-bus characteristics

- make sure the memory-bus can support the DRAM access rates and patterns

- with the goal of increasing the Memory-Bus to Cache bandwidth