#### EEC170 Computer Architecture

### Lecture 2 Addressing Modes and MIPS ISA

October 10, 2005 Soheil Ghiasi Electrical and Computer Engineering University of California, Davis

Slides are online

- Password protected:

- ♦ Username: EEC289Q

- Password: FPGAsrcool!

- \* TA office hours are Mondays right after class

- ♦ M 4-6pm

### **Key Design Principles**

- 1. Simplicity favors regularity.

- 2. Smaller is faster.

- 3. Make the common case fast.

- 4. Good design demands good compromises.

# Recap: Basic ISA Classes

| 2 address             | add A B   | $mem[A] \leftarrow mem[A] + mem[B]$ |

|-----------------------|-----------|-------------------------------------|

| 3 address             | add A B C | $mem[A] \leftarrow mem[B] + mem[C]$ |

| Accumulator:          |           |                                     |

| 1 address             | add A     | $acc \leftarrow acc + mem[A]$       |

|                       | addx A    | $acc \leftarrow acc + mem[A + x]$   |

| Stack:                |           |                                     |

| ♦0 address            | add       | $tos \leftarrow tos + next$         |

| ♦ General Purpose Reg | gister:   |                                     |

| 2 address             | add A B   | $reg[A] \leftarrow reg[A] + reg[B]$ |

| 3 address             | add A B C | $reg[A] \leftarrow reg[B] + reg[C]$ |

Comparison:

Bytes per instruction? Number of Instructions? Cycles per instruction?

\* If performance is most important, use fixed length instructions

#### Data Addressing Modes

- \*Frequent: Displacement, Immediate, Register Indirect

- Displacement size should be 12 to 16 bits

- Immediate size should be 8 to 16 bits

#### Operand Sizes

Support these data sizes and types:

8-bit, 16-bit, 32-bit, 64-bit integers and

32-bit and 64-bit IEEE 754 floating point numbers

### **Addressing Modes**

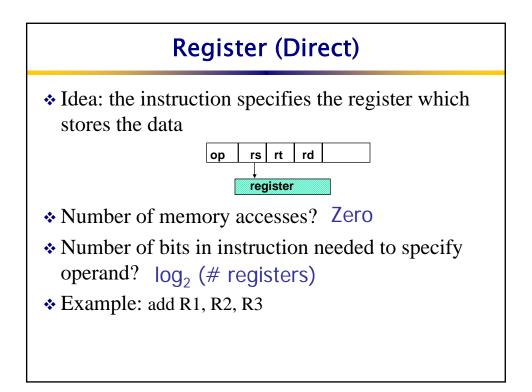

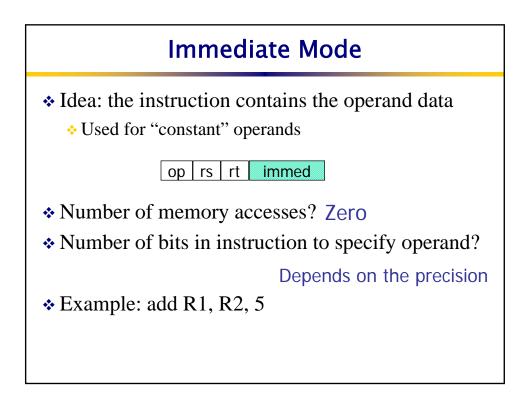

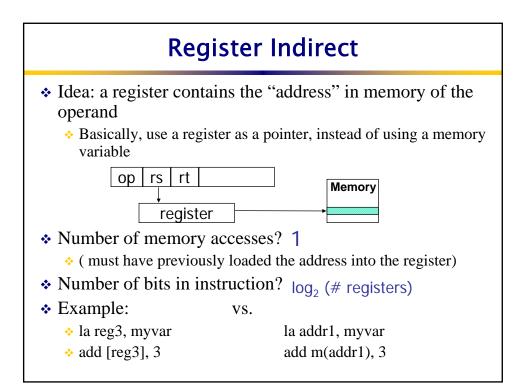

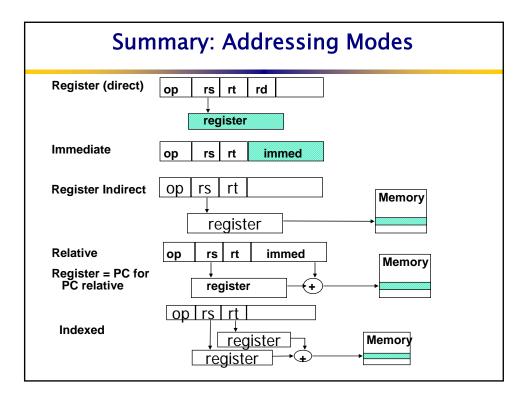

- How do we specify the location of the operands?

- Number of different possible Addressing Modes

- Register (direct)

- Immediate

- Register Indirect

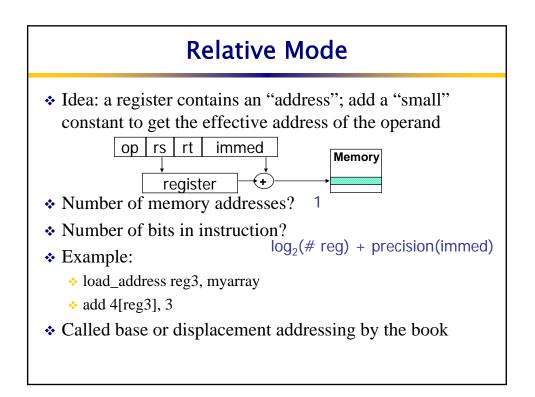

- Relative

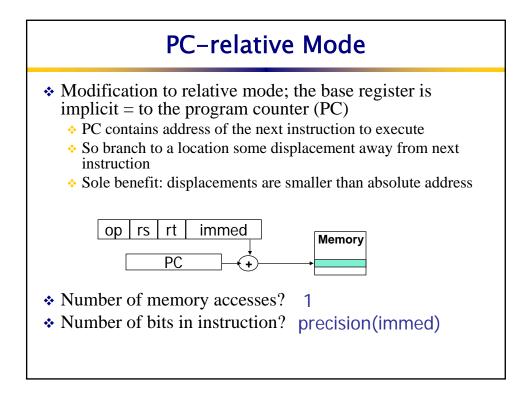

- PC relative

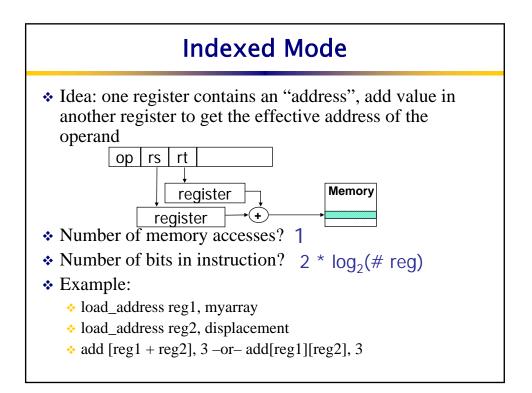

- Indexed

| MIPS logical instructions |                   |                               |                                |  |  |  |

|---------------------------|-------------------|-------------------------------|--------------------------------|--|--|--|

| Instruction               | Example           | Meaning                       | Comment                        |  |  |  |

| and                       | and \$1,\$2,\$3   | <b>\$1 = \$2 &amp; \$3</b>    | 3 reg. operands; Logical AND   |  |  |  |

| or                        | or \$1,\$2,\$3    | <b>\$1 = \$2   \$3</b>        | 3 reg. operands; Logical OR    |  |  |  |

| xor                       | xor \$1,\$2,\$3   | <b>\$1 = \$2 ^ \$3</b>        | 3 reg. operands; Logical XOR   |  |  |  |

| nor                       | nor \$1,\$2,\$3   | <b>\$1 = ~(\$2  \$3)</b>      | 3 reg. operands; Logical NOR   |  |  |  |

| and immediate             | andi \$1,\$2,10   | <b>\$1 = \$2 &amp; 10</b>     | Logical AND reg, constant      |  |  |  |

| or immediate              | ori \$1,\$2,10    | 1 = 2   10                    | Logical OR reg, constant       |  |  |  |

| xor immediate             | xori \$1, \$2,10  | <b>\$1 = \$2 ^ 10</b>         | Logical XOR reg, constant      |  |  |  |

| shift left logical        | sll \$1,\$2,10    | <b>\$1 = \$2 &lt;&lt; 10</b>  | Shift left by constant         |  |  |  |

| shift right logical       | srl \$1,\$2,10    | <b>\$1 = \$2 &gt;&gt; 10</b>  | Shift right by constant        |  |  |  |

| shift right arithm.       | sra \$1,\$2,10    | <b>\$1 = \$2 &gt;&gt; 10</b>  | Shift right (sign extend)      |  |  |  |

| shift left logical        | sllv \$1,\$2,\$3  | <b>\$1 = \$2 &lt;&lt; \$3</b> | Shift left by variable         |  |  |  |

| shift right logical       | srlv \$1,\$2, \$3 | <b>\$1 = \$2 &gt;&gt; \$3</b> | Shift right by variable        |  |  |  |

| shift right arithm.       | srav \$1,\$2, \$3 | <b>\$1 = \$2 &gt;&gt; \$3</b> | Shift right arith. by variable |  |  |  |

| <b>MIPS</b> Reference Data: CORE INSTRUCTION SET |                                                                                                                                                                                                                                   |             |                                      |                           |  |  |  |  |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------------|---------------------------|--|--|--|--|

| NAME                                             | MNE-<br>MON-<br>IC                                                                                                                                                                                                                | FOR-<br>MAT | OPERATION (in<br>Verilog)            | OPCODE<br>/FUNCT<br>(hex) |  |  |  |  |

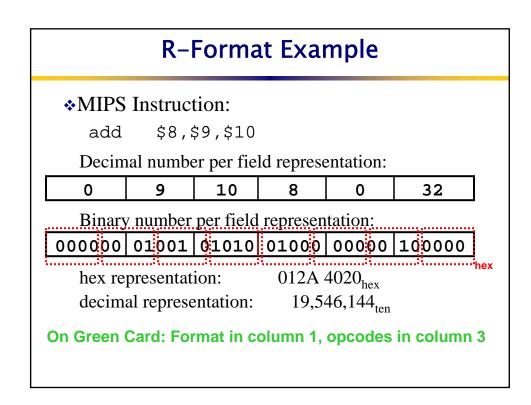

| Add                                              | add                                                                                                                                                                                                                               | R           | R[rd] = R[rs] + R[rt] (1)            | 0 / 20 <sub>hex</sub>     |  |  |  |  |

| Add<br>Immediate                                 | addi                                                                                                                                                                                                                              | I           | R[rt] = R[rs] +<br>SignExtImm (1)(2) | 8 <sub>hex</sub>          |  |  |  |  |

| Branch On<br>Equal                               |                                                                                                                                                                                                                                   |             |                                      |                           |  |  |  |  |

| (2)<br>(3)                                       | <ul> <li>(1) May cause overflow exception</li> <li>(2) SignExtImm = { 16{immediate[15]}, immediate }</li> <li>(3) ZeroExtImm = { 16{1b'0}, immediate }</li> <li>(4) BranchAddr = { 14{immediate[15]}, immediate, 2'b0}</li> </ul> |             |                                      |                           |  |  |  |  |

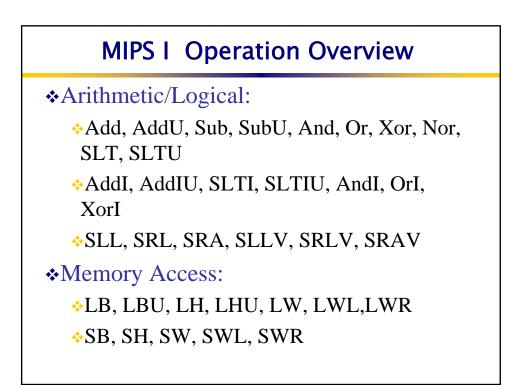

### **MIPS** arithmetic instructions

| Instruction       | Example           | Meaning            | Comments                                       |

|-------------------|-------------------|--------------------|------------------------------------------------|

| add               | add \$1,\$2,\$3   | 1 = 2 + 3          | 3 operands; exception possible                 |

| subtract          | sub \$1,\$2,\$3   | 1 = 2 - 3          | 3 operands; exception possible                 |

| add immediate     | addi \$1,\$2,100  | 1 = 2 + 100        | + constant; exception possible                 |

| add unsigned      | addu \$1,\$2,\$3  | 1 = 2 + 3          | 3 operands; no exceptions                      |

| subtract unsigned | subu \$1,\$2,\$3  | 1 = 2 - 3          | 3 operands; <u>no exceptions</u>               |

| add imm. unsign.  | addiu \$1,\$2,100 | 1 = 2 + 100        | + constant; <u>no exceptions</u>               |

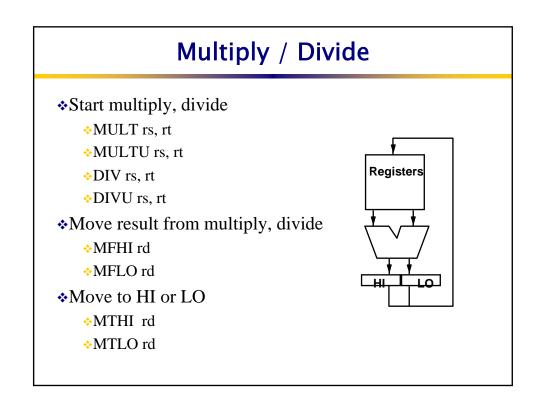

| multiply          | mult \$2,\$3      | Hi, Lo = \$2 x \$3 | 64-bit signed product                          |

| multiply unsigned | multu\$2,\$3      | Hi, Lo = \$2 x \$3 | 64-bit unsigned product                        |

| divide            | div \$2,\$3       | $Lo = $2 \div $3,$ | Lo = quotient, Hi = remainder Hi = \$2 mod \$3 |

| divide unsigned   | divu \$2,\$3      | $Lo = $2 \div $3,$ | Unsigned quotient & remainder Hi = \$2 mod \$3 |

| Move from Hi      | mfhi \$1          | 1 = Hi             | Used to get copy of Hi                         |

| Move from Lo      | mflo \$1          | 1 = Lo             | Used to get copy of Lo                         |

#### Q: Which add for address arithmetic? Which add for integers?

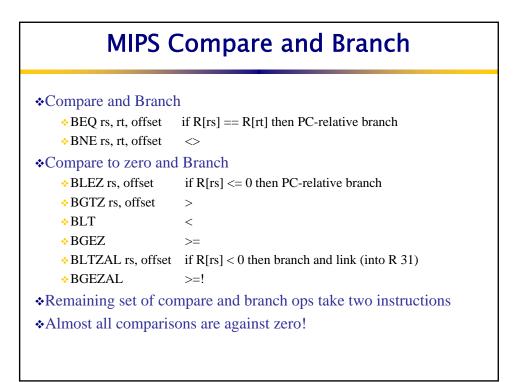

| MIPS jump,          | branch            | , compare instruction               |

|---------------------|-------------------|-------------------------------------|

| Instruction         | Example           | <u>Meaning</u>                      |

| branch on equal     | beq \$1,\$2,100   | if (\$1 == \$2) go to PC+4+100      |

|                     |                   | Equal test; PC relative branch      |

| branch on not eq.   | bne \$1,\$2,100   | if (\$1!= \$2) go to PC+4+100       |

|                     |                   | Not equal test; PC relative         |

| set on less than    | slt \$1,\$2,\$3   | if (\$2 < \$3) \$1=1; else \$1=0    |

|                     |                   | Compare less than; 2's comp.        |

| set less than imm.  | slti \$1,\$2,100  | if (\$2 < 100) \$1=1; else \$1=0    |

|                     |                   | Compare < constant; 2's comp.       |

| set less than uns.  | sltu \$1,\$2,\$3  | if (\$2 < \$3) \$1=1; else \$1=0    |

|                     |                   | Compare less than; natural numbers  |

| set l. t. imm. uns. | sltiu \$1,\$2,100 | if (\$2 < 100) \$1=1; else \$1=0    |

|                     |                   | Compare < constant; natural numbers |

| jump                | j 10000           | go to 10000                         |

|                     | ·                 | Jump to target address              |

| jump register       | jr \$31           | go to \$31                          |

|                     |                   | For switch, procedure return        |

| jump and link       | jal 10000         | \$31 = PC + 4; go to 10000          |

|                     |                   | For procedure call                  |

|                     |                   | For procedure call                  |

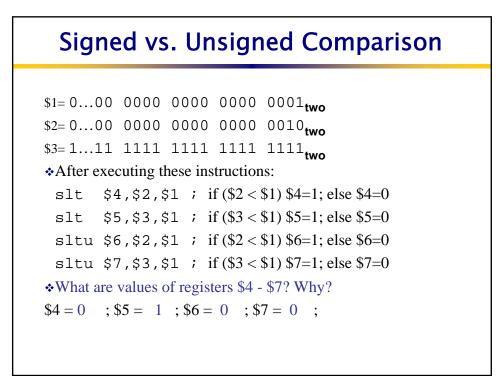

#### Signed vs. Unsigned Comparison

| Name        | Number | Usage                                           | Preserved across a call? |

|-------------|--------|-------------------------------------------------|--------------------------|

| \$zero      | 0      | the value 0                                     | n/a                      |

| \$v0-\$v1   | 2-3    | return values                                   | no                       |

| \$a0-\$a3   | 4-7    | arguments                                       | no                       |

| \$t0-\$t7   | 8-15   | temporaries                                     | no                       |

| \$s0-\$s7   | 16-23  | saved                                           | yes                      |

| \$t18-\$t19 | 24-25  | temporaries                                     | no                       |

| \$sp        | 29     | stack pointer                                   | yes                      |

| \$ra        | 31     | return address                                  | yes                      |

|             |        | ' <mark>callee saved''</mark><br>I in Column #2 |                          |

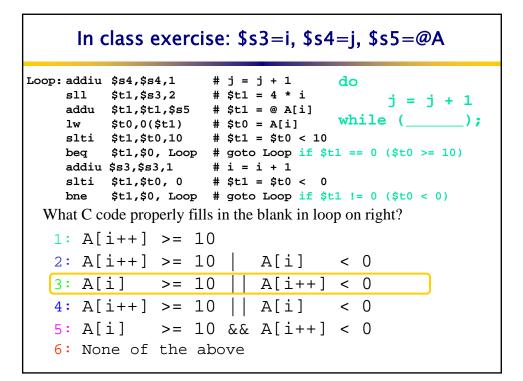

| Loop: addiu \$\$4,\$\$4,1  # j = j + 1 do<br>sll \$t1,\$\$3,2  # \$t1 = 4 * i<br>addu \$t1,\$t1,\$\$5  # \$t1 = @ A[i] j = j + 1<br>lw \$t0,0(\$t1)  # \$t0 = A[i] while ();<br>slti \$t1,\$t0,10  # \$t1 = \$t0 < 10<br>beq \$t1,\$0, Loop # goto Loop<br>addiu \$\$3,\$\$3,1  # i = i + 1<br>slti \$t1,\$t0, 0  # \$t1 = \$t0 < 0<br>bne \$t1,\$0, Loop # goto Loop<br>What C code properly fills in the blank in loop on right? |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>1: A[i++] &gt;= 10<br/>2: A[i++] &gt;= 10   A[i] &lt; 0<br/>3: A[i] &gt;= 10    A[i++] &lt; 0<br/>4: A[i++] &gt;= 10    A[i] &lt; 0<br/>5: A[i] &gt;= 10 &amp;&amp; A[i++] &lt; 0<br/>6: None of the above</pre>                                                                                                                                                                                                              |

| Gree                                                                               | Green Card: OPCODES, BASE CONVERSION, ASCII (3)                                                                                                                                                                                                                                                                                                                                                                                 |                            |         |              |                       |       |  |  |  |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------|--------------|-----------------------|-------|--|--|--|

| MIPS<br>opcode<br>(31:26)                                                          | (1)<br>MIPS<br>funct<br>(5:0)                                                                                                                                                                                                                                                                                                                                                                                                   | (2) MIPS<br>funct<br>(5:0) | Binary  | Deci<br>-mal | Hexa-<br>deci-<br>mal | ASCII |  |  |  |

| (1)                                                                                | sll                                                                                                                                                                                                                                                                                                                                                                                                                             | add.f                      | 00 0000 | 0            | 0                     | NUL   |  |  |  |

| j                                                                                  | srl                                                                                                                                                                                                                                                                                                                                                                                                                             | mul. <i>f</i>              | 00 0010 | 2            | 2                     | STX   |  |  |  |

| Iui         sync         floor.w.f         00 1111         15         f         SI |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |         |              |                       |       |  |  |  |

| lbu and cvt.w.f 10 0100 36 24 \$                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |         |              |                       |       |  |  |  |

| (2)                                                                                | Ibu         and         cvt.w.f         10 0100         36         24         \$           (1) opcode(31:26) == 0         (2) opcode(31:26) == 17 ten (11 hex );         if fmt(25:21)==16 ten (10 hex ) f = s (single);         if fmt(25:21)==16 ten (10 hex ) f = s (single);         if fmt(25:21)==17 ten (11 hex ) f = d (double)           Note: 3-in-1 - Opcodes, base conversion, ASCII!         S         S         S |                            |         |              |                       |       |  |  |  |

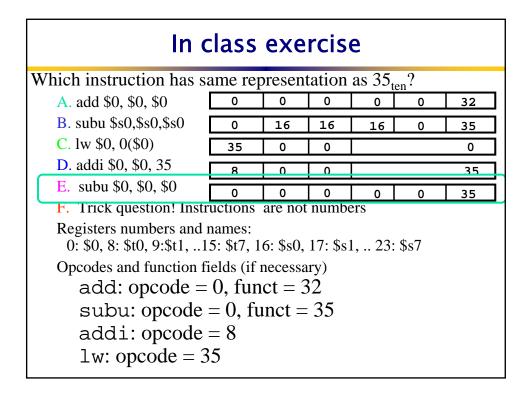

### In class exercise

Which instruction has same representation as  $35_{ten}$ ?

- A. add \$0, \$0, \$0

- B. subu \$\$0,\$\$0,\$\$0

- C. lw \$0, 0(\$0)

- **D**. addi \$0, \$0, 35

- E. subu \$0, \$0, \$0

- F. Trick question! Instructions are not numbers

✤Use Green Card handout to answer

| In class exercise                                                                              |                                             |        |        |        |        |       |  |

|------------------------------------------------------------------------------------------------|---------------------------------------------|--------|--------|--------|--------|-------|--|

| Which instruction has                                                                          | same rep                                    | resent | tation | as 35, | en?    |       |  |

| A. add \$0, \$0, \$0                                                                           | opcode                                      | rs     | rt     | rd     | shamt  | funct |  |

| B. subu \$s0,\$s0,\$s0                                                                         | opcode                                      | rs     | rt     | rd     | shamt  | funct |  |

| C. lw \$0, 0(\$0)                                                                              | opcode                                      | rs     | rt     |        | offset |       |  |

| <b>D</b> . addi \$0, \$0, 35                                                                   | D. addi \$0, \$0, 35 opcode rs rt immediate |        |        |        |        |       |  |

| E. subu \$0, \$0, \$0                                                                          | opcode                                      | rs     | rt     | rd     | shamt  | funct |  |

| F. Trick question! Instructions are not numbers                                                |                                             |        |        |        |        |       |  |

| Registers numbers and names:<br>0: \$0, 8: \$t0, 9:\$t1,15: \$t7, 16: \$s0, 17: \$s1, 23: \$s7 |                                             |        |        |        |        |       |  |

| Opcodes and function fields (if necessary)                                                     |                                             |        |        |        |        |       |  |

| add: opcode = 0, funct = $32$                                                                  |                                             |        |        |        |        |       |  |

| subu: $opcode = 0$ , funct = 35                                                                |                                             |        |        |        |        |       |  |

| addi: opcode                                                                                   | e = 8                                       |        |        |        |        |       |  |

| lw: opcode =                                                                                   | 35                                          |        |        |        |        |       |  |

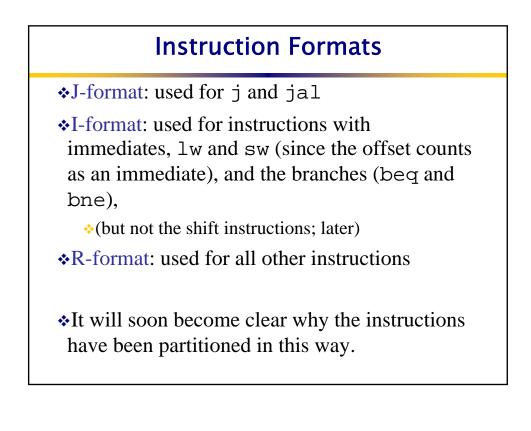

## Conclusion

Instruction Set Architecture is the key abstraction between hardware designer and software developers

Machine Organizations

Memory-to-Memory Machines

Accumulator

♦ Stack

General Purpose Register Machines

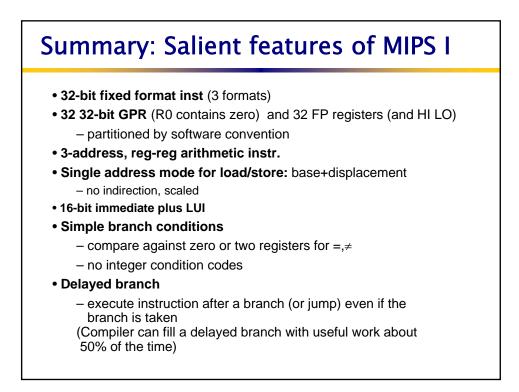

✤ MIPS ISA

- General Purpose Register, Load/Store Machine

- 32 registers, 32 bit operands, 32 bit main memory address space

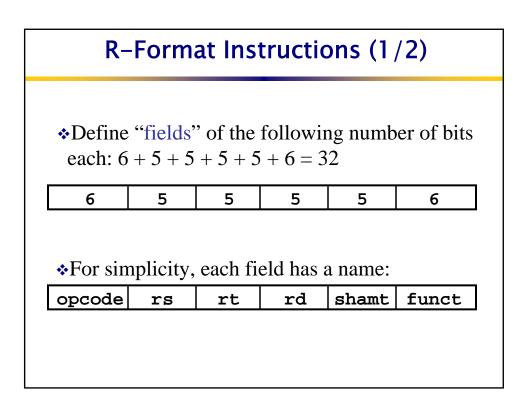

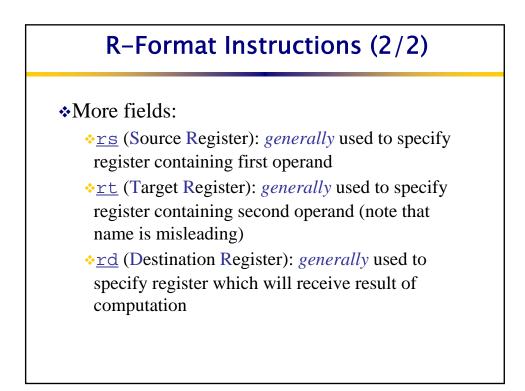

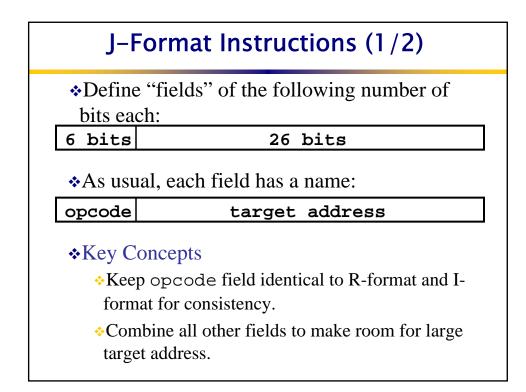

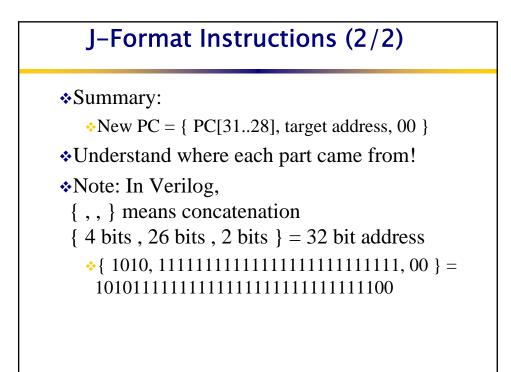

- 32 bit fixed length instructions R, I and J instruction formats