# EEC 118 Spring 2011 Midterm

Rajeevan Amirtharajah Dept. of Electrical and Computer Engineering University of California, Davis

#### May 2, 2011

This examination is closed book and closed notes. Some formulas which you may find useful are listed in the back of the exam. Calculators are allowed, however using the calculator's function memory to store course related material is NOT allowed and constitutes cheating on this exam.

For all problems, state any assumptions you make, show all work, and clearly mark your answers. Correct but unclear or ambiguous answers will not receive full credit.

Excerpts from the UC Davis Code of Academic Conduct state:

- 1. Each student should act with personal honesty at all times.

- 2. Each student should act with fairness to others in the class. This means, for example, that when taking an examination, students should not seek an unfair advantage over other classmates through cheating or other dishonest behavior.

- 3. Students should take group as well as individual responsibility for honorable behavior. This includes notifying the instructor or TA if you observe cheating.

I understand the honor code and agree to be bound by it. Signature: Solutions Name (printed): Lab Section:

#### Grading:

| Problem | Maximum | Score |

|---------|---------|-------|

| 1       | 15      |       |

| 2       | 9       |       |

| 3       | 28      |       |

| 4       | 11      |       |

| 5       | 12      |       |

| Total   | 75      |       |

#### 1 Transistor Biasing

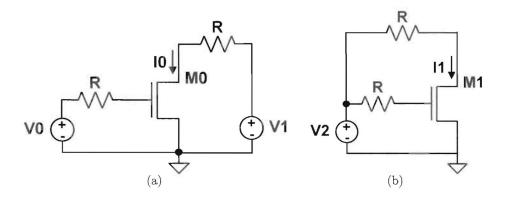

Figure 1: FET biasing circuits. (a) Two independent voltage sources. (b) One voltage source and two resistors.

**Problem 1.1** (10 points) Consider the NMOS bias circuit shown in Figure 1(a). Suppose we know that for the NMOS under bias,  $V_{T0,n} = 1.5$ V, W/L = 2/1,  $\gamma = 0.27$ V<sup>1/2</sup>,  $\lambda = 0$ V<sup>-1</sup>,  $\mu C_{ox} = 299 \ \mu \text{A/V}^2$ , and  $-2\Phi_F = 0.6$  V. Given that V0 = 5V and  $R = 50\Omega$ , find the following:

• The smallest voltage V1 such that transistor M0 is in saturation:  $V1 = 3.68 \sqrt{100}$

• The current 10 for the value of V1 you found: I0 = 3.66 mÅ  $N_{DS} = V1 = I0R V_{GS} = V0$  For saturation,  $V_{DS} \ge V_{GS} - V_{T,N} \Rightarrow V1 - I_0R \ge V0 - V_{T,N}$   $V_{BS} = OV \text{ (implicit)}$   $I_0 = I_{DS} = \frac{\mu C_{OX}}{2} \left(\frac{W}{L}\right) \left(V_0 - V_{T,N}\right)^2$   $= \frac{299 \mu A / N^2}{2} \left(\frac{2}{1}\right) \left(5V - 1.5V\right)^2 = 3.66 \text{ mÅ}$   $V1 \ge V0 - V_{T,N} + I_0R$   $\ge 5V - 1.5V + (3.66 \text{ mÅ})(50.52)$  $\ge 3.68 \text{ V}$  **Problem 1.2** (5 points) Consider the NMOS bias circuit shown in Figure 1(b). Assume transistor M1 has the same parameters as transistor M0 in Problem 1.1 except its W/L ratio is **unknown**. Given that when V2 = 3.3V and  $R = 500\Omega$ , the NMOS  $V_{DS} = V2/2$ , find W/L for M1.

$$V2 = 3.3V \qquad V_{DS} = \frac{V2}{2} = 1.65V \qquad V_{GS} = V2 \implies V_{GS} - V_{T,m} = V2 - V_{T,m} \qquad V_{BS} = \emptyset V \text{ (implicit)}$$

$$= 3.3V - 1.5V$$

$$= 1.8V$$

$$V_{GS} - V_{T,m} > V_{DS} \implies \underline{\text{(inear}}$$

$$T_{1} = \frac{V_{2} - V_{DS}}{R} = \frac{V_{2}}{2R} = 3.3 \text{ mA} = \mu_{n} \cos\left(\frac{W}{L}\right) \left[ (V_{GS} - V_{En}) V_{DS} - \frac{V_{DS}}{2} \right]$$

$$\Rightarrow \left(\frac{W}{L}\right) = \frac{3.3 \text{ mA}}{\frac{299 \mu A}{V^{2}} \left[ (3.3V - 1.5V) (1.65V) - \frac{(1.65V)^{2}}{2} \right]}$$

$$W = 6.86$$

# 2 Logic Gate

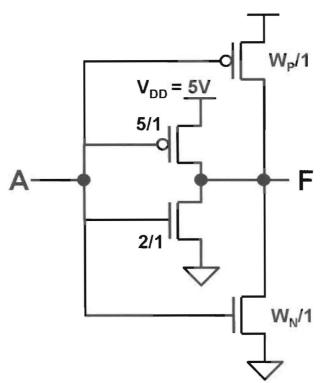

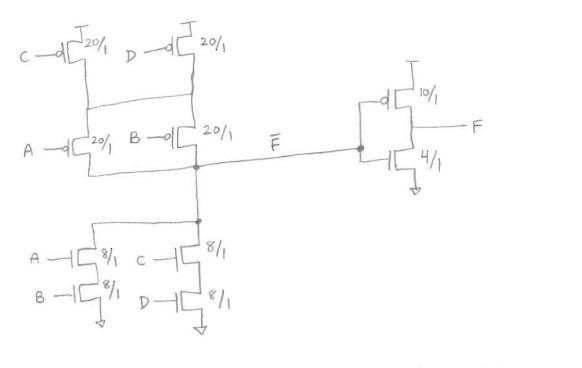

Figure 2 shows a circuit model for a one input CMOS logic gate. Assume all transistor W/L ratios are as shown in Figure 2 and the following transistor and supply voltage characteristics:  $V_{DD} = 5 \text{ V}$

$\begin{array}{ll} \nu_{DD} = 3 \ \mathrm{V} \\ \lambda_n = 0.02 \ \mathrm{V}^{-1} & \lambda_p = -0.02 \ \mathrm{V}^{-1} \\ V_{T0,n} = 0.8 \ \mathrm{V} & V_{T0,p} = -0.8 \ \mathrm{V} \\ \gamma_n = 0.33 \ \mathrm{V}^{1/2} & \gamma_p = 0.33 \ \mathrm{V}^{1/2} \\ \mu_n C_{ox} = 350 \times 10^{-6} \ \mathrm{A/V}^2 & \mu_p C_{ox} = 100 \times 10^{-6} \ \mathrm{A/V}^2 \\ W_{min} = 2 & L_{min} = 1 \end{array}$

Figure 2: Circuit schematic for a logic gate.

**Problem 2.1** (1 point) What Boolean logic function is implemented by the circuit in Figure 2?

Problem 2.2 (6 points) Find  $W_P$  and  $W_N$  such that the worst case rise and fall times of the circuit in Figure 2 are equal. Be sure to minimize the total transistor area. Justify your answers below.

•  $W_P = 9$ •  $W_N = \boxed{2}$

Need total PMOS width =  $\frac{K_n'}{K_p'} = \frac{350 \,\mu A/v^2}{100 \,\mu A/v^2} = 3.5 = \frac{5+W_p}{2+W_N}$

WN≥2, so choose WN=2 (min. area)

**Problem 2.3** (2 points) Given your sizes from Problem 2.2 above, what are  $V_{OH}$  and  $V_{OL}$ for the circuit in Figure 2? Justify your answers.

- Parallel transistors can be combined, so ckt is a •  $V_{OH} = V_{DD} = 5V$ CMOS inverter which has full output swing.

- · VOL = ØN (ground)

### 3 Static CMOS Logic Design

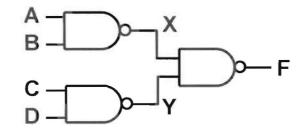

Figure 3: Logic gate network.

**Problem 3.1** (3 points) Write a Boolean expression for the logic function F in terms of inputs A, B, C, and D implemented by the logic gate network in Figure 3.

F = A . B + C . D

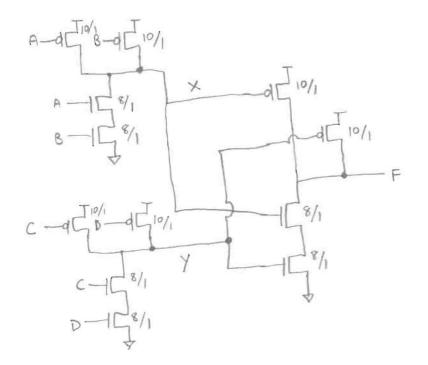

**Problem 3.2** (8 points) Implement the circuit in Figure 3 using static CMOS circuits for the <u>individual</u> logic gates. You will need at least three static CMOS gate circuits (some may be the same). Be sure to label all inputs, outputs, and other circuit nodes.

other solutions possible ...

**Problem 3.3** (4 points) Assume a minimum-sized inverter has PMOS ratio  $W_P/L = 10/1$  and NMOS ratio  $W_N/L = 4/1$ . Choose appropriate W/L ratios for the transistors in your circuit of Problem 3.2 such that the worst case rise and fall times are the same as a minimum-sized inverter. Indicate the sizes in your schematic above. Be sure to minimize the total area of the transistors.

**Problem 3.4** (7 points) Design a circuit that implements F which consists of a single multiple input CMOS logic gate and a static CMOS inverter.

other solutions possible

**Problem 3.5** (6 points) Choose appropriate W/L ratios for the transistors in your circuit of Problem 3.4 such that the worst case rise and fall times are the same as the minimum-sized inverter in Problem 3.3. Indicate the sizes in your schematic above. Be sure to minimize the total area of the transistors.

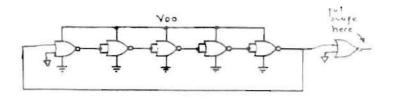

#### 4 Ring Oscillator

Figure 4: NOR gate ring oscillator.

**Problem 4.1** (4 points) For the ring oscillator circuit shown in Figure 4 from Lab 2, use the switch RC model and the following parameters for the equivalent inverters which model the NOR gates:  $R_p = 11k\Omega$ ,  $R_n = 10k\Omega$ , and  $C_L = 99$  fF ( $C_L$  is the load capacitance seen by each NOR gate). What frequency would be measured by the scope probe when placed as shown in the figure?

$$f = \frac{1}{T} = \frac{1}{N(t_{pLH} + t_{pHL})} = \frac{1}{5(0.69 R_p C_L + 0.69 R_n C_L)}$$

$$= \frac{1}{5(0.69 \cdot 11 K_s 2 \cdot 99 FF + 0.69 10 K_s 2 \cdot 99 FF)}$$

$$= \frac{1}{150.87 MHz} \qquad (139.4 MHz or other)$$

$$Values acceptable \rightarrow roundoff errors)$$

**Problem 4.2** (7 points) Suppose the equivalent inverter resistance for the NMOS devices  $(R_n = 10k\Omega)$  in the NOR gates was measured by averaging the resistance at the beginning and end of a **best case fall time** measurement. Find the W/L of the NMOS devices given  $V_{DD} = 5$  V,  $V_{T0,n} = 1.0$  V,  $\mu_n C_{ox} = 30 \times 10^{-6}$  A/V<sup>2</sup>,  $\gamma_n = 0.0$  V<sup>1/2</sup>,  $\lambda_n = 0.0$  V<sup>-1</sup>.

$$t_{f} = t_{2} - t_{1} \quad @t_{2} : V_{out} = 0.1 V_{DD} \\ @t_{1} : V_{out} = 0.9 V_{DD} \\ \end{bmatrix} V_{out} = V_{DS} \text{ for NOR gate equivalent} \\ \text{inverter.} \\ R_{n} = \frac{1}{2} \left( \frac{V_{DS} @t_{2}}{I_{0S} @t_{2}} + \frac{V_{0S} @t_{1}}{I_{0S} @t_{1}} \right) \\ @t_{1} : V_{0S} = 0.9 V_{DD} = 4.5V \ge V_{DD} - V_{T}\phi_{in} = 5 - 1V \\ @t_{1} : V_{0S} = 0.9 V_{DD} = 4.5V \ge V_{DD} - V_{T}\phi_{in} = 5 - 1V \\ = 4V \\ @t_{2} : V_{0S} = 0.1 V_{DD} = 0.5V \le V_{DD} - V_{T}\phi_{in} = 4V \\ @t_{2} : V_{0S} = 0.1 V_{DD} = 0.5V \le V_{DD} - V_{T}\phi_{in} = 4V \\ \end{bmatrix}$$

Problem 4.2 (cont.)

$$R_{n} = \frac{1}{2} \left[ \frac{0.1 V_{DD}}{\mu_{n} c_{ox} \left(2 \cdot \frac{W}{L}\right) \left[ \left(V_{DD} - V_{Td_{j}n}\right) 0.1 V_{DD} - \frac{\left(0.1 V_{DD}\right)^{2}}{2} \right]^{2} + \frac{0.9 V_{DD}}{\frac{\mu_{n} c_{ox}}{2} \left(2 \cdot \frac{W}{L}\right) \left(V_{00} - V_{Td_{j}n}\right)^{2}}{\frac{1}{2}} \right] \right]$$

$$\frac{1}{2} \left[ \frac{1}{1} \frac{1$$

Plugging in values and solving for W,

$$\frac{W}{L} = 1.16$$

or 1.31 if 20%-80% fall time assumed

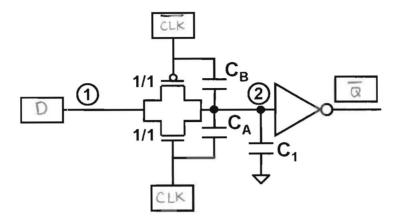

#### 5 Latch

Figure 5: Latch schematic.

**Problem 5.1** (4 points) For the latch circuit shown in Figure 5, label the boxes D, CLK,  $\overline{CLK}$ ,  $\overline{Q}$  such that the circuit works as a **positive transparent** inverting latch.

**Problem 5.2** (2 points) Is the circuit in Figure 5 a static or dynamic latch (circle one)? Justify your answer.

• Static

• Dynamic No positive feedback, logic level stored as capacitor charge.

**Problem 5.3** (6 points) Suppose the latch is used as the slave stage of an edge-triggered flip-flop and that node 1 and node 2 in Figure 5 are initially at 1.8V and 0V, respectively. Assuming  $R_p = 300\Omega$  for a PMOS device with W/L = 1/1 and  $R_n = 100\Omega$  for an NMOS device with W/L = 1/1,  $C_A = 19$ fF,  $C_B = 23$ fF,  $C_1 = 150$ fF, and  $t_{pHL}$  for the inverter is 8.9ps, estimate the clock-to-Q delay for the latch using the switch RC model for the transistors.

Problem 5.3 (cont.)

$$t_{c \rightarrow q} : \text{ when } CLk \text{ gors high, } D \text{ propagates } to \text{ output } \overline{Q}$$

$$c_{LK}$$

$$l_{RV}$$

$$f_{CR}$$

$$r_{CR}$$

# Miscellaneous Formulas

**MOSFET** Threshold Voltage

$$V_T = V_{T0} + \gamma \cdot \left(\sqrt{|-2\phi_F + V_{SB}|} - \sqrt{|2\phi_F|}\right)$$

$$\gamma = \frac{\sqrt{2q \cdot N_A \cdot \epsilon_{Si}}}{C_{ox}}$$

**CMOS** Inverter Switching Threshold

$$V_{TH} = \frac{V_{T0,n} + \sqrt{\frac{1}{k_R}} \cdot (V_{DD} - |V_{T0,p}|)}{\left(1 + \sqrt{\frac{1}{k_R}}\right)}$$

#### **CMOS Inverter Propagation Delay Times**

$$\tau_{PHL} = \frac{C_{load}}{k_n (V_{DD} - V_{T,n})} \left[ \frac{2V_{T,n}}{V_{DD} - V_{T,n}} + \ln\left(\frac{4(V_{DD} - V_{T,n})}{V_{DD}} - 1\right) \right]$$

$$\tau_{PLH} = \frac{C_{load}}{k_p (V_{DD} - |V_{T,p}|)} \left[ \frac{2|V_{T,p}|}{V_{DD} - |V_{T,p}|} + \ln\left(\frac{4(V_{DD} - |V_{T,p}|)}{V_{DD}} - 1\right) \right]$$

Switch Model Propagation Delay Times

$$t_{PHL} = 0.69R_nC_L$$

$$t_{PLH} = 0.69R_pC_L$$

$$t_f = 2.2R_nC_L$$

$$t_r = 2.2R_pC_L$$

**Junction Capacitances**

$$C_{j0} = \sqrt{\frac{\epsilon_{Si} \cdot q}{2} \left(\frac{N_A N_D}{N_A + N_D}\right) \frac{1}{\phi_0}}$$

$$C_j(V) = \frac{AC_{j0}}{\left(1 - \frac{V}{\phi_0}\right)^m}$$

$$C_{eq} = A C_{j0} K_{eq}$$