# EEC 118 Spring 2011 Final

Rajeevan Amirtharajah Dept. of Electrical and Computer Engineering University of California, Davis

June 6, 2011

This examination is closed book and closed notes. You are allowed one  $8.5 \times 11$  inch sheet (both sides) on which you may write formulas. Calculators are allowed, however using the calculator's function memory to store course related material is NOT allowed and constitutes cheating on this exam.

For all problems, state any assumptions you make, show all work, and clearly mark your answers. Correct but unclear or ambiguous answers will not receive full credit.

Excerpts from the UC Davis Code of Academic Conduct state:

- 1. Each student should act with personal honesty at all times.

- 2. Each student should act with fairness to others in the class. This means, for example, that when taking an examination, students should not seek an unfair advantage over other classmates through cheating or other dishonest behavior.

- 3. Students should take group as well as individual responsibility for honorable behavior. This includes notifying the instructor or TA if you observe cheating.

I understand the honor code and agree to be bound by it.

Signature: Name (printed): Solutions Lab Section:

Grading:

| Problem | Maximum | Score | Problem | Maximum | Score |

|---------|---------|-------|---------|---------|-------|

| 1       | 20      |       | 4       | 15      |       |

| 2       | 25      |       | 5       | 15      |       |

| 3       | 25      |       |         |         |       |

| Total   | 100     |       |         |         |       |

### **Device Parameters**

For all problems in this exam, assume we are using enhancement-type NMOS and PMOS transistors which have the characteristics shown in Table 1, unless otherwise specified. All dimensions are in microns. Also, assume **minimum** length devices unless otherwise specified.

| Parameter       | NMOS              | PMOS              |  |  |

|-----------------|-------------------|-------------------|--|--|

| VTO             | 0.8 V             | -0.8 V            |  |  |

| $\mu C_{ox}$    | $300 \ \mu A/V^2$ | $100 \ \mu A/V^2$ |  |  |

| $\gamma$        | $0 V^{1/2}$       | $0 V^{1/2}$       |  |  |

| Wmin            | $1.0\mu m$        | $1.0 \mu { m m}$  |  |  |

| $L_{min}$       | $1.0\mu m$        | $1.0 \mu { m m}$  |  |  |

| $\lambda$       | $0.0 V^{-1}$      | $0.0 V^{-1}$      |  |  |

| V <sub>DD</sub> | 5 V               |                   |  |  |

Table 1: Assumed Transistor Parameters.

| Capacitance/Width (fF/ $\mu$ m) | PMOS | NMOS |

|---------------------------------|------|------|

| $C_{gs}$                        | 1.5  | 1.4  |

| $C_{gd}$                        | 1.5  | 1.4  |

| $\tilde{C_{db}}$                | 1.0  | 0.9  |

| $C_{sb}$                        | 1.0  | 0.9  |

Table 2: PMOS and NMOS capacitances per unit width.

### 1 Transistor Current Biasing

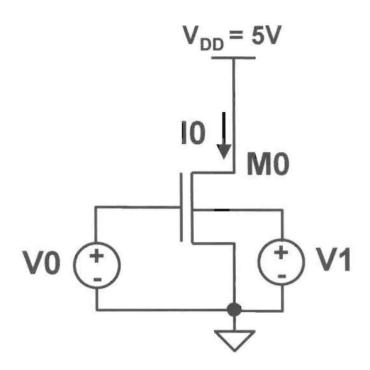

Figure 1: Voltage setup for NMOS biasing.

Assume that NMOS transistor M0 in Figure 1 has W/L = 4,  $\gamma = 0.33 V^{\frac{1}{2}}$ , and  $-2\Phi_F = 0.6V$  in the following problems.

**Problem 1.1** (5 points) Find the value of V1 which yields  $V_{Tn} = 1.1$  V.

$$V_{TN} = V_{TN0} + \sqrt[3]{\left(\sqrt{1-2}\phi_{E} + V_{SB}\right) - \sqrt{12}\phi_{E}I}} \qquad (2pts.)$$

$$1.1V = 0.8V + (0.33 V'^{12}) (\sqrt{10.6V} VII - \sqrt{0.6V}) \qquad (2pts.)$$

$$V_{1} = 2.235 V \qquad (1pt.)$$

$$V_{SB} = -V_{1}$$

Accepted - 2.235 V

as well

**Problem 1.2** (7 points) Given the value of V1 you found in Problem 1.1, fill in the table below for the different values of V0.

- $V0 = 0V, I0 = \phi A$

- V0 = 1.0V,  $I0 = \phi A$

- V0 = 4.0V, I0 = 5.04 mA

- V0 = 7.0V, I0 = 20.4 mA

$$V_{GS} = V\phi = \phi V \perp V_{T,n} = 1.1 V \quad cutoff \quad [I\phi = I_{PS} = \phi A] \quad (1pt.)$$

$$V_{GS} = V\phi = 1.0V \prec V_{T,n} = 1.1 V \quad cutoff \quad [I\phi = \phi A] \quad (1pt.)$$

$$V_{GS} = 4.0V, \quad V_{DS} = V_{DD} = 5V, \quad V_{GS} = V_{T,n} = 2.9V \quad \leq V_{DS} \implies saturation \quad (1pt.)$$

$$T\phi = \frac{\mu_{n} C_{ox}(\mu(V_{os} - V_{T,n})^{2} (1 + \frac{\lambda}{2} N_{os})}{2} = \frac{300 \mu A / V^{2}}{2} (\frac{4}{1}) (4.0V - 1.1V)^{2} (1 \text{ pts.})$$

$$V_{GS} = 7.0V$$

,  $V_{DS} = 5V$ ,  $V_{GS} - V_{T_{SN}} = 5.9V > V_{PS} \Rightarrow linear$  (1pt.)

$$Id = \mu_{n} C_{0X} \left(\frac{W}{L}\right) \left[2 \left(V_{0S} - V_{T,n}\right) V_{0S} - V_{0S}^{2}\right]$$

=  $\frac{300 \mu A/V^{2}}{2} \left(\frac{4}{L}\right) \left[2 \left(7.0V - 1.1V\right) (5V) - (5V)^{2}\right]$  (1p+.)

=  $\left[20 \mu_{0} - 0\right]$  (0.5 pt-)

$$= 20.4 \text{ mA}$$

**Problem 1.3 (5 points)** Assuming the value of V1 which you found in Problem 1.1, find the value of V0 which yields a current I0 = 1mA.

From Problem 1.2, need

$$V \neq = V_{GS} \angle 4.0V \Rightarrow \text{ sat}$$

(1pt.)

$1mA = \frac{\mu_n C_{oX}}{2} \left(\frac{W}{L}\right) \left(V \phi - V_{T,n}\right)^2$  (1pt.)

$V \phi = \sqrt{\frac{1mA}{(\frac{300 \mu A/V^2}{2})(\frac{\mu}{1})} + 1.1V$  (2pt.)

$V \phi = 2.39 V$  (1pt.)

**Problem 1.4 (3 points)** Suppose  $\lambda = 0.06 V^{-1}$  and that when  $V_{GS} < V_{Tn}$ , the NMOS drain current is:

$$I_{DS} = I_S e^{\frac{V_{GS} - V_{Tn}}{kT/q}} \left( 1 - e^{\frac{-V_{DS}}{kT/q}} \right) \left( 1 + \lambda V_{DS} \right) \tag{1}$$

where  $I_S = 4.85 \mu A$  and kT/q = 26 mV. Assuming V0 = 1.0 V and V1 which you found in Problem 1.1, what is the new value of I0 at this V0?

$$I\phi = I_{ps} = (4.85\mu A) e^{\frac{(1.0V - 1.1V)}{26mV}} (1 - e^{\frac{-5V}{26mV}}) (1 + 0.06V^{-1}(5V)) (2pts.)$$

$$= \boxed{95.7 \text{ hA}} (1pt.)$$

$$134.7 \text{ hA}$$

#### 2 Inverter Characteristics and Logical Effort

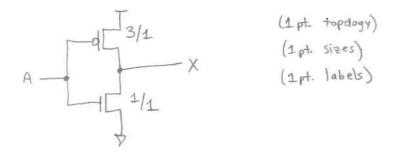

**Problem 2.1 (3 points)** Draw and label the schematic for a minimum-sized static CMOS inverter assuming the transistor parameters of Table 1. Size the circuit for an inverter switching threshold  $V_M = 0.5V_{DD}$ .

**Problem 2.2 (2 points)** Suppose the inverter you designed in Problem 2.1 drives a total capacitance of 45fF at 4.1GHz. How much power does it consume assuming  $V_{DD} = 5$ V?

$$P = C V_{DD}^{2} F \qquad (1pt.)$$

= (45 × 10<sup>-15</sup> F) (5 V)<sup>2</sup> (4.1 × 10<sup>9</sup> Hz) = [4.61 mW] (1pt.)

**Problem 2.3 (4 points)** Suppose the inverter you designed in Problem 2.1 drives an identical copy of itself. Using the capacitance values from Table 2, find the total load capacitance seen by the driver  $C_T = C_p + C_{in}$ , where  $C_p$  is the unloaded (intrinsic) output capacitance of the driver and  $C_{in}$  is the input capacitance of the receiver.

- $C_p = 15.7 \, \text{fF}$

- $C_{in} = 11.8 \text{ FF}$

- $C_T = 27.5 \, \text{fF}$

$$Cp = 2 - (1 \mu m) Cgdn + Cdbn + 2 \cdot (3 \mu m) Cgdp + Cdbp = 15.7 \text{ fF} (1pt.)$$

$$\widehat{T} \text{ Miller Effect (1pt.)}$$

$$Cin = 1 \mu m \cdot Cgdn + 1 \mu m \cdot Cgsn + 3 \mu m \cdot Cgdp + 3 \mu m \cdot Cgsp = 11.8 \text{ fF} (1pt.)$$

$$or$$

$$= 1 \mu m \cdot Cgsn + 3 \mu m \cdot Cgsp (acceptable if assume Miller effect on Toad inverter)$$

$$C_T = Cp + Cin = 27.5 \text{ fF} (1pt.)$$

**Problem 2.4 (6 points)** Find  $t_{pLH}$  for the inverter you designed in Problem 2.1 driving a total capacitance of  $C_T$  (from Problem 2.3). Assume an ideal step voltage on  $V_{in}$  and approximate the charging current by averaging the initial and final drain currents.

$$\begin{aligned} t_{pLH} &= \frac{C_T \Delta V}{I_{avg}} (I_{pt})^{C_T = 27.5 \text{ fF}} \quad \Delta N = 5V - 2.5V = 2.5V \quad (I_{pt}) \\ &= \frac{C_T \Delta V}{\frac{1}{2} \left[ \frac{\mu_p C_{ox}}{2} \left( \frac{W}{L} \right)_p \left( V_{GS,P} - V_{T,P} \right)^2 + \frac{\mu_p C_{ox}}{2} \left( \frac{W}{L} \right)_p \left[ 2 \left( V_{GS,P} - V_{T,P} \right) V_{DS,P} - V_{DS,P}^2 \right] \right]}{\frac{sat}{2} \left[ \frac{100 \mu A/V^2}{2} \left( \frac{3}{1} \right) \left( -5V - -0.8V \right)^2 + \frac{100 \mu A/V^2}{2} \left( \frac{3}{1} \right) \left[ 2 \left( -5V - -0.8V \right) \left( -2.5V \right) - \left( -2.5V \right)^2 \right]} \right]} \\ &= \left[ 28.3 \text{ ps} \right] (I_{P}t_{*}) \end{aligned}$$

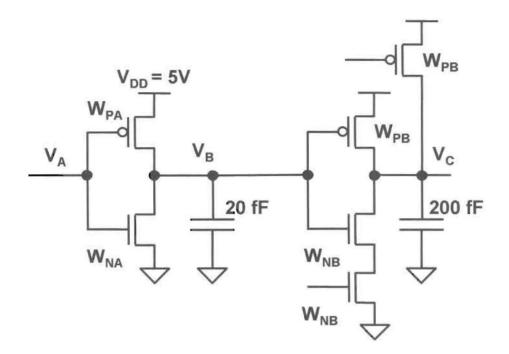

Figure 2: Cascaded inverter and NAND gate forming part of a logic network.

**Problem 2.5** (1 point) Figure 2 shows a CMOS inverter driving a 20fF wire load and a 2-input NAND gate driving a 200fF wire load. You will use the method of logical effort to minimize the delay of these gates by finding the optimal transistor widths. First, find the normalized parasitic delay  $p = C_p/C_{in}$  from the values you found above.

•

$$p = \frac{C_P}{C_{in}} = \frac{15.7 \, \text{fF}}{11.8 \, \text{fF}} = 1.33$$

**Problem 2.6** (5 points) Find the optimal transistor widths for the FETs in Figure 2 assuming each logic stage has an identical effort delay f = gh of 4.

- $W_{PA} = 5.25$

- $W_{NA} = 1.75$

- $W_{PB} = |5.9|$

- $W_{NB} = 5.3$

Logical effort of NAND2:  $g = \frac{Cin(NAND2)}{Cin(INV)} = \frac{3+2}{3+1} = \frac{5}{4}$  (1pt.)

Parasitic delay of NAND2:

$$P_{NAND2} = \frac{3+3+2}{3+1} P_{INV} = 2 \frac{CP}{CIM} = 2.66$$

Problem 2.6 (cont.)

Want

$$f = gh = 4$$

for NAND2  $\Rightarrow h = \frac{C_{out}}{C_{in}} = \frac{200 \, \text{FF}}{G_{in}} = \frac{f}{9} = \frac{4}{(5/4)} = \frac{16}{5}$  (lpt.)

$C_{in} = \frac{200 \, \text{FF}}{(16/5)} = 62.5 \, \text{FF}$ , Scale factor  $= \frac{62.5 \, \text{FF}}{C_{in} (inv)} = \frac{62.5 \, \text{FF}}{11.8 \, \text{FF}} = 5.3$  (lpt.)

$W_{rB} = 15.9$   $W_{NB} = 5.3$

for  $NNV \Rightarrow h = \frac{C_{out}}{C_{in}} = \frac{20 \, \text{FF} + 62.5 \, \text{FF}}{C_{in}} = \frac{f}{9} = \frac{4}{1}$  (lpt.)

$C_{in} = \frac{82.5 \, \text{FF}}{4} = 20.63 \, \text{FF}$ , Scale factor  $= \frac{20.63 \, \text{FF}}{C_{in} (inv)} = \frac{20.63 \, \text{FF}}{11.8 \, \text{FF}} = 1.75$  (lpt.)

$W_{PA} = 5.25$   $W_{NA} = 1.75$

**Problem 2.7** (4 points) Find the normalized path delay D and the absolute path delay  $D_{abs}$  assuming the sizes you found in Problem 2.6 and  $\tau = t_{pLH}$  you found in Problem 2.4.

•

$$D = \begin{bmatrix} 12 \\ \\ D_{abs} = \begin{bmatrix} 194 & ps \\ \\ P_{NB,NP2} = 2.66 & (see above) & (1pt.) \\ D = F + P = 2.4 + 2.66 + 1.33 = 11.99 \approx 12 & (2pts.) \\ D_{abs} = 12 & \tau = 12 \cdot 28.3 & ps = 193.75 & (1pts.) \end{bmatrix}$$

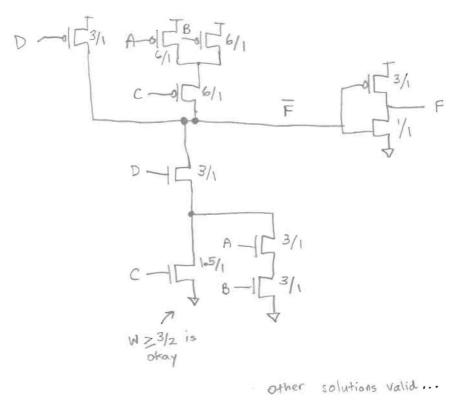

#### 3 Static CMOS, Dynamic Logic, and Pseudo NMOS

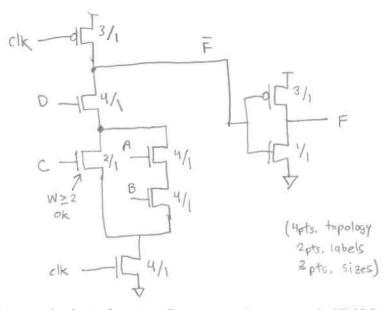

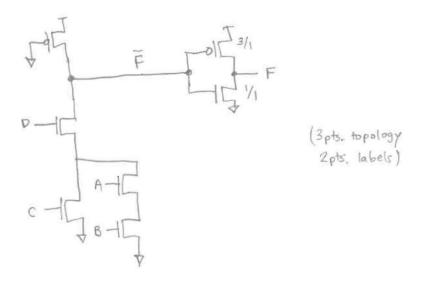

**Problem 3.1** (11 points) Implement the logic function F = ABD + CD using a 4-input static CMOS logic gate with a minimum number of transistors and a single minimum-sized inverter as designed in Problem 2.1. Size the 4-input gate such that the worst case rise and fall times at its output are equal to the minimum-sized inverter.

F= (AB + c)D

**Problem 3.2 (9 points)** Implement the logic function F using a 4-input dynamic logic gate and a single minimum-sized inverter as designed in Problem 2.1. Size the 4-input gate such that the worst case rise and fall times at the dynamic node are equal to the minimum-sized inverter.

**Problem 3.3** (5 points) Implement the logic function F using a 4-input pseudo-NMOS logic gate and a single minimum-sized inverter as designed in Problem 3.1. You do not have to size the transistors.

### 4 Sequential Element Design

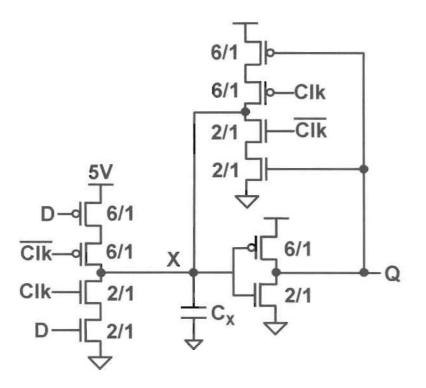

Figure 3: Transparent Latch.

Figure 3 shows a transparent latch circuit.

**Problem 4.1 (2 points)** Is this circuit a static or dynamic sequential element (circle one)? Justify your answer.

(1pt.) • Static Positive feedback (1pt.) • Dynamic

**Problem 4.2** (2 points) Is this latch transparent during the positive or negative phase of the clock (circle one)? Justify your answer.

**Problem 4.3 (10 points)** The delay through the latch is determined by the rise and fall times at internal node X. Suppose  $C_X = 25$  fF. Using the switch RC model for the transistors, calculate the rise and fall times of node X assuming simultaneous ideal steps on D and Clk or  $\overline{Clk}$  and that the initial resistance remains unchanged throughout the transition.

•

$$t_r = 104 \text{ ps}$$

•  $t_f = 104 \text{ ps}$

•  $t_f = 104 \text{ ps}$

$t_r = 1n(9)RC = 2.2RC \quad (1pt.)$

$R_{PMos} = \frac{|V_{DS}|}{I_{DS}p} = \frac{|OV - V_{DD}|}{\frac{\mu_P C_{DX}}{2} (\phi V - V_{DD} - V_{T_s}p)^2 (\frac{W}{L})} \quad (3 \text{ pts})$

$= \frac{5V}{\frac{100\mu A/v^2}{2} (\frac{6}{2}) (-5V - 0.8V)^2} = 1889.6 \Omega \quad (1pt.)$

$t_f = 2.2 (1.89kg) (25 \text{ fF})$

$= 103.8 \text{ ps} \quad (1pt.)$

t\_=tr since transistors are mobility-ratioed (3pts.)

**Problem 4.4** (1 point) Briefly describe a set of conditions on Clk and  $\overline{Clk}$  which could cause the latch to operate incorrectly.

cik, cik simultaneously high or low rise/fall times >> than tr, tf above

## 5 Eight Transistor Memory Cell

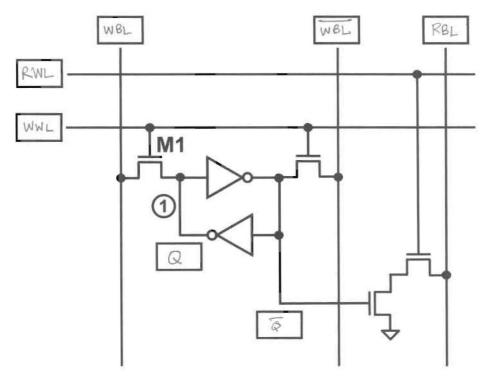

For this problem, assume the transistor characteristics as shown in Table 1 and all transistor widths and lengths are  $1\mu$ m, unless otherwise specified. Figure 4 shows an eight transistor memory cell. The inverters are CMOS inverters.

Figure 4: Eight transistor memory cell.

**Problem 5.1** (2 points) What type of memory cell is shown in Figure 4 (circle one)? Justify your answer.

**Problem 5.2** (4 points) Label Figure 4 to clearly indicate the storage (data) node Q, the write word line WWL, the read word line RWL, the write bit line WBL, and the read bit line RBL. Also label the complements of any signals if necessary.

15

**Problem 5.3** (4 points) Assume Node 1 is a storage node and NMOS M1 connects to a bidirectional bit line. If Node 1 stores a logic '0' and the bit line is held at  $V_{DD}$ , write an equation which can be solved for the voltage  $V_1$  at Node 1. State any reasonable assumptions you make. Simplify the equation but you do not need to solve for  $V_1$ .

$$V_{DD} = V_{1} \angle V_{DD} - V_{T,T} \implies M_{2} \implies M_{2} \implies Since V_{GS} = V_{DD}, V_{DS} = V_{1} (lpt.)$$

$$M_{1} = V_{DD} - V_{1} \implies Sa^{+} (lpt.)$$

$$V_{DD} = V_{1} + V_{DD}$$

$$I_{1} = V_{DD} - V_{1} \implies Sa^{+} (lpt.)$$

$$I_{DS} = I_{DS2}$$

$$M_{2} = M_{2} C_{0X} \left(\frac{1}{1}\right) \left(V_{DD} - V_{1} - V_{T,T}\right)^{2} = M_{2} C_{0X} \left(\frac{1}{1}\right) \left[2 \left(V_{DD} - V_{T,T}\right)V_{1} - V_{1}^{2}\right]$$

$$\left[\left(V_{DD} - V_{1} - V_{T,T}\right)^{2} = 2 \left(V_{DD} - V_{T,T}\right)V_{1} - V_{1}^{2}\right] (2pts)$$

**Problem 5.4** (4 points) Under the same assumptions as in Problem 5.3, if Node 1 stores a logic '1' and the bit line is held at 0V, write an equation which can be solved for the voltage  $V_1$  at Node 1. State any reasonable assumptions you make. Simplify the equation but you do not need to solve for  $V_1$ .

$$\frac{\mu_{n} \cos \left(\frac{1}{i}\right) \left(V_{bp} - V_{\tau,n}\right)^{2}}{2} = \frac{\mu_{p} \cos \left(\frac{1}{i}\right) \left[2 \left(-V_{bp} - V_{\tau,p}\right) \left(V_{l} - V_{pp}\right) - \left(V_{l} - V_{pp}\right)^{2}\right]}{2} \left(2 \text{ pts.}\right)$$

**Problem 5.5** (1 point) What is the principal advantage of the memory cell shown in Figure 4 over a conventional six transistor SRAM cell?

Decouples transistor sizing for writes from sizing for reads.