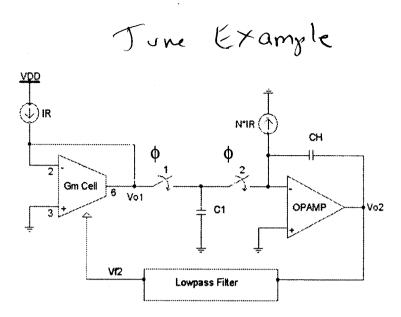

Fig. 4. Simplified Tuning Loop.

The reference tuning loop uses a Gm cell in feedback as shown in simplified form in Fig. 4 [4]. A constant current  $I_R$  is pushed into the Gm cell, producing a voltage  $V_{ol} = I_R/g_m$ .  $\phi_1$  and  $\phi_2$  are two non-overlapping clocks with frequency  $f_{clock}$ . During  $\phi_1$ , the capacitor  $C_1$  is charged to  $V_{ol}$ . During  $\phi_2$ , the charge on  $C_1$  is transferred to capacitor  $C_H$ . Also, a constant current  $NI_R$  is drawn from  $C_H$ . The average value of the opamp output,  $V_{I2}$ , is used to tune the

transconductance of the Gm cell.

When the loop reaches steady state, the charge injected onto  $C_H$  by  $C_1$  during  $\phi_2$  equals the charge removed from  $C_H$  by  $NI_R$  in one clock period. Therefore  $V_{02}$  is periodic and  $V_{J2}$  is constant. In steady state,

$$= C_1 V_{o1} = N I_R T , = \mathbf{Q} \mathbf{I} \mathbf{R}$$

(2)

where  $T = 1/f_{clock}$  is the clock period. Substituting  $V_{ol} = I_R/g_m$  into (2) and simplifying gives

$$\frac{C_1}{g_m} = NT = \frac{N}{f_{clock}} , \qquad (3)$$

where  $g_m$  is the transconductance of the Gm cell. Hence,  $C_1/g_m$  depends on the clock frequency  $f_{clock}$ , which is derived from a crystal oscillator, and N, the ratio of DC currents that can be accurately defined in a CMOS process.

A more detailed block diagram of the tuning loop is shown in Fig. 5. The clock frequency is 6.25MHz and the DC current ratio N is 0.2. Using these values in (3),  $C_1/g_m = 32$ ns. If  $C_1$  has the same nominal value as  $C_f (=0.6 \text{pF})$  in the AC coupler, then  $g_m = 18.8 \mu\text{A/V}$ . With  $I_R \le 5 \mu\text{A}$  in Fig. 5, the nominal differential output voltage of the Gm cell is  $\le 0.53 \text{V}$ . To have a large  $g_m$  tuning range, the Gm cell should allow an output swing of >1.0V.

$$V_{oi} = \frac{IR}{Gm}$$

(1)

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 27, NO. 12, DECEMBER 1992