# 7 SDRAM\_CONTROL\_4PORT Module

## 7.1 Description

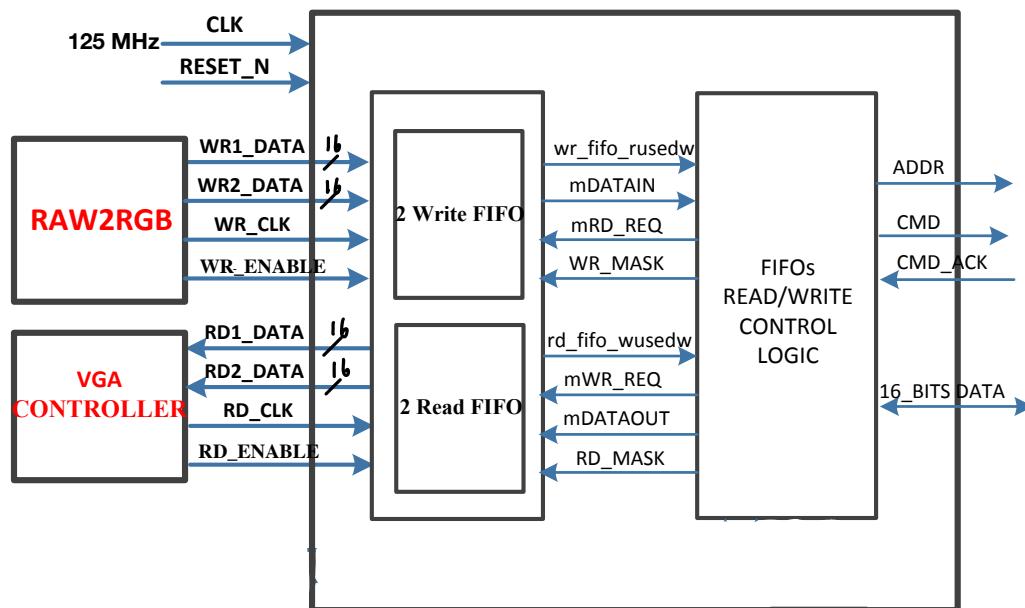

IS42R16320D SDRAM is used to store image data. Data source (RAW2RGB module) and data consumer (VGA CONTROLLER module) communicate to SDRAM by SDRAM\_CONTROL\_4PORT module. This module contains a SDRAM controller. The 16-bit SDRAM data port is regarded as 4 virtual data ports (2 read, 2 write). The 30-bit input RBD data is buffered in two 16-bit-width write FIFOs which write data to SDRAM. In the meanwhile, to meet the read request of the data consumer (VGA CONTROLLER module), the RGB data stored in SDRAM previously is read out and buffered in two 16-bit-width read FIFOs. This module forms a complete frame buffer.

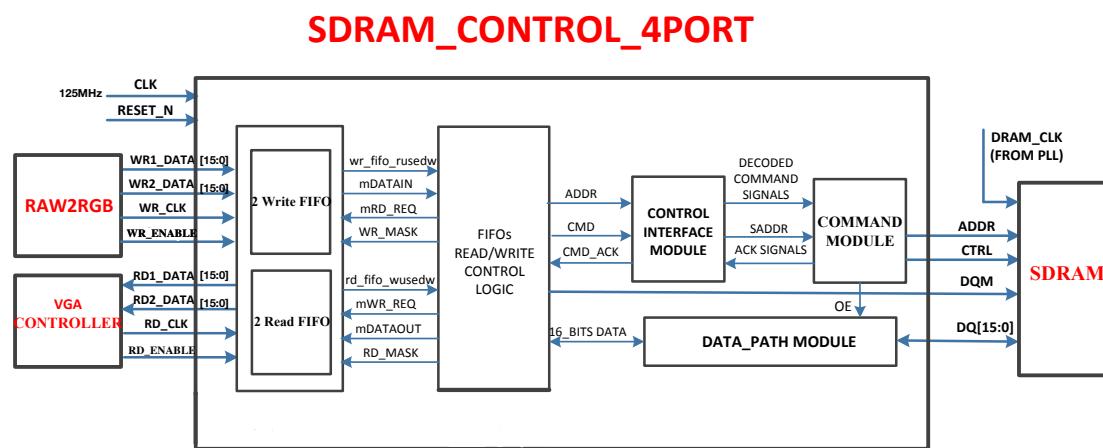

The structure of SDRAM\_CONTROL\_4PORT module is demonstrated below.

Figure 7-1 SDRAM\_CONTROL\_4PORT Module Structure

### 7.1.1 Data Flow

RGB format image data from RAW2RGB module is written to two write FIFOs in SDRAM\_CONTROL module continuously. VGA CONTROLLER reads data from two read FIFOs continuously. The FIFOs READ/WRITE CONTROL LOGIC generates read/write request and address to the CONTROL INTERFACE sub module according to the state of four FIFOs. The CONTROL INTERFACE sub module handles not only the read/write request from FIFOs READ/WRITE CONTROL LOGIC, but also initial request or refresh request generated by its internal timer according to SDRAM timing sequence. The CONTROL INTERFACE sub module sends decoded command signals to the COMMAND sub module and command acknowledge signal to FIFOs READ/WRITE CONTROL LOGIC. The COMMAND module uses decoded command signals to generate operations conforming to SDRAM protocol and control the signals output to SDRAM. Controlled by OE signal generated by COMMAND sub module, the DATA\_PATH sub module controls the direction of data line to make it simultaneous to the corresponding operations to SDRAM.

## 7.1.2 Using Four FIFOs

The input data is from RAW2RGB module and the output data is transferred to VGA CONTROLLER module. This means the read/write operations between external modules and SDRAM\_CONTROL\_4PORT module need high continuity but comparatively low speed. On the other hand, the read/write between SDRAM\_CONTROL\_4PORT module and SDRAM do not need continuity, and the speed is high. For the reasons above, asynchronous dual clock FIFOs are needed as input/output buffer. The data width of FIFOs is 16 bit, and the depth should be larger than one read/write burst length.

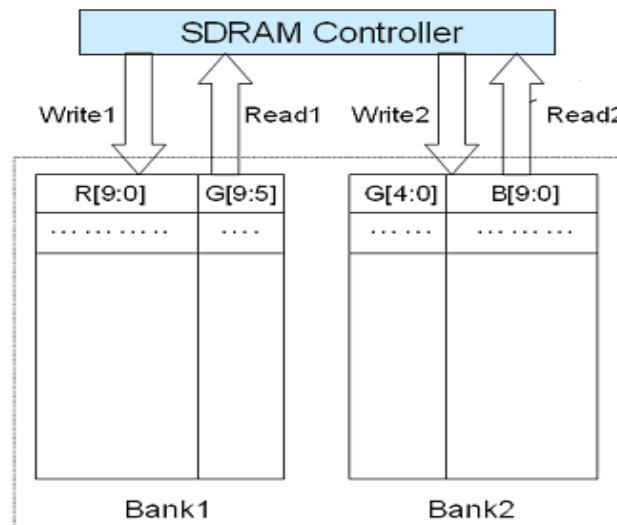

IS42R16320D SDRAM is used to store data. It has 4 banks, the data width of which is 16 bit. Since 30-bit data is needed for one pixel (R,G,B each need 10-bit data), the data of one pixel can't be write to/read from SDRAM in one operation. Also the 30-bit data can't share the same column/row address if it is stored in one bank of SDRAM, because the data width is only 16.

For convenience, we use two banks of SDRAM to store data of each pixel, as is demonstrated in the figure below. In this way, we build 4 virtual data ports for the 16-bit SDRAM data port (2 read, 2 write). We split the data of one pixel into two parts and store them in two banks separately, which means they can have the same column/row address. When the pixel data needs to be read out, these two parts are combined together to form a complete RGB-data.

Besides, to enhance the read/write speed, Full-Page Burst Mode is used in read/write transactions. For detail about Full-Page Burst Mode, please refer to [Chapter 7.3.2](#)

Figure 7-2 Four Port FIFOs Structure

## 7.2 Interface

| Port                  | Direction        | Width        | Description                               |

|-----------------------|------------------|--------------|-------------------------------------------|

| <b>CLK</b>            | Input            | 1            | Module clock                              |

| <b>RESET_N</b>        | Input            | 1            | Module reset<br>active low, asynchronous  |

| <b>WR1_DATA</b>       | Input            | `DSIZE       | Write FIFO 1 Input data                   |

| <b>WR_ENABLE</b>      | Input            | 1            | Write request to Write FIFO 1             |

| <b>WR1_ADDR</b>       | Input            | `ASIZE       | Write start address of Write FIFO 1       |

| <b>WR1_MAX_ADDR</b>   | Input            | `ASIZE       | Write max address of Write FIFO 1         |

| <b>WR1_LENGTH</b>     | Input            | 9            | Write length of Write FIFO 1              |

| <b>WR1_LOAD</b>       | Input            | 1            | Write register load input of Write FIFO 1 |

| <b>WR1_CLK</b>        | Input            | 1            | Write clock of Write FIFO 1               |

| <b>WR2_DATA</b>       | Input            | `DSIZE       | Write FIFO 1 Input data                   |

| <del><b>WR2</b></del> | <del>Input</del> | <del>1</del> | <del>Write request to Write FIFO 2</del>  |

| <b>WR2_ADDR</b>       | Input            | `ASIZE       | Write start address of Write FIFO 2       |

| <b>WR2_MAX_ADDR</b>   | Input            | `ASIZE       | Write max address of Write FIFO 2         |

| <b>WR2_LENGTH</b>     | Input            | 9            | Write length of Write FIFO 2              |

| <b>WR2_LOAD</b>       | Input            | 1            | Write register load input of Write FIFO 2 |

| <b>WR2_CLK</b>        | Input            | 1            | Write clock of Write FIFO 2               |

| <b>RD1_DATA</b>       | Output           | `DSIZE       | Read FIFO 1 output data                   |

| <b>RD_ENABLE</b>      | Input            | 1            | Read request to Read FIFO 1               |

| <b>RD1_ADDR</b>       | Input            | `ASIZE       | Read start address of Read FIFO 1         |

| <b>RD1_MAX_ADDR</b>   | Input            | `ASIZE       | Read max address of Read FIFO 1           |

| <b>RD1_LENGTH</b>     | Input            | 9            | Read length of Read FIFO 1                |

| <b>RD1_LOAD</b>       | Input            | 1            | Read register load input of Read FIFO 1   |

|              |        |            |                                         |

|--------------|--------|------------|-----------------------------------------|

| RD1_CLK      | Input  | 1          | Read clock of Write FIFO 1              |

| RD2_DATA     | Output | `DSIZE     | Read FIFO 2 output data                 |

| RD2          | Input  | 1          | <del>Read request to Read FIFO 2</del>  |

| RD2_ADDR     | Input  | `ASIZE     | Read start address of Read FIFO 2       |

| RD2_MAX_ADDR | Input  | `ASIZE     | Read max address of Read FIFO 2         |

| RD2_LENGTH   | Input  | 9          | Read length of Write FIFO 2             |

| RD2_LOAD     | Input  | 1          | Read register load input of Read FIFO 2 |

| RD2_CLK      | Input  | 1          | Read clock of Write FIFO 2              |

| SA           | Output | 12         | SDRAM address                           |

| BA           | Output | 2          | SDRAM bank address                      |

| CS_N         | Output | 2          | SDRAM chip selects<br>Active low        |

| CKE          | Output | 1          | SDRAM clock enable                      |

| RAS_N        | Output | 1          | SDRAM Row Address Strobe                |

| CAS_N        | Output | 1          | SDRAM Column Address Strobe             |

| WE_N         | Output | 1          | SDRAM write enable                      |

| DQ           | Output | `DSIZE     | SDRAM data bus                          |

| DQM          | Output | `DSIZE/8-1 | SDRAM data mask                         |

\* User can decide `ASIZE and `DSIZE. `ASIZE should no more than 23(the space of one SDRAM bank is 8M) and `DSIZE should no more than 16. In this system, `ASIZE is 23 and `DSIZE is 16.

*Table 7-1 SDRAM\_CONTROL\_4PORT module Interface*

## 7.3 Sub modules and Logic

### 7.3.1 FIFO

#### 1. Description

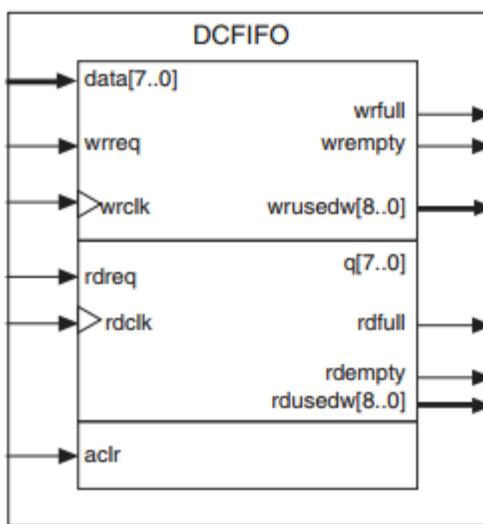

Altera provides dual-clock FIFO (DCFIFO) mega functions. User can use the FIFO parameter editor launched from the MegaWizard Plug-In Manager in the Quartus II software to build the FIFO mega functions.

The FIFO functions are mostly applied in data buffering applications that comply with the first-in-first-out data flow in asynchronous clock domains. The read and write signals are synchronized to the **rdclk** and **wrclk** clocks respectively. The input and output ports of the DCFIFO is illustrated below.

Figure 7-3 DCFIFO Structure

#### 2. Interface

| Port         | Direction | Width     | Description                                                                                                                                                                         |

|--------------|-----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>wrclk</b> | Input     | 1         | Positive-edge-triggered clock.<br>Use to synchronize the following ports: <ul style="list-style-type: none"><li>■ data</li><li>■ wrreq</li><li>■ wrfull</li><li>■ wrusedw</li></ul> |

| <b>rdclk</b> | Input     | 1         | Positive-edge-triggered clock.<br>Use to synchronize the following ports: <ul style="list-style-type: none"><li>■ q</li><li>■ rdreq</li><li>■ rdempty</li><li>■ rdusedw</li></ul>   |

| <b>data</b>  | Input     | lpm_width | Holds the data to be written in the FIFO when the <b>wrreq</b> signal is asserted. If you manually instantiate the FIFO, ensure the port width is equal to the lpm_width parameter. |

|                |        |            |                                                                                                                                                             |

|----------------|--------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>wrreq</b>   | Input  | 1          | Assert this signal to request for a write operation.                                                                                                        |

| <b>rdreq</b>   | Input  | 1          | Assert this signal to request for a read operation                                                                                                          |

| <b>aclr</b>    | Input  | 1          | Assert this signal to clear all the output status ports. Asynchronous.                                                                                      |

| <b>q</b>       | Output | lpm_width  | Shows the data read from the read request operation.<br>the width of the <b>q</b> port must be equal to the width of the data port.                         |

| <b>wrfull</b>  | Output | 1          | When asserted, the FIFO is considered full. Do not perform write request operation when the FIFO is full.                                                   |

| <b>rdempty</b> | Output | 1          | When asserted, the FIFO is considered empty. Do not perform read request operation when the FIFO is empty                                                   |

| <b>wrusedw</b> | Output | lpm_widthu | Show the number of words stored in the FIFO.<br>Ensure that the port width is equal to the <b>lpm_widthu</b> parameter if you manually instantiate the FIFO |

| <b>rdusedw</b> | Output | lpm_widthu | Show the number of words stored in the FIFO.<br>Ensure that the port width is equal to the <b>lpm_widthu</b> parameter if you manually instantiate the FIFO |

\* Some other ports of the DCFIFO IP Core (wrempy, rdfull, almost\_empty, almost\_full, etc.) are not used.

*Table 7-2 DCFIFO Interface*

### 3. Main Parameter

| Parameter           | Type    | Description                                                                                                                                                   |

|---------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>lpm_width</b>    | Integer | Specifies the width of the data and <b>q</b> ports                                                                                                            |

| <b>lpm_widthu</b>   | Integer | Specifies the width of the <b>rdusedw</b> and <b>wrusedw</b> ports                                                                                            |

| <b>lpm_numwords</b> | Integer | Specifies the depths of the FIFO you require.<br>The value must be at least 4.<br>The value assigned must comply with this equation, $2^{\text{LPM\_WIDTHU}}$ |

*Table 7-3 DCFIFO Parameter*

Attention: Default values of other parameter are commended to use. For more parameter, please refer to [http://www.altera.com/literature/ug/ug\\_fifo.pdf](http://www.altera.com/literature/ug/ug_fifo.pdf), page 10.

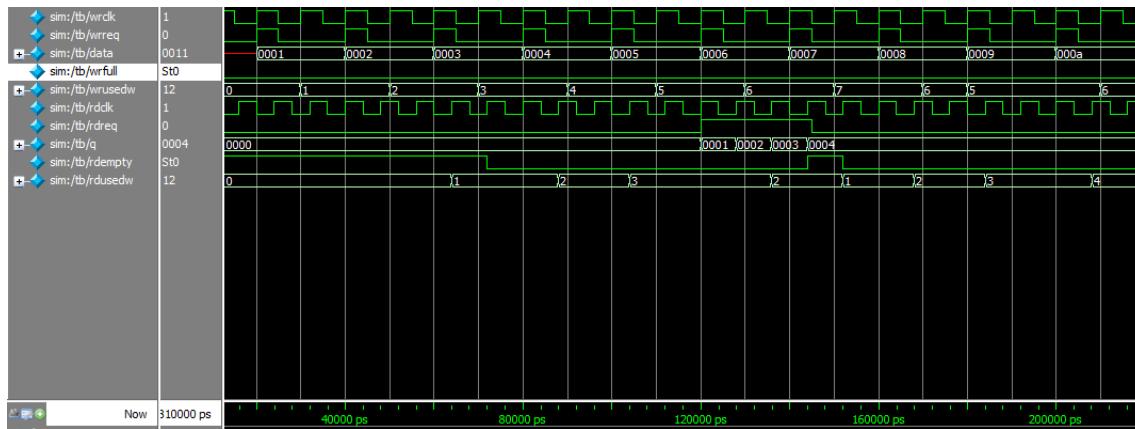

#### 4. Timing example

The figure below shows an example of the timing of DCFIFO. The write clock and read clock are of different frequency. This example is simulated by myself using Modelsim, which can help you get a better understand of DCFIFO. For more timing examples and explanation about DCFIFO, please refer to [http://www.altera.com/literature/ug/ug\\_fifo.pdf](http://www.altera.com/literature/ug/ug_fifo.pdf)

Figure 7-4 DCFIFO Timing Example

### 7.3.2 FIFOs Read/Write Control Logic

This module provides an interface for FIFOs and SDRAM to exchange data. Its main functions include:

1. Converting the state of FIFOs into read/write request signals for COMMAND\_INTERFACE sub module. The read/write request to SDRAM is generated automatically.

2. Generate read/write address to SDRAM.

3. Switch among the four FIFOs deciding which one should be read or write.

4. Control the read/write operations of FIFO according to SDRAM timing sequence.

Signals related to the FIFOs read/write control logic are demonstrated below. Table 7-4 shows functions of some signals in the figure below.

Figure 7-5 Signals Related to FIFO Read/Write Control Logic

#### 1. FIFO interfaces

The input/output signals of the 4 FIFOs in SDRAM\_CONTROL\_4PORT module is demonstrated below.

|                             | Write FIFO 1                       | Write FIFO 2                       | Read FIFO 1                                                    | Read FIFO 2                                                    |

|-----------------------------|------------------------------------|------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|

| <b>Wrclk</b>                | WR_CLK<br>(from <b>RAW2RGB</b> )   | WR_CLK<br>(from <b>RAW2RGB</b> )   | RD_CLK<br>(from <b>RAW2RGB</b> )                               | RD_CLK<br>(from <b>RAW2RGB</b> )                               |

| <b>Rdclk</b>                | CLK<br>(module clock)              | CLK<br>(module clock)              | CLK<br>(module clock)                                          | CLK<br>(module clock)                                          |

| <b>Data</b><br>(input data) | WR1_DATA<br>(from <b>RAW2RGB</b> ) | WR2_DATA<br>(from <b>RAW2RGB</b> ) | mDATAOUT                                                       | mDATAOUT                                                       |

| <b>Wrreq</b>                | WRITE<br>(from <b>RAW2RGB</b> )    | WRITE<br>(from <b>RAW2RGB</b> )    | RD_MASK[0]&<br>mWR_REQ<br>(Generated by FIFO<br>CONTROL LOGIC) | RD_MASK[1]&<br>mWR_REQ<br>(Generated by FIFO<br>CONTROL LOGIC) |

|                           |                                                                |                                                                |                                          |                                          |

|---------------------------|----------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------|------------------------------------------|

| <b>Rdreq</b>              | WR_MASK[0]&<br>mRD_REQ<br>(Generated by FIFO<br>CONTROL LOGIC) | WR_MASK[1]&<br>mRD_REQ<br>(Generated by FIFO<br>CONTROL LOGIC) | READ<br>(from<br><b>VGA CONTROLLER</b> ) | READ<br>(from<br><b>VGA CONTROLLER</b> ) |

| <b>Q</b><br>(output data) | mDATAIN1*                                                      | mDATAIN2*                                                      | RD1_DATA<br>(to <b>VGA CONTROLLER</b> )  | RD2_DATA<br>(to <b>VGA CONTROLLER</b> )  |

\* mDATAIN is the input data of SDRAM memory.

If WR\_MASK[0] is 1, mDATAIN = mDATAIN1; else if WR\_MASK[1] is 1, mDATAIN = mDATAIN2

*Table 7-4 Input and Output Signals of 4 FIFOs*

## 2. Read/Write Request Generation

The RAW2RGB module, which can be considered as data source, keeps writing data to the two write FIFOs. The VGA CONTROLLER module as the “data consumer”, keeps reading data to two read FIFOs. The states of the two write FIFOs are reflected by the **wr\_fifo\_rusedw1** and **wr\_fifo\_rusedw2** signals, which represents how much data in write FIFO1/2 can be read out to the SDRAM. The states of the two read FIFOs are reflected by the **rd\_fifo\_wusedw1** and **rd\_fifo\_wusedw2** signals, which represents how much data in read FIFO1/2 can be written to the VGA CONTROLLER.

When the amount of data in write FIFO1 reaches **rWR1\_LENGTH**, which is a parameter configured by user, a read request **mRD\_REQ** will be automatically generated to read data from Write FIFO 1 to the SDRAM, and WR\_MASK[0] will be set to 1. The amount of data read for one burst is **rWR1\_LENGTH** (16-bit data is transferred for one clock cycle in a burst). And also when data is read out from write FIFO 1, RAW2RGB module still keeps writing data to it.

Write FIFO 1 has the highest priority to exchange data with SDRAM. If the amount of data in write FIFO 1 is not enough for one burst and SDRAM data line is not occupied at the same time, write FIFO 2 will be considered. If the amount of data in write FIFO2 reaches **rWR2\_LENGTH**, read request **mRD\_REQ** will be generated to read data from Write FIFO 2 to the SDRAM, and WR\_MASK[1] will be set to 1.

If both write FIFO 1 and 2 do not have enough data to be read out and SDRAM is not busy, read FIFO 1 will be considered. When the amount of data in read FIFO1 is less than **rRD1\_LENGTH**, a write request **mWR\_REQ** will be automatically generated to write data from SDRAM to the write FIFO1, and RD\_MASK[0] will be set to 1. And also when data is written from SDRAM to read FIFO 1, VGA CONTROLLER module still keeps reading data to it.

Read FIFO 2 has the lowest priority to communicate with SDRAM. The circumstance is similar to what are mentioned above.

The code about this part is shown below.

```

533      //  Write Side 1

534      if( (write_side_fifo_rusedw1 >= rWR1_LENGTH) && (rWR1_LENGTH!=0) )

535      begin

536          mADDR    <=  rWR1_ADDR;

537          mLENGTH <=  rWR1_LENGTH;

538          WR_MASK <=  2'b01;

539          RD_MASK <=  2'b00;

540          mWR      <=  1;

541          mRD      <=  0;

542      end

543      //  Write Side 2

544      else if( (write_side_fifo_rusedw2 >= rWR2_LENGTH) && (rWR2_LENGTH!=0) )

545      begin

546          mADDR    <=  rWR2_ADDR;

547          mLENGTH <=  rWR2_LENGTH;

548          WR_MASK <=  2'b10;

549          RD_MASK <=  2'b00;

550          mWR      <=  1;

551          mRD      <=  0;

552      end

553      //  Read Side 1

554      else if( (read_side_fifo_wusedw1 < rRD1_LENGTH) )

555      begin

556          mADDR    <=  rRD1_ADDR;

557          mLENGTH <=  rRD1_LENGTH;

558          WR_MASK <=  2'b00;

559          RD_MASK <=  2'b01;

560          mWR      <=  0;

561          mRD      <=  1;

562      end

563      //  Read Side 2

564      else if( (read_side_fifo_wusedw2 < rRD2_LENGTH) )

565      begin

566          mADDR    <=  rRD2_ADDR;

567          mLENGTH <=  rRD2_LENGTH;

568          WR_MASK <=  2'b00;

569          RD_MASK <=  2'b10;

570          mWR      <=  0;

```

Figure 7-6 Code Related to Read/Write Request Generation

### 3. Address Generation

The FIFOs read/write logic also generates the read/write address **mADDR** to the SDRAM.

The value of **mADDR** is assigned when a read/write request to the SDRAM is generated. If SDRAM reads data from write FIFO 1, **rWR1\_ADDR**, which is the register write address of write FIFO 1, will be assigned to **mADDR**. Likewise, if SDRAM reads data from write FIFO 2, **rWR2\_ADDR** will be assigned to **mADDR**. If SDRAM writes data to read FIFO 1 or 2, **rRD1\_ADDR** or **rRD2\_ADDR** will be assigned to **mADDR**.

The value of **rWR1\_ADDR** is generated in the following way: when user input signal **WR1\_LOAD** is set to 1 (i.e. the FIFO is reset), user input address **WR1\_ADDR** will be assigned to **rWR1\_ADDR**. Else when write FIFO 1 writes data to SDRAM, after a write transaction is finished, **rWR1\_ADDR** will adds **rWR1\_LENGTH** to its original value. If the current address is less than **rWR1\_MAX\_ADDR - rWR1\_LENGTH**, the address will be reassigned to **WR1\_ADDR**. Here **rWR1\_MAX\_ADDR** is the max address offset to **WR1\_ADDR**.

The condition of **WR2\_ADDR**, **RD1\_ADDR**, **RD2\_ADDR** is similar. The code about this part is shown below.

```

463

464

465

466

467

468

469

470

471

472

473

474

if(WR1_LOAD)

begin

rWR1_ADDR  <=  WR1_ADDR;

rWR1_LENGTH <=  WR1_LENGTH;

end

else if(mWR_DONE&WR_MASK[0])

begin

if(rWR1_ADDR<rWR1_MAX_ADDR-rWR1_LENGTH)

rWR1_ADDR  <=  rWR1_ADDR+rWR1_LENGTH;

else

rWR1_ADDR  <=  WR1_ADDR;

end

```

Figure 7-7 Code Related to Address Generation

Notice that **mADDR** is multiplex. When the FIFOs are reset, user-defined address (**WR1\_ADDR**, **WR2\_ADDR**, **RD1\_ADDR** and **RD2\_ADDR**) can be assigned to **mADDR**. During the normal read/write transaction, **mADDR** includes the column address, row address and bank address to SDRAM.

**Attention:**

In this design, Write FIFO 1 and read FIFO 1 use the same part of SDRAM since they have the same start address(**WR1\_ADDR** = **RD1\_ADDR** = 0) and maximum offset (**rWR1\_MAX\_ADDR** = **rRD1\_MAX\_ADDR** = 640\*480). The maximum offset is 640\*480, which is the resolution of one input image (please refer to RAW2RGB module for detail). So only the data amount of one image can be stored in SDRAM.

We know the actual storage space of one bank of the SDRAM is 8M, which is larger than 640\*480. Why no more images are stored in the SDRAM? The reason is that the read frequency and write frequency of SDRAM are different, which is because the data source (RAW2RGB module) and data consumer (VGA CONTROLLER module) are in different clock domain. Thus the change of **rWR1\_ADDR** and **rRD1\_ADDR** are not simultaneous. If the read frequency of SDRAM is quicker than the write frequency, **rRD1\_ADDR** will grow quicker than **WR1\_ADDR**. Supposing infinite space is used in SDRAM to store data, which means the difference between **rRD1\_ADDR** and **rWR1\_ADDR** are getting larger. So the image data written to SDRAM and the image data read from SDRAM will not be simultaneous, and the time delay between input image and output image will be larger and larger.

So we set the maximum offset is 640\*480 to store only one image in SDRAM. Since **rRD1\_ADDR** and **rWR1\_ADDR** are both circular, the difference between them will be no more than 640\*480, which means the delay between input image and output image will be no more than the time of capturing one frame for camera. In this way, the output image can be regarded as “real-time”. However, if we store the data amount of ten images in SDRAM, the maximum time delay between input and output will be the time of capturing ten frames for camera, which is longer.

#### 4. Full-Page Burst Mode and timing sequence

When large amount of data is read or written, Full-Page Burst Mode is a good way to take full use of SDRAM performance and enhance read/write speed.

The full-page burst is used in conjunction with the BURST TERMINATE command to generate

arbitrary burst lengths, which can be defined by user according to the actual application. The data in a row can be read or written consecutively in full-page mode. The address doesn't need to be configured to every data.

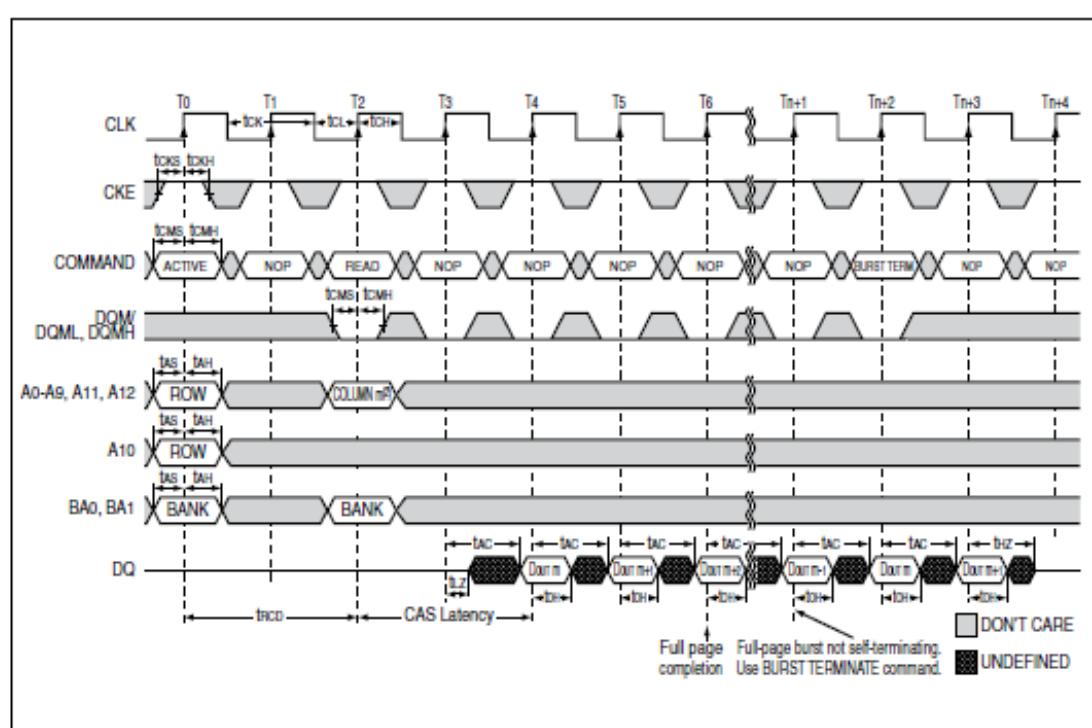

### Read timing sequence

Before any READ or WRITE commands can be issued to a bank within the SDRAM, a row in that bank must be opened. This is accomplished via the ACTIVE command, which selects both the bank and the row to be activated. After opening a row (issuing an ACTIVE command), a READ or WRITE command may be issued to that row after several clock cycles determined by tRCD.

The starting column and bank addresses are provided with the READ command. During READ bursts, the valid data-out element from the starting column address will be available following the CAS latency after the READ command. Each subsequent data-out element will be valid by the next positive clock edge.

Upon completion of a burst, assuming no other commands have been initiated, the DQs will go High-Z. A full-page burst will continue until terminated.

Full-page READ bursts can be truncated with the BURST TERMINATE command or PRECHARGE command to the same bank, and The BURST TERMINATE command or PRECHARGE command should be issued  $x$  cycles before the clock edge at which the last desired data element is valid, where  $x$  equals the CAS latency minus one. The diagram below shows Full-Page burst read terminated by BURST TERMINATE command for CAS latency=2. For more detail, please refer to [IS42R16320D.pdf, Page 37](#)

### READ - FULL-PAGE BURST

Figure 7-8 Read Full-Page Burst

The code about this part is shown below. ST is the controller status which records the timing of SDRAM. When the FIFOs control logic send a write/read command **CMD** to **COMMAND\_INTERFACE** module and get acknowledge signal **CMDACK**, the read/write transaction to SDRAM begins.

```

378

379

380

381

382

383

384

385

386

387

388

389

390

391

392

393

394

395

396

397

398

399

400

401

402

403

404

405

406

407

408

409

case(ST)

0: begin

if({Pre_RD,mRD}==2'b01)

begin

Read    <= 1;

Write   <= 0;

CMD     <= 2'b01;

ST      <= 1;

end

else if({Pre_WR,mWR}==2'b01)

begin

Read    <= 0;

Write   <= 1;

CMD     <= 2'b10;

ST      <= 1;

end

end

1: begin

if(CMDACK==1)

begin

CMD<=2'b00;

ST<=2;

end

end

default:

begin

if(ST!=SC_CL+SC_RCD+mLENGTH+1)

ST<=ST+1;

else

ST<=0;

end

endcase

```

Figure 7-9 Code Related to Read Timing

In a read transaction, after ( **trCD** + **tSC\_CL** ) clock cycles the READ command is executed, input data from SDRAM is valid ( **tSC\_CL** = CAS latency) according to timing sequence in last page. After another **mLENGTH** clock cycles, which is the user-defined read length, the input data is invalid. The related code is shown below.

```

411

412

413

414

415

416

417

418

419

420

421

422

423

if(Read)

begin

if(ST==SC_CL+SC_RCD+1)

OUT_VALID  <= 1;

else if(ST==SC_CL+SC_RCD+mLENGTH+1)

begin

OUT_VALID  <= 0;

Read       <= 0;

mRD_DONE   <= 1;

end

end

else

mRD_DONE   <= 0;

```

Figure 7-10 Code Related to Read Timing Sequence

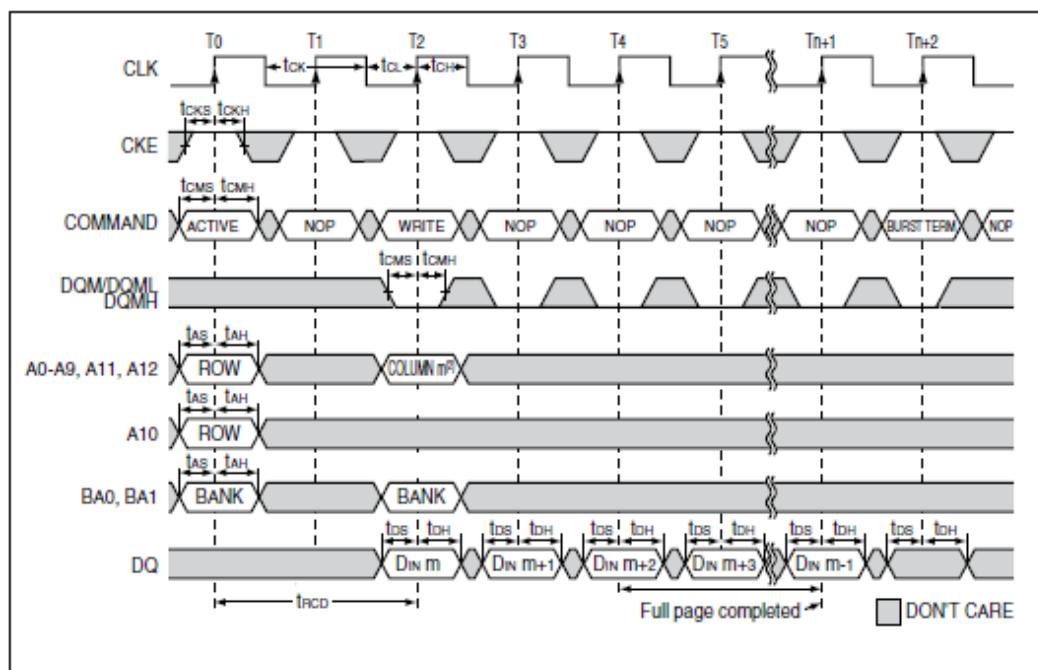

## Write timing sequence

An ACTIVE command must be issued before the WRITE command, which is similar to the read timing sequence. The WRITE command may be issued after several clock cycles determined by tRCD.

The starting column and bank addresses are provided with the WRITE command. During WRITE bursts, the first valid data-in element will be registered coincident with the WRITE command. Subsequent data elements will be registered on each successive positive clock edge. Upon completion of a fixed-length burst, assuming no other commands have been initiated, the DQs will remain High-Z and any additional input data will be ignored. A full-page burst will continue until terminated.

Full-page WRITE bursts can be truncated with the BURST TERMINATE command or PRECHARGE command to the same bank. When truncating a WRITE burst with the BURST RERMINATE, the input data applied coincident with the BURST TERMINATE command will be ignored. The last data written (provided that DQM is LOW at that time) will be the input data applied one clock previous to the BURST TERMINATE command. The diagram below shows Full-Page burst write terminated by BURST TERMINATE command. For more detail, please refer to [IS42R16320D.pdf, Page 44](#)

## WRITE - FULL PAGE BURST

Figure 7-11 Write Full-Page Burst

The code about this part is shown below. In a write transaction, after `trCD` clock cycles after the `WRITE` command is executed, output data to SDRAM is valid according to timing sequence in last page. After another `mLENGTH` clock cycles, which is the user-defined read length, the output data is invalid. The related code is shown below.

```

425

426

427

428

429

430

431

432

433

434

435

436

437

438

if(Write)

begin

if(ST==SC_CL-1)

IN_REQ  <=  1;

else if(ST==SC_CL+mLENGTH-1)

IN_REQ  <=  0;

else if(ST==SC_CL+SC_RCD+mLENGTH)

begin

Write  <=  0;

mWR_DONE<=  1;

end

end

else

mWR_DONE<=  0;

```

Figure 7-12 Code Related to Write Timing

### 7.3.3 COMMAND\_INTERFACE Sub Module

#### 1. Description

This module judges the input CMD signal from FIFOs CONTROL LOGIC and output the corresponding decoded command to COMMAND module. There are also an initial timer and a SDRAM refresh timer embedded in the module. When the SDRAM is powered up and initialized, a predefined manner must be complied. In this case, the decoded command to COMMAND module is generated according to the value of initial timer. Also Because the SDRAM needs to be refreshed automatically when it works, a REFRESH decoded command is generated at regular interval according to the refresh timer.

#### 2. Interface

| Port    | Direction | Width  | Description                              |

|---------|-----------|--------|------------------------------------------|

| CLK     | Input     | 1      | Module clock                             |

| RESET_N | Input     | 1      | Module reset<br>active low, asynchronous |

| CMD     | Input     | 3      | Command input                            |

| ADDR    | Input     | `ASIZE | Address                                  |

| REF_ACK | Input     | 1      | Refresh request acknowledge              |

| CM_ACK  | Input     | 1      | Command acknowledge(from COMMAND module) |

| NOP     | Output    | 1      | Decoded NOP command                      |

| READA   | Output    | 1      | Decoded READA command                    |

| WRITEA  | Output    | 1      | Decoded WRITEA command                   |

|           |        |        |                                              |

|-----------|--------|--------|----------------------------------------------|

| REFRESH   | Output | 1      | Decoded REFRESH command                      |

| PRECHARGE | Output | 1      | Decoded PRECHARGE command                    |

| LOAD_MODE | Output | 1      | Decoded LOAD_MODE command                    |

| SADDR     | Output | 'ASIZE | Registered version of <b>ADDR</b>            |

| REF_REQ   | Output | 1      | Refresh request                              |

| INIT_REQ  | Output | 1      | Initial request                              |

| CMD_REQ   | Output | 1      | Command acknowledge (to FIFOs CONTROL LOGIC) |

*Table 7-5 CONTROL\_INTERFACE sub module Interface*

### 3. Function

#### Generate WRITEA and READA command

This module generates **WRITEA** and **READA** command to the COMMAND module according to the input **CMD** signal from FIFOs CONTROL LOGIC.

If **CMD** is 3'b001, **READA** command is generated.

If **CMD** is 3'b010, **WRITEA** command is generated.

If **CMD** is 3'b000, **NOP** command is generated.

#### Generate refresh command

Since the storage unit of SDRAM is actually capacitor which tends to discharge, SDRAM must be auto refreshed at regular interval to maintain the data stored. According to the datasheet of SDRAM IS42R16320D, The SDRAM must be refreshed 8k times in 64ms. Because the clock frequency of the module is 125MHz, therefore 64ms means 8M clock cycles. Thus the interval between two auto refresh behaviors is  $8M/8k = 1k$  clock cycles.

The code in this module about auto refresh is shown below. The parameter **REF\_PER** is defined in the file **SDRAM\_PARAM.h**. Its value is 1024 for the reason mentioned above. A timer is used to calculate the passing clock cycles since last refresh. If the value of timer is 0, a refresh request is generated. And when a refresh acknowledge is received, the value of timer will be reset to **REF\_PER**.

```

151  // refresh timer

152  always @ (posedge CLK or negedge RESET_N) begin

153      if (RESET_N == 0)

154          begin

155              timer        <= 0;

156              REF_REQ     <= 0;

157          end

158      else

159          begin

160              if (REF_ACK == 1)

161                  begin

162                      timer <= REF_PER;

163                      REF_REQ <= 0;

164                  end

165              else if (INIT_REQ == 1)

166                  begin

167                      timer <= REF_PER+200;

168                      REF_REQ <= 0;

169                  end

170              else

171                  timer <= timer - 1'b1;

172

173              if (timer==0)

174                  REF_REQ     <= 1;

175

176          end

177      end

```

Figure 7-13 Code Related to Refresh Request Generation

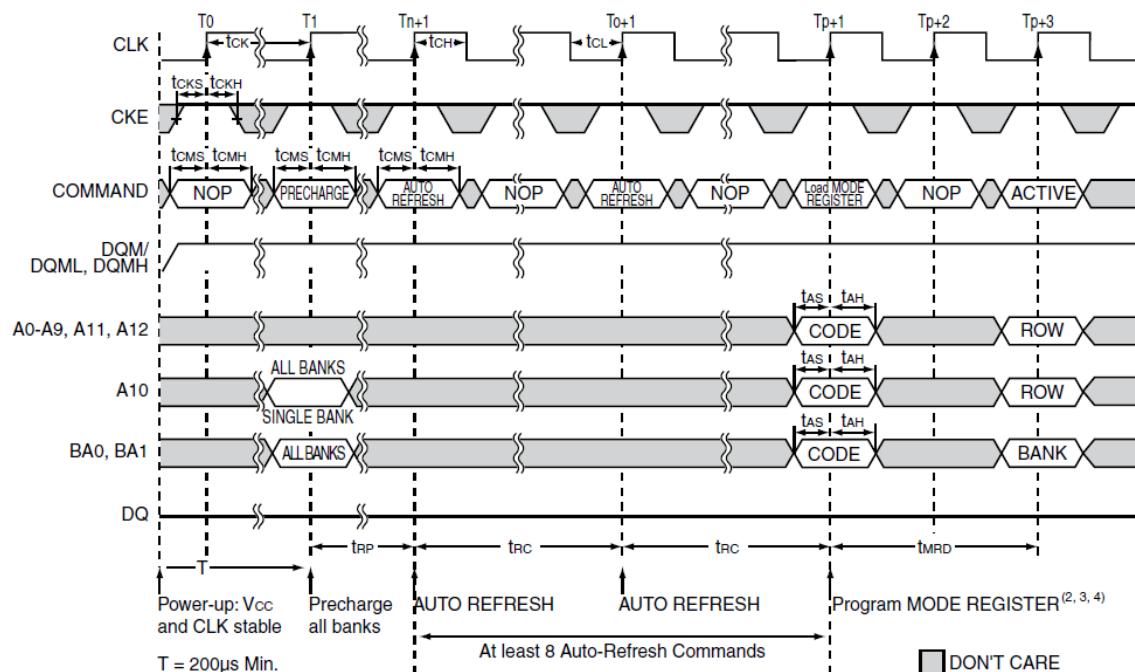

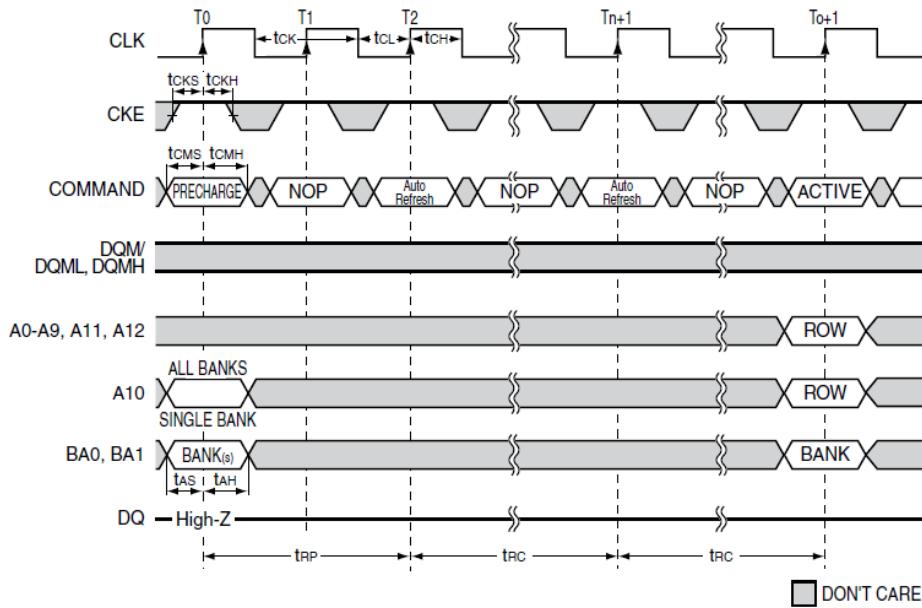

### Generate Initial manner

When the SDRAM is powered up and initialized, a predefined manner must be complied. The values of REFRESH command, PRECHARGE command and LOAD\_MODE command are decided according to the initialized timing sequence, which is illustrated below. For more details, please refer to [IS42R16320D.pdf, Page 22-24](#)

Figure 7-14 Initialization Timing Sequence

Figure 7-15 Auto Refresh Cycles in Initialization

A 100us delay is required prior to issuing any command other than a COMMAND INHIBIT or a NOP. The COMMAND INHIBIT or NOP may be applied during the 100us period and should continue at least through the end of the period. With at least one COMMAND INHIBIT or NOP command having been applied, a PRECHARGE command should be applied once the 100us delay has been satisfied. All banks must be precharged. This will leave all banks in an idle state after which at least eight AUTO REFRESH cycles must be performed. After the AUTO REFRESH cycles are complete, the SDRAM is then ready for mode register programming. The mode register should be loaded prior to applying any operational command because it will power up in an unknown state.

The code about the generation of decoded command during the initialization is shown below.

```

180  always @(posedge CLK or negedge RESET_N) begin

181      if (RESET_N == 0)

182          begin

183              init_timer      <= 0;

184              REFRESH        <= 0;

185              PRECHARGE      <= 0;

186              LOAD_MODE      <= 0;

187              INIT_REQ       <= 0;

188          end

189      else

190          begin

191              if (init_timer < (INIT_PER+201))

192                  init_timer  <= init_timer+1;

193

194              if (init_timer < INIT_PER)

195                  begin

196                      REFRESH        <=0;

197                      PRECHARGE      <=0;

198                      LOAD_MODE      <=0;

199                      INIT_REQ       <=1;

200                  end

201              else if(init_timer == (INIT_PER+20))

202                  begin

203                      REFRESH        <=0;

204                      PRECHARGE      <=1;

205                      LOAD_MODE      <=0;

206                      INIT_REQ       <=0;

207                  end

```

PRECHARGE

COMMAND

```

208

209

210

211

212

213

214

215

216

217

218

219

220

221

222

223

224

225

226

227

228

229

230

231

232

233

234

235

236

237

8 AUTOREFRESH

COMMAND

LOAD_MODE

COMMAND

begin

REFRESH  <=1;

PRECHARGE <=0;

LOAD_MODE <=0;

INIT_REQ  <=0;

end

else if( init_timer == (INIT_PER+40) ) ||

(init_timer == (INIT_PER+60) ) ||

(init_timer == (INIT_PER+80) ) ||

(init_timer == (INIT_PER+100) ) ||

(init_timer == (INIT_PER+120) ) ||

(init_timer == (INIT_PER+140) ) ||

(init_timer == (INIT_PER+160) ) ||

(init_timer == (INIT_PER+180) )

begin

REFRESH  <=0;

PRECHARGE <=0;

LOAD_MODE <=1;

INIT_REQ  <=0;

end

else

begin

REFRESH  <=0;

PRECHARGE <=0;

LOAD_MODE <=0;

INIT_REQ  <=0;

end

end

```

Figure 7-16 Code Related to Initial Manner Generation

**Attention:**

1. The clock cycles between each auto refresh is 20 cycles, which is equal to t<sub>RC</sub> of the SDRAM.

2. The parameter INIT\_PER in the code is configured in file **SDRAM\_PARAM.h**. The value of INIT\_PER is 25000. Since the module clock frequency of SDRAM\_CONTROL\_4PORT module is 125MHz, thus 25000 clock cycles is 200us, which is the minimum time required before the first precharge command is generated.

### 7.3.4 COMMAND sub module

#### 1. Description

This module uses decoded command signals from CONTROL\_INTERFACE sub module to generate operations conforming to SDRAM protocol and control the signals output to SDRAM. This module also generates **OE** signal for data path module to control it. Besides, non-multiplex input address ADDR is transferred into multiplex address for SDRAM and sent to **SA** and **BA** according to the time.

**Attention:** the code of this module is not suggested to be modified. You do not need to understand the internal logic of this module, and the following part can be omitted.

#### 2. Interface

| Port           | Direction | Width | Description                              |

|----------------|-----------|-------|------------------------------------------|

| <b>CLK</b>     | Input     | 1     | Module clock                             |

| <b>RESET_N</b> | Input     | 1     | Module reset<br>active low, asynchronous |

|                  |        |        |                                     |

|------------------|--------|--------|-------------------------------------|

| <b>SADDR</b>     | Input  | `ASIZE | Multiplex Address                   |

| <b>NOP</b>       | Input  | 1      | Decoded NOP command                 |

| <b>READA</b>     | Input  | 1      | Decoded READA command               |

| <b>WRITEA</b>    | Input  | 1      | Decoded WRITEA command              |

| <b>REFRESH</b>   | Input  | 1      | Decoded REFRESH command             |

| <b>PRECHARGE</b> | Input  | 1      | Decoded PRECHARGE command           |

| <b>LOAD_MODE</b> | Input  | 1      | Decoded LOAD_MODE command           |

| <b>REF_REQ</b>   | Input  | 1      | Refresh request                     |

| <b>INIT_REQ</b>  | Input  | 1      | Initial request                     |

| <b>PM_STOP</b>   | Input  | 1      | Page mode stop                      |

| <b>REF_ACK</b>   | Output | 1      | Refresh request acknowledge         |

| <b>CMD_ACK</b>   | Output | 1      | Command acknowledge                 |

| <b>OE</b>        | Output | 1      | OE signal for DATA_PATH module      |

| <b>SA</b>        | Output | 12     | SDRAM address                       |

| <b>BA</b>        | Output | 2      | SDRAM bank address                  |

| <b>CS_N</b>      | Output | 2      | SDRAM chip selects<br>Active low    |

| <b>CKE</b>       | Output | 1      | SDRAM clock enable                  |

| <b>RAS_N</b>     | Output | 1      | SDRAM Row Address Strobe Command    |

| <b>CAS_N</b>     | Output | 1      | SDRAM Column Address Strobe Command |

| <b>WE_N</b>      | Output | 1      | SDRAM write enable                  |

Table 7-6 COMMAND sub module Interface

### 3. Function

#### Generate operations to SDRAM

Operations are generated according to the input decoded command signals. The logic is generated below. Notice that REFRESH command has higher priority than READA/WRITEA command.

```

182     if ((REF_REQ == 1 | REFRESH == 1) & command_done == 0 & do_refresh == 0 & rp_done == 0)           // Refresh

183         & do_reada == 0 & do_writea == 0)

184         do_refresh <= 1;

185     else

186         do_refresh <= 0;

187

188     if ((READA == 1) & (command_done == 0) & (do_reada == 0) & (rp_done == 0) & (REF_REQ == 0))      // READA

189     begin

190         do_reada <= 1;

191         ex_read <= 1;

192     end

193     else

194         do_reada <= 0;

195

196     if ((WRITEA == 1) & (command_done == 0) & (do_writea == 0) & (rp_done == 0) & (REF_REQ == 0))    // WRITEA

197     begin

198         do_writea <= 1;

199         ex_write <= 1;

200     end

201     else

202         do_writea <= 0;

203

204     if ((PRECHARGE == 1) & (command_done == 0) & (do_preamble == 0))      // PRECHARGE

205         do_preamble <= 1;

206     else

207         do_preamble <= 0;

208

209     if ((LOAD_MODE == 1) & (command_done == 0) & (do_load_mode == 0))      // LOADMODE

210         do_load_mode <= 1;

211     else

212         do_load_mode <= 0;

```

Figure 7-17 Code Related to Operation Generation

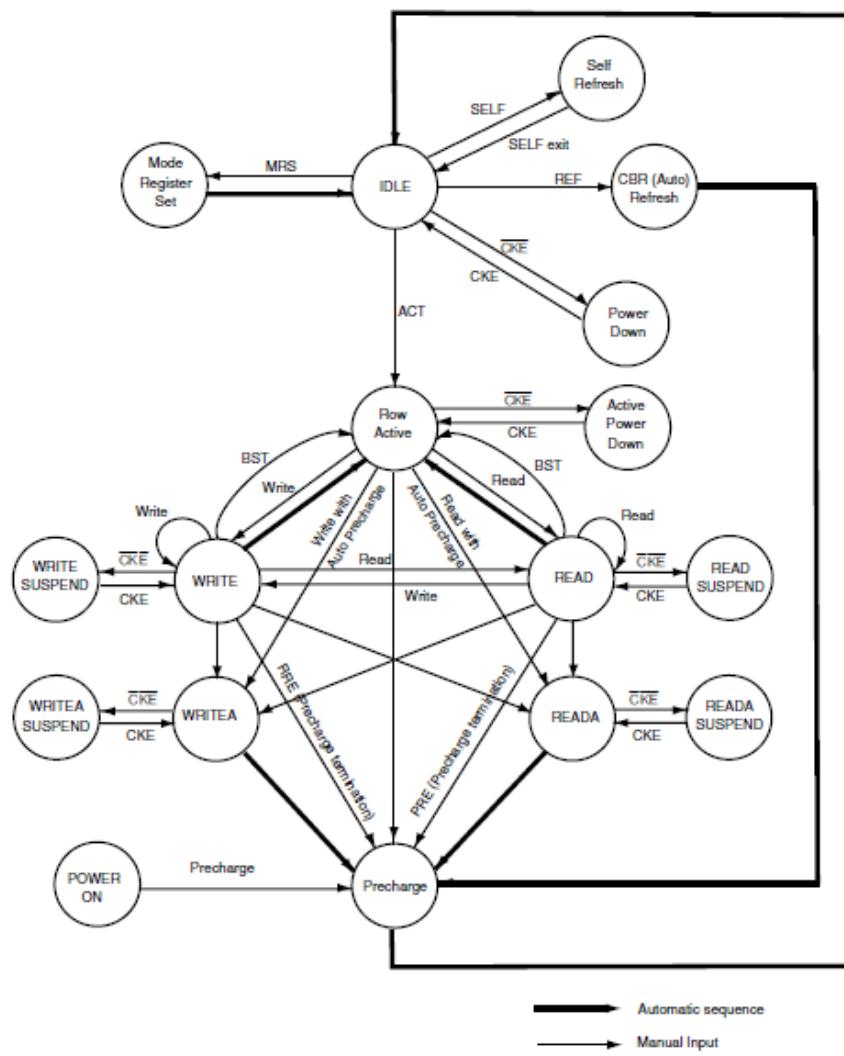

What needs to be noticed is that WRITEA and READA command actually imply an ACTIVE command first, which is demonstrated in the state diagram below. Thus when the module receives WRITEA or READA command, which means the interval signal do\_wirtea or do\_reada is 1, ACTIVE command must be executed first, and then write or read operation are enabled after a time delay according to CAS configuration of SDRAM.

Figure 7-18 SDRAM State Diagram

The code below tracks the time between the ACTIVE command and the subsequent WRITE or READ command. The shift register is set using the configuration register setting SC\_RCD. The shift register is loaded with a single '1' with the position within the register dependent on SC\_RCD. When the '1' is shifted out of the register it sets so\_rw which triggers a write or reada command.

```

335  always @ (posedge CLK or negedge RESET_N)

336  begin

337      if (RESET_N == 0)

338      begin

339          rw_shift <= 0;

340          do_rw    <= 0;

341      end

342

343      else

344      begin

345

346          if ((do_reada == 1) | (do_writea == 1))

347          begin

348              if (SC_RCD == 1)                                // Set the shift register

349                  do_rw <= 1;

350              else if (SC_RCD == 2)

351                  rw_shift <= 1;

352              else if (SC_RCD == 3)

353                  rw_shift <= 2;

354

355          end

356          else

357          begin

358              rw_shift <= (rw_shift>>1);

359              do_rw    <= rw_shift[0];

360

361      end

362

363  always @ (posedge CLK or negedge RESET_N)

364  begin

365      if (RESET_N == 0)

366      begin

367          rw_shift <= 0;

368          do_rw    <= 0;

369      end

370

371      else

372      begin

373

374          if ((do_reada == 1) | (do_writea == 1))

375          begin

376              if (SC_RCD == 1)                                // Set the shift register

377                  do_rw <= 1;

378              else if (SC_RCD == 2)

379                  rw_shift <= 1;

380              else if (SC_RCD == 3)

381                  rw_shift <= 2;

382

383          end

384          else

385          begin

386              rw_shift <= (rw_shift>>1);

387              do_rw    <= rw_shift[0];

388

389      end

390

391  end

```

Figure 7-19 Code Related to Timing Tracking After ACTIVE Command

## OE signal

OE is a control signal of DATA\_PATH module. OE is 1 when write operation is executed, and OE is 0 when read operation is executed. For normal burst write (SC\_PM=0) the duration of OE is dependent on the configured burst length. For page mode accesses (SC\_PM=1) the OE signal is turned on at the start of the write command and is left on until a PRECHARGE (page burst terminate) is detected.

## Address

Non-multiplex address **SADDR** is transferred into multiplex address for SDRAM and sent to **SA** and **BA** according to the time. The way how ADDR is divided into bank address, row address and column address is shown in the code below:

```

133  // assignment of the row address bits from SADDR

134  assign rowaddr = SADDR[`ROWSTART + `ROWSIZE - 1: `ROWSTART];

135

136  // assignment of the column address bits

137  assign coladdr = SADDR[`COLSTART + `COLSIZE - 1: `COLSTART];

138

139  // assignment of the bank address bits

140  assign bankaddr = SADDR[`BANKSTART + `BANKSIZE - 1: `BANKSTART];

```

Figure 7-20 Code Related to Address Assignment

The parameter ROWSTART, ROWSIZE, COLSTART, COLSIZE, BANKSTART, BANKSIZE are defined in the file **Sdram\_Param.h**.

## Acknowledge signal

When a REFRESH request generated by the internal refresh timer circuit in the COTROL\_INTERFACE module is received, this module will generate a refresh acknowledge signal REF\_ACK to the CONTROL\_INTERFACE module. When other kinds of command is received, this module will generate a command acknowledge signal CMD\_ACK to the CONTROL\_INTERFACE module. The code about this part is shown below.

```

371  always @(posedge CLK or negedge RESET_N)

372  begin

373

374  if (RESET_N == 0)

375  begin

376    CM_ACK <= 0;

377    REF_ACK <= 0;

378

379  end

380

381  else

382  begin

383    if (do_refresh == 1 & REF_REQ == 1)           // Internal refresh timer refresh request

384    begin

385      REF_ACK <= 1;

386    end

387    else if ((do_refresh == 1) | (do_reada == 1) | (do_writea == 1) | (do_preamble == 1) | (do_load_mode))

388    begin

389      CM_ACK <= 1;

390    end

391    else

392    begin

393      REF_ACK <= 0;

394      CM_ACK <= 0;

395    end

396  end

397

398  end

```

Figure 7-21 Code Related to Acknowledge Signals Generation

### RAS\_N, CAS\_N, and WE\_N signal

These signals are generated according to the issued command and the table below. For more details, please refer to [IS42R16320D.pdf, Page 9](#)

#### COMMAND TRUTH TABLE

| Function                    | CKE | n - 1 | n | CS | $\overline{\text{RAS}}$ | $\overline{\text{CAS}}$ | $\overline{\text{WE}}$ | BA1 | BA0 | A10 | A9 - A0 | A12, A11 |

|-----------------------------|-----|-------|---|----|-------------------------|-------------------------|------------------------|-----|-----|-----|---------|----------|

| Device deselect (DESL)      |     | H     | x | H  | x                       | x                       | x                      | x   | x   | x   | x       | x        |

| No operation (NOP)          |     | H     | x | L  | H                       | H                       | H                      | x   | x   | x   | x       | x        |

| Burst stop (BST)            |     | H     | x | L  | H                       | H                       | L                      | x   | x   | x   | x       | x        |

| Read                        |     | H     | x | L  | H                       | L                       | H                      | V   | V   | L   | V       |          |

| Read with auto precharge    |     | H     | x | L  | H                       | L                       | H                      | V   | V   | H   | V       |          |

| Write                       |     | H     | x | L  | H                       | L                       | L                      | V   | V   | L   | V       |          |

| Write with auto precharge   |     | H     | x | L  | H                       | L                       | L                      | V   | V   | H   | V       |          |

| Bank activate (ACT)         |     | H     | x | L  | L                       | H                       | H                      | V   | V   | V   | V       |          |

| Precharge select bank (PRE) |     | H     | x | L  | L                       | H                       | L                      | V   | V   | L   | x       |          |

| Precharge all banks (PALL)  |     | H     | x | L  | L                       | H                       | L                      | x   | x   | H   | x       |          |

| CBR Auto-Refresh (REF)      |     | H     | H | L  | L                       | L                       | H                      | x   | x   | x   | x       |          |

| Self-Refresh (SELF)         |     | H     | L | L  | L                       | L                       | H                      | x   | x   | x   | x       |          |

| Mode register set (MRS)     |     | H     | x | L  | L                       | L                       | L                      | L   | L   | L   | V       |          |

Note: H=ViH, L=ViL, x=ViH or ViL, V=Valid Data.

Figure 7-22 Command Truth Table

The code of this part is shown below.

```

436 //Generate the appropriate logic levels on RAS_N, CAS_N, and WE_N

437 //depending on the issued command.

438 //

439 if ( do_refresh==1 ) begin

440   RAS_N <= 0;

441   CAS_N <= 0;

442   WE_N <= 1;

443 end

444 else if ((do_preamble==1) & ((oe4 == 1) | (rw_flag == 1))) begin // burst terminate if write is active

445   RAS_N <= 1;

446   CAS_N <= 1;

447   WE_N <= 0;

448 end

449 else if (do_preamble==1) begin // Precharge All: S=00, RAS=0, CAS=1, WE=0

450   RAS_N <= 0;

451   CAS_N <= 1;

452   WE_N <= 0;

453 end

454 else if (do_load_mode==1) begin // Mode Write: S=00, RAS=0, CAS=0, WE=0

455   RAS_N <= 0;

456   CAS_N <= 0;

457   WE_N <= 0;

458 end

459 else if (do_reada == 1 | do_writea == 1) begin // Activate: S=01 or 10, RAS=0, CAS=1, WE=1

460   RAS_N <= 0;

461   CAS_N <= 1;

462   WE_N <= 1;

463 end

464 else if (do_rw == 1) begin // Read/Write: S=01 or 10, RAS=1, CAS=0, WE=0 or 1

465   RAS_N <= 1;

466   CAS_N <= 0;

467   WE_N <= rw_flag;

468 end

469 else if (do_initial ==1) begin

470   RAS_N <= 1;

471   CAS_N <= 1;

472   WE_N <= 1;

473 end

474 else begin // No Operation: RAS=1, CAS=1, WE=1

475   RAS_N <= 1;

476   CAS_N <= 1;

477   WE_N <= 1;

478 end

```

Figure 7-23 Code Related to RAS\_N, CAS\_N, WE\_N Signals Assignment