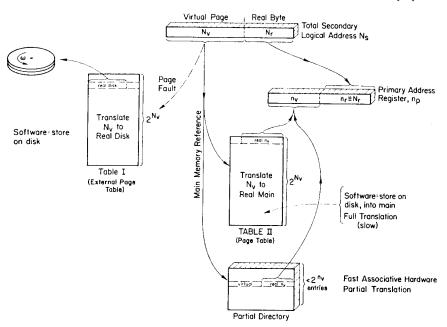

proceeds with little difficulty as long as the second page is also within main memory. If the second page is not in main memory, the required page is transferred into main memory as needed; this is called demand paging, or in some cases the page is transferred in advance by special look-ahead operations. Demand paging is more commonly used. Assuming that main memory is already full, the subsequent operations necessitate a replacement algorithm to determine which page is to be removed, a mapping function to determine where it is to be relocated on secondary storage, and means of keeping track of its new location. Also the location of the desired page in secondary storage must be determined. Since page replacement is a time-consuming operation. either the CPU transfers operation to a different user's program and continues processing, or it sits idle while the transfer is performed. This is a design option set by the desired system cost-performance. Once a page is transferred to main memory, many words within that page will be used more than once. such as in looping operations. Thus one rather slow transfer of information subsequently results in many fast accesses to that information, with a net gain resulting from the clustering of memory references.\*

Assuming that memory references do cluster into natural page sizes of reasonable length, it can be deduced from the previous discussion that the fundamental, minimum functions necessary for a virtual memory system are as follows:

- 1. Page mapping function (Section 9.5).

- 2. Address translation (Section 9.6).

- a. Word addressing within a page.

- b. Page addressing within both primary and secondary storage.

- 3. Page replacement algorithm (Section 9.7).

In large, multiprogrammed systems, a number of additional practical functions are needed to produce a feasible, efficient system. Some important practical requirements in a multiuser system are as follows:

- a. I/O processor and technique for efficient page relocations.

- b. Storage protection.

- c. Sharing of pages.

When a required page is not in primary storage, the I/O processor finds and transfers the required page, allowing the CPU to transfer to a different user and continue processing. These overlapping functions combined with cycle stealing for data transfer (Section 9.2) greatly improve the CPU utiliza-

tion. Yet even without this, some advantage in efficiency over a nonvirtual system can result because of the clustering of memory references,\* but the main advantage would be the virtual addressing capability. This is the situation in some small, single user virtual system. In large, multiuser virtual systems, speed and system efficiency are important as well as virtual addressing capability.

The storage protection function ensures that any given page of memory is not inadvertently changed or removed, nor accessed by unauthorized users. In multiuser systems, sharing of pages that contain, for instance, the supervisory program, is highly desirable to conserve memory space. In data based systems, sharing of data between users with proper access rights becomes a fundamental necessity, but this represents a more complex system than that being considered here. In a simple, two-level, multiuser virtual hierarchy, the latter three optional features are of practical importance but are not fundamentally necessary—a workable, but perhaps inefficient system can be envisioned without them. The advantages of an I/O processor, detailed in Section 9.2, are valid here as well. Sharing of pages is a complex issue that is not considered.

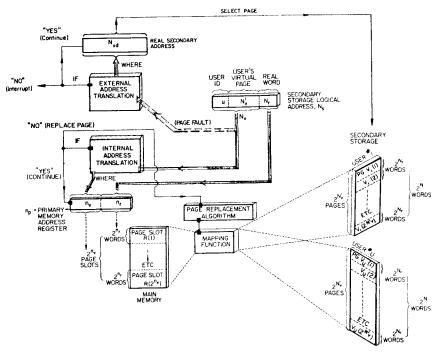

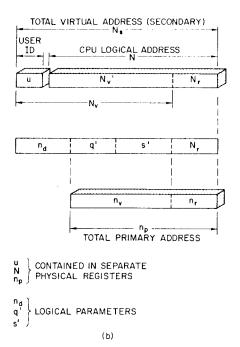

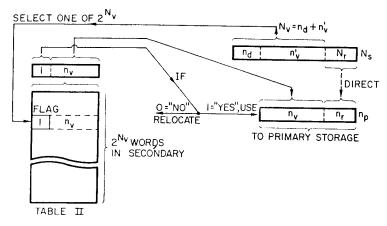

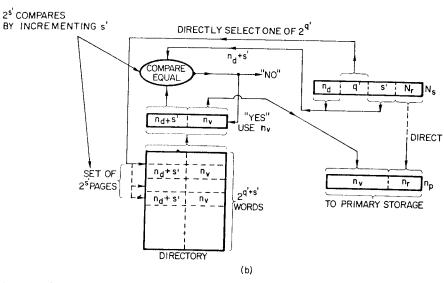

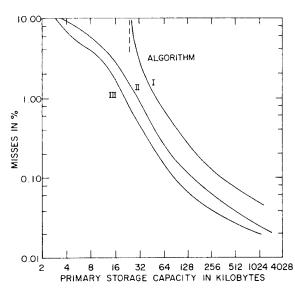

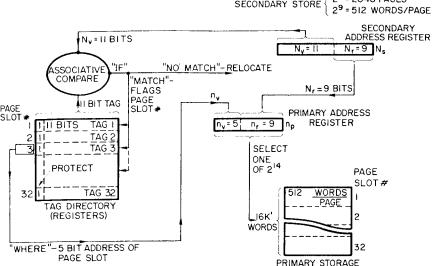

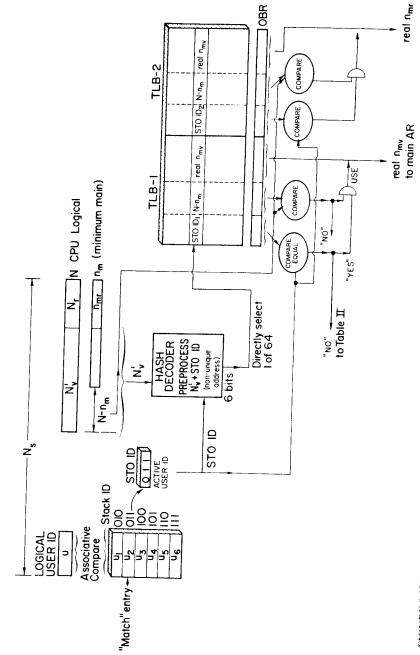

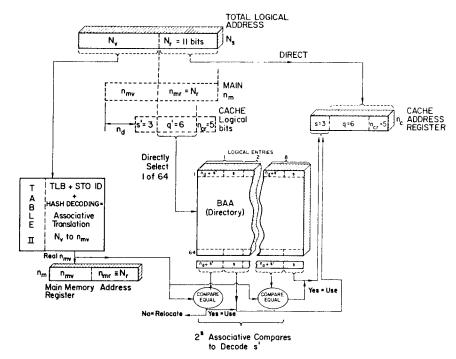

To better understand how the fundamental requirements interact, we now discuss a large, multiuser virtual system consisting of a disk as secondary storage and main memory as primary storage. We consider only a multiple virtual address space system: a single virtual address space is fundamentally no different and is just a simpler, limiting case.† The total logical address that addresses secondary storage consists of  $N_s$  bits, of which u bits are the user identification bits. These  $N_s$  bits can be contained in one or several registers within the CPU—typically, several are used. Each page is divided into  $2^{N_r}$  words or bytes, where  $N_r$  represents the lowest order address bits (Fig. 9.3-1). The total number of pages in the virtual disk storage is thus  $2^{N_s}$ , where

$$N_r = N_s - N_r (9.3-1)$$

Since the number of users U must be

$$U = 2^{u} (9.3-2)$$

from: Richard Matick, BM

<sup>\*</sup> In this case "memory references" means both program instructions and the actual alphanumeric data processed.

<sup>\*</sup> The main advantage is the saving in multiple access times. A nonvirtual system with improper memory segmentation may require numerous accesses to the disk for the same number of words processed, whereas a virtual system may use only one or a few accesses. The clustering of subsequent memory references to pages already present eliminates a large number of disk accesses but not the data transfer time.

<sup>†</sup> In practical terms, a single virtual space system does not have a separate user ID register (Fig. 9.5-2*b* and Fig. 9.8-2). Rather, the *u* bits are contained within  $N_i$  so each user has a virtual address space which is smaller than the total CPU address  $N_i$  but this can still be larger than the actual main memory address  $n_p$ .

FIGURE 9.3-1 Definitions of address bits in primary and secondary addresses.

each user has a total virtual storage capacity of

$$pages/user = 2^{N_r} (9.3-3)$$

where  $N_r' = N_r - u = N_s - u - N_r$ , as shown schematically in Fig. 9.3-1. This is equivalent to N address bits per user, where N is the standard address length of the CPU as given by column 7 of Table 1.1-1. For instance, on the IBM systems 360/370, N = 24 bits and the additional user address bits u are contained in a special register (see Section 9.9). Primary storage is addressed by  $n_p$  bits, where

$$n_p < N_s \tag{9.3-4}$$

Hence it can hold only  $2^{n_p}$  words, which is normally considerably less than  $2^{N_s}$ . Since pages are of fixed size.

$$n_{\rm v} = n_{\rm p} - n_{\rm r} \tag{9.3-6}$$

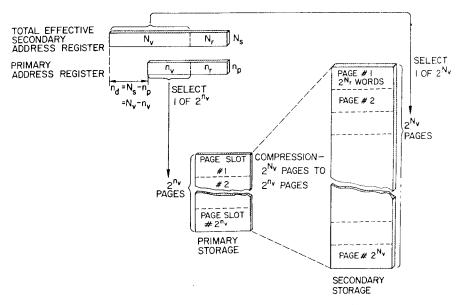

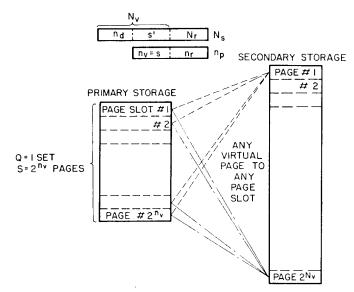

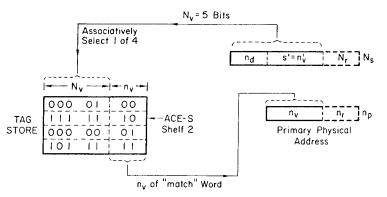

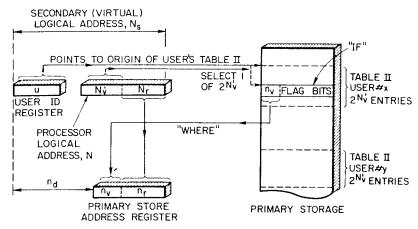

The CPU can reference pages through main memory only. Since in principle all  $2^{N_v}$  pages must eventually be referenced by the CPU, the page slots in main memory must be shared by many virtual pages, at different times, of course. The mapping of this large number of virtual pages into a smaller number of page slots is performed by the mapping function (Section 9.5) as indicated schematically in Fig. 9.3-2.

The addressing of such a system is considerably more complex than for an ordinary memory. Each of the  $N_s$  bit combinations represents a unique word in the virtual disk store therefore all these bits *must* be used to address main memory. However the main memory address register can only hold  $n_p$ , giving a deficiency of

$$n_d = N_s - n_n \text{ bits} ag{9.3-7}$$

FIGURE 9.3-2 Schematic of basic functional requirements in multiuser virtual memory system, showing information flow during translation of virtual address to primary memory address.

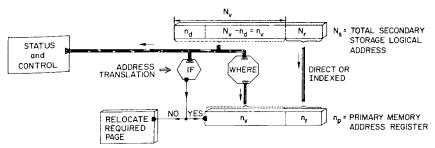

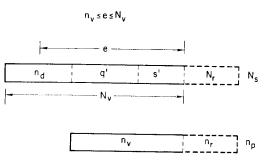

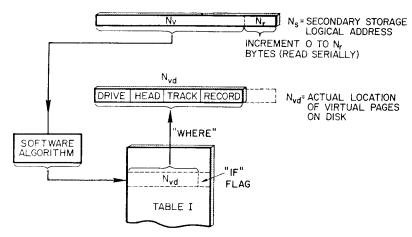

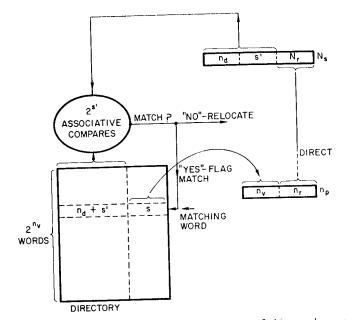

as in Fig. 9.3-1. These deficient bits must be used in addressing main memory, hence this number of bits (but not necessarily these bit positions) must be decoded externally. The words or bytes within a page are addressed by the lowest order address bits, denoted as  $N_r$  in Fig. 9.3-1. These bits are real and convert directly to  $n_r$  in the primary address register (Fig. 9.3-1 or 9.3-2).\* Since many virtual pages can occupy that same page slot, the remaining  $N_r$  bits must be used to indicate IF and WHERE the desired page resides in main memory. The various parts of the address translation are shown in Fig. 9.3-3. When the IF part produces a "yes," the address residing in the primary address register is used. When a "no" answer is obtained from the IF part, that page does not reside in main memory and a page relocation is necessary. The address that appears in the primary address register is aborted.

<sup>\*</sup> These bits may be added to the contents of an index or base register but nevertheless are converted directly to the real address.

**FIGURE 9.3-3** Schematic of translation of virtual logical address  $N_s$  into primary address showing IF, WHERE, and DIRECT components.

and now the  $N_s$  bits must be converted to the disk (secondary) address in Fig. 9.3-2. A separate external address translation function must be invoked which, as before, provides an IF and a WHERE. When the IF is "yes," the WHERE address is valid. When the IF is "no," that virtual page is not present in the secondary store and a program interrupt is generated. The WHERE function converts the virtual page address  $N_r$  into a real disk page address  $N_{rd}$ . In principle  $N_{rd}$  represents the same number of bits as  $N_r$ ; hence any of the  $2^{N_t}$  pages of any user can be accessed in secondary storage. Since all words of a page are transferred, the real address bits  $N_r$  are incremented by either hardware or software from zero to  $N_r$ , and the translation must be concerned only with the page address bits  $N_r$  as shown.

When main memory is full, it is necessary to remove one page before a new one can be entered. The page replacement algorithm keeps track of page usage in main memory and decides which page is expendable on request for a new page not present. If this expendable page has been modified, it is transferred back to disk, and only afterward can the new page be transferred. These three fundamental requirements are represented in block diagram form in Fig. 9.3-2 with only some lines of communication and control included. In actual implementation, these functions do not necessarily divide into convenient, separate pieces but often are closely interleaved. The address translation function has two major, separate components: to convert  $N_s$ into  $n_n$  if that page is resident in main memory; or, when a page fault is obtained, to convert N<sub>c</sub> into a disk address. Each of these translations can be done in several fundamental ways, as we see later. The integration of these functions into a system can take various forms as detailed in Sections 9.8 through 9.11. In large multiprogrammed systems, additional status and control functions are often included to indicate whether pages have been changed, to control each user's access rights and sharing of pages, and to implement other practical concerns.

In summary, we can state that the basic functions of Fig. 9.3-2 are necessary and sufficient to make a virtual memory work in a logical sense. From a practical point of view, however, data clustering is needed to make the system efficient. If references to primary storage physical locations occurred in a purely random fashion, page swapping between secondary and primary storage would occur very frequently, greatly reducing the overall system efficiency. Fortunately references to memory locations do not occur at random but cluster into groups called pages. The clustering is not precise, hence page size varies with the miss ratio required, size of primary storage, and other factors. This subject is covered in detail in Section 9.4. Thus the functions in Fig. 9.3-2 are those required to make virtual addressing logically feasible; overlaid on these is the phenomenon of data clustering, which makes the virtual memory economically feasible.

#### 9.4 DATA CLUSTERING, PAGING, AND HIT RATIO

As was mentioned briefly in Section 9.1, early commercial virtual memory systems were dominated by the use of segments of variable size. This approach evolved because in the early storage hierarchies, where program segments were overlaid into main memory, the segments always appeared in widely varying sizes. In fact, the natural length varied with the problem as well as with the programmer. Thus it seemed natural for a virtual system to allow for variation if efficient operation was to be obtained. Later, however, this notion proved to be incorrect. Though the natural segment length does indeed vary, allowing for this in any memory allocation procedure leads to gross inefficiencies. A number of small, fixed size pages can approximate any segment, and since the memory allocation procedure is much simpler, considerable improvement in overall efficiency can be obtained. The fundamental problem with segmentation is that it requires contiguous words in primary storage and the segments may be of varying size.\* A request for transfer of a segment into primary memory requires locating an empty region of the proper size. The empty regions may not singly be large enough. even though their sum may be more than sufficient. Since they are not contiguous, however, they cannot be used, and on a statistical basis, many regions of primary storage may remain unused. In a paged system with fixed page sizes, transferring a page only requires finding or creating an empty page slot in primary storage. This is considerably easier than finding or creating

<sup>\*</sup> Contiguous words are required just as for a page in Section 9.3, since the word within a segment is obtained by catenating the lower order real address bits to the higher order segment address bits.

present in primary storage for many different user programs. Each program is a maximum of 32 pages total size, each page containing 1024 words. The results for the particular set of programs indicate that relatively few pages can give a rather small miss ratio. Four pages result in about a 1% miss ratio, whereas 10 pages can reduce this by 2 orders of magnitude. The conclusion is that relatively few pages of a user's program are required to achieve reasonable miss ratios.

#### 9.5 MAPPING FUNCTIONS

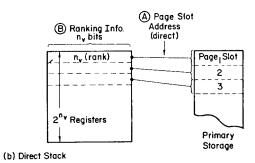

The secondary or virtual store contains a large number of pages that must be mapped or compressed into a smaller number of page slots in primary storage. The mapping function, requirement 1 in Section 9.3, specifies how this mapping is to be done. We consider the various mapping techniques in their general, fundamental form and derive relationships that are useful latter. The mapping function has a very significant effect on the address translation.

In practice, mapping functions are considered in four distinct groups (Conti, 1969): direct, sector, set associative, and fully associative. Fundamentally, they form a continuum of set associative organizations, with the direct and fully associative being two extremes and sectoring a special case.

A point of confusion often arises in understanding mapping functions because the mapping functions are only logical concepts that impart overall organization to the page mapping schemes. A given mapping function can be implemented in different ways and when implemented, it becomes part of the address translation function. These logical concepts can be used to visualize the mapping of logical to logical addresses, or logical address to physical address. The precise meaning of this and its consequences are discussed later in this section. First we deal with the general forms of logical mapping functions, assuming that the page slot allocations and relationships to follow are done in terms of *logical* structure without necessarily requiring the same *physical* structure.

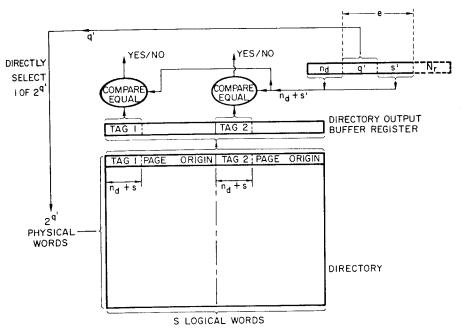

Following the nomenclature in Section 9.3 and Figs. 9.3-1 through 9.3-3. secondary store contains a maximum of  $2^{N_r}$  pages, each of  $2^{N_r}$  words, whereas primary storage contains only  $2^{n_r}$  pages of the same size. The primary address register has a deficiency of bits equal to  $n_d$  given by (9.3-7) as in Fig. 9.3-1. Since  $2^{n_r} \ll 2^{N_r}$  as in Fig. 9.5-1, it is necessary to specify how this compression or mapping is to be done. Any page slot in primary storage must hold many different virtual pages, but at different times of course. The actual number of virtual pages that a logical page slot must accommodate varies with the mapping function: the minimum number, however, is the total

**FIGURE 9.5-1** Compression of secondary pages into primary page slots with associated address bits.

page capacity of secondary divided by the total page capacity of primary storage or

$$\frac{\text{minimum number of pages}}{\text{logical page slot}} = \frac{2^{N_v}}{2^{n_v}} = 2^{N_v - n_v} = 2^{n_d}$$

(9.5-1)

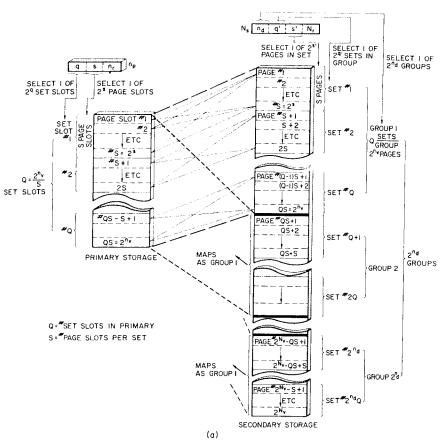

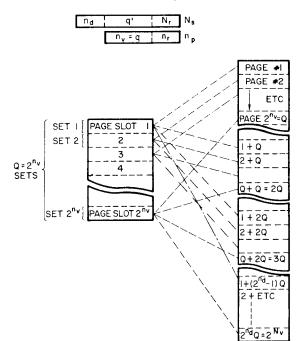

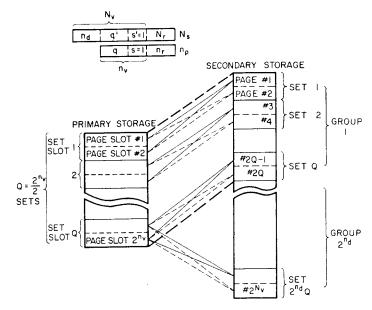

Thus the minimum number is determined by the deficient bits  $n_d$ . The maximum number is the total page capacity of secondary storage, or  $2^{N_v}$ . These two cases represent the extremes of direct and associative mapping, respectively. Between these two limiting cases are any number of possibilities. In a more general form, we can allow a virtual page from secondary storage to reside in any of S page slots in primary storage as in Fig. 9.5-2a. These S page slots form a set, and the mapping is the general form of set associative. There are obviously  $2^{n_v}$  total slots; hence the number of possible sets in primary storage is

$$Q = \frac{2^{n_v}}{S} = \frac{2^{n_v}}{2^s} = 2^{n_v - s} = 2^q \text{ sets}$$

(9.5-2)

where

$$q = n_r - s \tag{9.5-3}$$

$$S = 2^s \tag{9.5-4}$$

FIGURE 9.5-2 (a) General format for mapping secondary to primary storage.

But there are  $2^{N_c}$  virtual pages that must be accommodated in  $2^{n_c}$  page slots. The easiest way to visualize how this might be done is to think of secondary storage as being logically divided into groups of pages, each group of length equal to that of primary storage or  $2^{n_c}$  page slots. Each group contains Q sets and each set contains S pages. Each set slot in primary storage must be shared by the  $Q^{th}$  set in secondary storage. Thus set slot 1 is shared by sets 1,  $1+Q,\ldots,2^{n_d}$ . Likewise set slot Q in shared by sets  $Q, Q, Q, Q, \ldots, 2^{n_d}Q$ . Pages within a set are associatively mapped into any of the S page slots. All virtual pages are thus assigned to one and only one logical set and can be located in any one of S specific page slots within that set. Sets from different groups can be intermixed within primary storage; therefore not all sets from one given group need be simultaneously resident in primary storage. We

FIGURE 9.5-2 (b) Relationship of physical and logical address bit parameters.

may have, for instance, sets 1 from several different groups resident in primary storage, which means that all these virtual pages would have the same q address bits but different  $n_d$  address bits.

One reason for such a seemingly complex allocation of pages is that knowledge of which logical set and group a page must occupy constitutes additional addressing information that is used by the address translation function. The total number of virtual pages that can possibly reside at different times in any given slot in primary storage is the total number of virtual pages  $2^{N_v}$  divided by the number of sets Q, or

$$\frac{\text{virtual pages}}{\text{logical page slot}} = \frac{2^{N_v}}{Q} = \frac{2^{N_v}}{2^q} = 2^{N_v - q}$$

(9.5-5)

But from (9.5-3),  $q = n_v - s$ ; thus substitution gives

$$\frac{\text{possible virtual pages}}{\text{logical page slot}} = 2^{N_v - (n_v - s)} = 2^{n_d + s}$$

(9.5-6)

$$= S2^{n_d} (9.5-7)$$

The logical level of organization in secondary storage of Fig. 9.5-2a starting from the lowest to the highest is thus  $2^{N_r}$  words per page,  $S = 2^s$  pages/set,  $Q = 2^q$  sets/group, and  $2^{na}$  groups total. The analogous hierarchy in primary storage is  $2^{n_r}$  words/page,  $S = 2^s$  page slots/set, and Q set slots/primary storage.

When the physical locations of sets in primary storage are fixed to be equivalent to the logical locations, the word "logical" can be replaced by "physical" in all the above expressions. In the more general case, logical and physical allocations are not equivalent. In the most flexible case, any virtual page can reside anywhere in primary storage, irrespective of the logical structure of the mapping function. In such a case, the total possible virtual pages per physical page slot is the total number of possible virtual pages. Thus for the general case,

$$\frac{\text{possible virtual pages}}{\text{physical page slot}} = 2^{N_v} = 2^{n_d + s + q}$$

(9.5-8)

These relationships are important in the address translation process. The smaller the number of slots S per set, or the larger Q, the fewer logical places a page can reside and the easier it will be to find. Likewise larger values of S or smaller Q allow more possible slots per virtual page, and the more difficult the page will be to find. Thus one factor in the selection of a mapping function is the effect on the address translation.

Also important in the choice of a mapping function is the primary slot contention problem. In any mapping scheme, all the virtual pages required for a given problem can, statistically, reside in the same set, and the number of required pages might exceed the size of that set. Thus contention problems between two or more pages for unavailable slots can result in a large miss ratio for that problem, which is undesirable. The probability of contention problems, of course, varies with the number of page slots per set S.

The various distinct types of mapping function can be obtained by varying the value of S. Fully associative mapping results when S is its maximum value of  $2^{n_t}$  and Q is its minimum value of 1. Direct mapping is just the opposite, resulting when S is its minimum value of 1 or S = 0 and  $Q = 2^{n_t}$ . Set associative occurs for any values of S and Q between these extremes. Sector mapping is just a special case of fully associative mapping with the page enlarged to encompass many pages, called sectors. Thus it is apparent that the address parameters Q and S are logical entities that can be selected by the designer. They can be taken from the physical address registers, and the value of each is determined by the arrangement of the physical wires connecting the registers. The relationship between the various physical and logical address bits is shown in Fig. 9.5-2b. Each of the mapping functions is now considered separately.

**FIGURE 9.5-3** Schematic of fully associative mapping:  $S = 2^{n_t}$  page slots set:  $s = n_t$ , Q = 1, q = 0.

## 9.5.1 Fully Associative Mapping: $S = 2^{n_v}$ , Q = 1, $s = n_v$ , q = 0

If we allow S to become its maximum value of  $2^{n_i}$ , there can only be one set in primary storage (i.e., Q=1). Under these circumstances, any virtual page can be mapped logically into any page slot, and the mapping becomes fully associative (Fig. 9.5-3). This mapping is the most general and provides the minimum probability for page slot contention problems. Two virtual pages can contend for a page slot only when the pages required simultaneously for a given problem exceeds  $2^{n_i}$ , which is most unlikely. Hence fully associative mapping provides the largest hit ratio for a given problem on a given virtual system and is the most desired mapping function. However an associative type of compare is required in the address translation (Section 9.6), making this the most difficult mapping function to implement.

**9.5.2** Direct Mapping:

$$S = 1$$

,  $Q = 2^{n_v}$ ,  $s = 0$ ,  $q = n_v$

One way to completely avoid associative searching and greatly simplify the address translation is to let S = 1, giving only one page slot per set. This is referred to as direct mapping, illustrated in Fig. 9.5-4. Any given page in secondary storage can reside logically only in a specific page slot in primary storage. Using the rules previously described, the first logical page slot in

**FIGURE 9.5-4** Schematic of direct mapping; S = 1 page slot set;  $Q = 2^{n_0}$  sets, s = 0,  $q = n_1$ .

primary storage is assigned to hold virtual page 1, or 1 + Q, 1 + 2Q, ..., up to page  $1 + (2^{n_d} - 1)2^{n_v}$ . Likewise, the second page slot is assigned virtual pages 2, 2 + Q, 2 + 2Q, and so on, as shown, where  $Q = 2^{n_v}$ . When the logical and physical allocations are identical, primary storage will physically contain the pages as shown.

A serious disadvantage of direct mapping is the high probability of primary slot contention. For example, suppose a problem is being processed using arrays or matrices. If each array is in a separate page with array  $A_{ijk}$  in page 1 and array  $M_{ijk}$  in page 1 + Q, a problem of the form

$$\sum C_1 A_{ijk} + C_2 M_{ijk} = F_{ijk} \tag{9.5-9}$$

would require a transfer of one of the arrays for every evaluation of  $F_{ijk}$ , since both arrays are needed for each point. But only one of these arrays can be present in primary storage at any time, giving a low hit ratio and very inefficient operation. It could be argued that the data could, or should, be organized so that this does not happen. This is possible in principle, but it

**FIGURE 9.5-5** Schematic of set associative mapping showing 2 page slots set: S = 2, s = 1,  $Q = 2^{n_0}/2$ ,  $q = n_0 - 1$ .

is not always known beforehand how the data will be used. Even when known, such organization presents many formidable problems to the system allocation of storage, requiring "hand tuning" for efficient operation. Therefore direct mapping of the secondary to primary logical address space is never used.

#### 9.5.3 Set Associative Mapping

In fully associative mapping, the slot contention problem is minimized but the address translation problem is maximized. Direct mapping does just the opposite; contention problems are maximized and the address translation problem is minimized. Set associative mapping represents a compromise between these two. The general form is that of Fig. 9.5-2a. Some typical values are S=2 or 4 page slots per set. The case for S=2 is presented in Fig. 9.5-5. A virtual page can now reside in either of two logical page slots in primary storage. Hence the contention problem arising with direct mapping in solving (9.5-9) is eliminated. However other contention problems can and do arise. Larger values for S are desirable, when possible. A case for S=4 is described in Section 9.11.2.

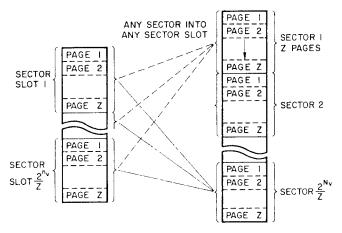

### 9.5.4 Sector Mapping

Sector mapping is a special case of fully associative mapping. In fact, if we ignore the labeling of what constitutes a page, the two are fundamentally identical. In practice there are some differences arising from the way the words are divided and decoded.

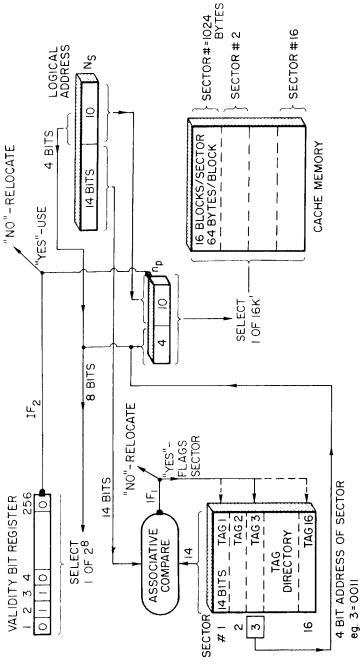

Sector mapping can be approached in two ways. The simplest method is to consider that the pages in Fig. 9.5-3 are increased in size to encompass many previous pages. If we wish to maintain our definition of a page (i.e., the number of words that is approximately the natural block size), we can just redefine the groupings. Instead of larger pages, we now define a sector to consist of several pages (Fig. 9.5-6). Both primary and secondary storage are broken into sectors of Z pages, and sectors are associatively mapped into primary storage. Obviously a sector of several natural pages has now taken the place of a single page in the fully associative mapping. All the previous rules pertaining to pages now apply to sectors. Note, however, that for a given physical implementation, the value of S, the number of page slots per set, takes on a slightly modified meaning and is reduced by the factor of 1 Z. In other words, the number of associative compares is now  $2^{n_r}/Z$ , since only the presence or absence of the sector is required. In practice, this has considerable merit to the extent that the number of sectors can be quite reasonable (e.g., 16); thus if tags are used for sector identification, the tags can be kept in a small associative memory that is very fast and not excessively expensive.

FIGURE 9.5-6 General form of sector mapping with Z pages per sector.

This sector technique using tags has been used with some modifications in the IBM system 360 model 85 cache. The essential idea remains the same – namely, to reduce the size of associative compare hardware while giving the flexibility of an associative mapping. The difficulty with this scheme is that Z must be reasonably large (16 or more), thus the number of sectors in primary storage becomes too small, resulting in a lower average hit ratio.

## 9.5.5 Logical versus Physical Address Space of Primary Storage

The mapping functions have been discussed in terms of secondary to primary logical address space, as previously indicated. The logical mapping represents the relationship between the symbolic addresses of page slots and can be done independently of any physical address mapping. The descriptions and figures require some conceptual representation of the primary page slots, and these might give the appearance of being the actual physical locations. Although this can indeed be the case, it need not be, and in general is not. The confusion between logical and physical mapping comes about because in our minds, we can picture page slots into which virtual pages may be placed, and they appear to have some physical relationship to other page slots. We can quickly address any specified page slot by visual inspection, and we tend to overlook the fact that we have performed a complex address translation function. Yet such a visual search is a sequential associative addressing function. In a computer, the same or other addressing operations can be performed but must be specifically implemented in hardware, just as our visual search is implemented with our eyes and the associative functions of the brain. Thus in our minds, the mapping function appears as though it were mapping secondary store to the physical primary page slots. But when we implement the mapping in the computer, we have removed the associative function provided by the human brain and must supply it in some other manner. This is then the primary logical to physical mapping, which is an essential part of the overall mapping function.

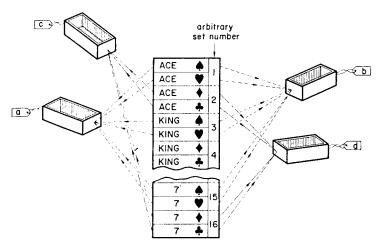

To understand the fundamentally important difference between logical versus physical address and mapping, let us consider the problem of mapping a deck of ordinary playing cards into a set of boxes. For simplicity, we assume that there are only four boxes into which cards can be placed. Also, since an ordinary deck of 52 cards is not a power of 2, we use only the highest 32 cards, from aces to sevens. The cards essentially represent the secondary virtual pages, and the boxes are the primary store page slots. The exact physical address of each box is in the item of importance ultimately, and this has not yet been specified. Let us "logically" label the boxes in some random fashion a, b, c, d by attaching tags (Fig. 9.5-7). The mapping is assumed to be set associative with s=1, which means that a given card can

**FIGURE 9.5-7** Logical mapping of cards into boxes for set associative mapping with s = 1 and four primary storage boxes.

reside in only one of two specifically labeled boxes as shown. For simplicity, we arrange the deck with the highest value card on top (ace of spades) and the lowest card on the bottom (seven of clubs). Since logical mapping is totally independent of physical address, it makes no difference which cards are mapped into which "logical" boxes, as long as we are consistent and obey the mapping rules. Thus we arrange the logical mapping so that the first set, consisting of the aces of spades and hearts, can reside only in the boxes tagged a and b: the second set, consisting of the aces of diamonds and clubs into boxes c and d; set 3, consisting of the kings of spades and hearts into boxes tagged a and b, and so on, similar to that in Fig. 9.5-2a. This information about how cards are mapped must be stored somewhere. In this very simple case, we may be able to remember the mapping, so it is stored in our brains. As a rule, however, the mapping is too complex to remember, therefore let us store this information on a sheet of paper (second, third, and fourth columns of Fig. 9.5-8a). To completely understand the mapping function and the kind of information that is required, we must attempt to find various cards in boxes, which invokes some address translation operations. However, we do these only in a very general way without specifying the actual implementation. Section 9.6 demonstrates the various ways in which the address translation function can be implemented in terms of the mapping information.

Continuing with the example, we specify that only one card may reside in a box at any one time and start moving the cards in random fashion into

|             | BINAF<br>Value                               | Suit                          | LOGIC |        | SET<br># | WHERE    | WHERE      | E ACTUAL | S — Spades<br>H — Hearts<br>D — Diamonds        |   |                   |          |

|-------------|----------------------------------------------|-------------------------------|-------|--------|----------|----------|------------|----------|-------------------------------------------------|---|-------------------|----------|

| 32<br>Cards | X <sub>5</sub> X <sub>4</sub> X <sub>3</sub> | X <sub>2</sub> X <sub>1</sub> |       |        |          | POSSIBLE | IF         | Tag      | C - Clubs                                       |   |                   |          |

|             | 111                                          | 11                            | ACE   | S<br>H | ı        | a- b     | Yes<br>No  | b        |                                                 |   |                   |          |

|             | 111                                          | 00                            |       | D<br>C | 2        | c-d      | No<br>No   |          |                                                 |   |                   |          |

|             | 110                                          | 11                            | KING  | S<br>H | 3        | a-b      |            |          |                                                 |   |                   |          |

|             | 110                                          | 00                            |       | D<br>C | 4        | c-d      |            |          |                                                 |   |                   |          |

|             | 101                                          | 10                            | QUEEN | S      | 5        | a-b      | Yes<br>No  | а        |                                                 |   |                   | W. 505   |

|             |                                              |                               |       | D      | 6        |          | No         |          | Ta                                              | g | PHYSICAL<br>Shelf | Binary   |

|             | letc.                                        |                               |       |        |          |          |            | WHE      | RE                                              | # | Address           |          |

|             | 000                                          | 11                            | 7     | S<br>H | 15       | a-b      | No<br>No   |          | а<br>ь                                          |   | 3<br>2            | 10       |

|             | 000                                          | 01                            |       | D      | 16       | c-d      | Yes<br>Yes | d<br>c   | c<br>d                                          |   | 0                 | 01<br>00 |

|             | (a) Logical Map of Cards to Tags [Map 2]     |                               |       |        |          |          | (b         | Ph       | imary Log<br>sysical Map<br>ven time<br>[Map 3] |   |                   |          |

FIGURE 9.5-8 Mapping information for cards in boxes

and out of the boxes. At any given instant of time, the four boxes contain four cards. We know from the mapping function which cards may be in which boxes, assuming no mistakes in the swapping process. Suppose that we wish to know IF and WHERE the ace of spades is residing in one of the boxes; a quick check on Fig. 9.5-8a shows that it is useless to look into boxes c and d. Hence we need to associatively search only boxes a and b. If this associative search fails to provide a match, the IF is a "no" and the WHERE is irrelevant. A "yes" match supplies the IF and WHERE directly. Only two associative searches are needed because the boxes are logically tagged and the tags are visible on the boxes. Suppose we remove the tags from the boxes so that the required mapping information is contained only on the piece of paper of Fig. 9.5-8. Since the boxes are identical, it may be difficult determining which two boxes to search for the ace of spades. But we remember that box a is on the lower left and box b on the upper right; thus we might search these boxes. However we have made a very important assumption, namely, that there is a "direct" relationship between the logical tags and physical location of the boxes; that is, the logical to physical mapping of the boxes (primary) is direct. If this relationship is true, our search is valid.

Suppose, however, that we rearranged the boxes in some random fashion as we swapped cards. Now with the logical tags on the piece of paper only, there is no way to find the physical location of the ace of spades except by a completely associative search of all four boxes. If we had provided some mapping of the logical tags to physical location of the boxes, only two associative searches would be needed to locate the ace of spades. For instance, suppose we keep the boxes on four shelves and specify that boxes a and b are always on the top two shelves and c and d are always on the bottom two shelves. Now there is no need to search the bottom two shelves, which makes the search simpler. This additional information about where the boxes physically reside must be stored somewhere (e.g., in the primary logical to physical mapping of Fig. 9.5-8b). There are various techniques for implementing this mapping, but then it becomes part of the address translation. The essential point is that in the most general sense, the secondary to primary mapping function is a logical map. When the physical position of the boxes is specified by the use of tags stored directly on the boxes, the logical map is directly converted into a physical map. When the tags are stored separately from the associated boxes, an indirect conversion to the physical location of each box is required. Both cases of directly or separately stored tags involve the use of an additional mapping of the logical tag to physical location of the box, the former represents direct mapping and the latter a form of associative mapping. In either case, this logical to physical map is a fundamental requirement.

The case of finding IF and WHERE the ace of spades might be in the boxes requires a minimum of two associative searches plus the second, third, and fourth columns of Fig. 9.5-8a and the map of Fig. 9.5-8b. It is possible to avoid associative searches completely by storing more information within the mapping tables. Suppose we provide a fifth column in Fig. 9.5-8a called "WHERE ACTUAL," specifying IF and WHERE any card actually resides logically within a box. Thus the ace of spades and three other cards have a "yes" for IF and a logical box location WHERE each is. The boxes logical to physical translation must make use of Fig. 9.5-8b as before. Thus the location of the ace of spades requires direct addressing only: a reference to its binary address, shown as 111-11 in Fig. 9.5-8a, yields "yes," "tag b" for IF and WHERE from the last column; an access to tag b in Fig. 9.5-8b yields shelf 2 (note that any of the four shelves just as easily could have been indicated here). The price we pay for the elimination of associative searches is the need for more stored mapping information.

In a completely analogous manner, we can show that the initial orientation of the entire deck of cards as in Fig. 9.5-7 is a logical orientation, and the initial selection of a physical card from the deck (secondary) before being placed in a box requires a mapping of the secondary logical to secondary

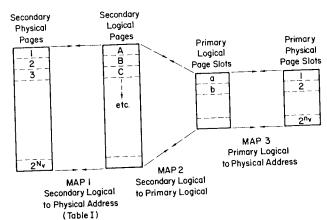

**FIGURE 9.5-9** Schematic of logical and physical address spaces showing three fundamental maps required for a two-level virtual memory hierarchy.

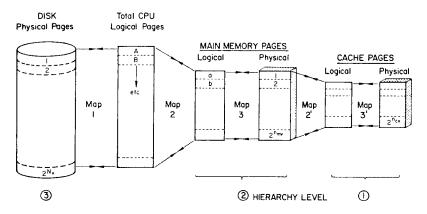

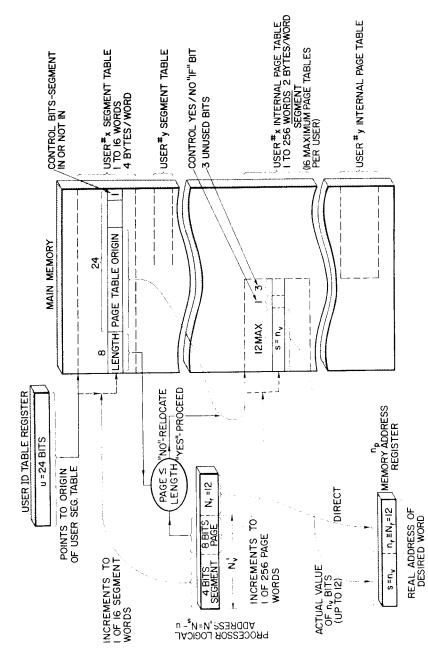

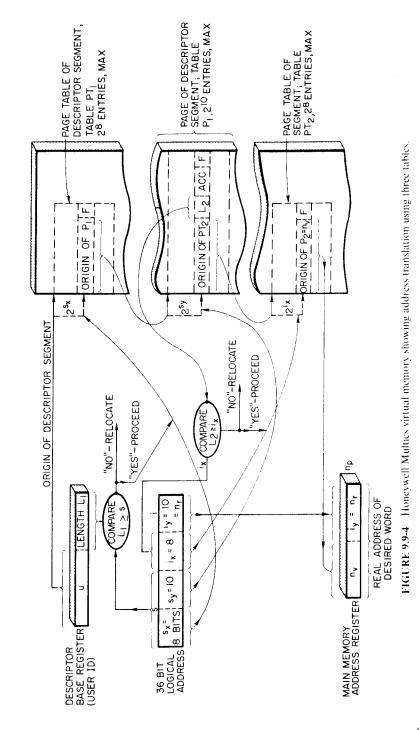

physical location. In other words, we picture the logical orientation of the cards as in Fig. 9.5-7, but given a shuffled deck, we would need a logical to physical mapping to find the ace of spades, and so on. Thus we can conclude that any two-level virtual hierarchy requires three mapping functions. One map is required for each level to map that level's logical to physical space, and one map is required between levels. Figure 9.5-9 shows these maps schematically for a disk-main memory type of two-level hierarchy. Map 1 is generally provided by Table I discussed in Section 9.8. In a cache-main memory type of two-level hierarchy without a disk-main hierarchy, there are no pages in the main memory that are visible to the user. The CPU (secondary) logical address is converted into a physical main memory address by the compiler, assembler, link editor, and so on; thus Map 1 in Fig. 9.5-9 is essentially a direct mapping in such a case. The internal memory physical pages are mapped into the logical cache pages with an analogous Map 2, and likewise the cache logical to physical mapping with an analogous Map 3.

In a three-level hierarchy, containing a disk-main virtual store and a main-cache hierarchy, the cache is paged out of main memory just as in the the two-level hierarchy. However additional mappings are obviously required. One logical to physical map for each level and one map between each level results in a minimum of five maps for this case. The disk and main memory mappings would be as indicated in Fig. 9.5-9, with disk being the secondary, the main memory the primary, and the total CPU logical address the equivalent to the "secondary logical pages." When a cache is inserted into

**FIGURE 9.5-10** Schematic of logical and physical address space showing various maps required for a typical three-level virtual memory hierarchy.

this system, its position in the mapping scheme must be determined. Fundamentally, the logical cache pages can be mapped into the cache starting from the CPU logical pages, from the main memory logical pages, or from main real (physical) pages. However since the CPU logical pages are so much more numerous, and since they must be mapped into the main memory logical space anyway, it is advantageous to start either with the main logical or physical pages. For various practical reasons, the latter are often used (see Section 9.12). The schematic of the various maps for such a case appears in Fig. 9.5-10. In all systems, Maps 2, 2', 3, and 3' are implemented as an integral part of the address translation function discussed in Section 9.6. All three maps can take on any of the possible forms discussed previously from direct to fully associative. The degree of associativity of one does not affect the associativity of the others, since each is completely independent.

Some of the important conclusions about mapping of physical secondary pages to physical primary pages in a two-level hierarchy can be summarized as follows.

- 1. Three mapping functions are a fundamental requirement.

- 2. Contention problems for primary page slots are determined only by the secondary logical to primary logical mapping function and become less severe as the degree of associativity 2<sup>s</sup> increases.

- 3. The mapping of primary logical to physical address has no bearing on the page slot contention problem: more generally, all three maps are independent of each other in principle.

## 9.6 ADDRESS TRANSLATION FOR A TWO-LEVEL VIRTUAL HIERARCHY

To understand virtual memory addressing, familiarity with the concepts and mapping functions discussed in Section 9.5 is imperative.

The functions performed by the address translation were outlined in Section 9.3. The N<sub>s</sub> bits must be converted into an IF and WHERE real address. As shown in Fig. 9.3-3, N<sub>r</sub> is directly translated, hence only the virtual page address  $N_{\rm r}$  need be considered. When the desired page happens to be resident in primary storage, the IF translation produces a "yes" and the correct, real  $n_0$  must be provided by the WHERE translation. This is essentially an implementation of Maps 2 and 3 of Fig. 9.5-9. When the desired page happens not to be resident in primary storage, the IF produces a "no" and the real address of that page in secondary storage must be found. This is an implementation of Map 1 of Fig. 9.5-9. In a two-level hierarchy, the conversion of  $N_n$  into  $n_n$  when the desired page happens to be resident (i.e., IF = "yes") becomes the critical factor in the overall speed of address translation. If the entire process is to run at an effectively fast cycle time, this part of the translation should not introduce excessively large delays. We concentrate mainly on this, the most important part of the translation function, and its associated Maps 2 and 3 of Fig. 9.5-9. We consider the various fundamental schemes in considerable detail and derive important tradeoffs and relationships.

### 9.6.1 Translation of Logical Address to Primary Storage Address

Irrespective of the mapping function used, the address translator must decode all  $N_{\rm r}$  bits of the secondary storage logical address. Only a WHERE function is performed in ordinary nonvirtual decoding, since in such cases each logical address has the same length as the primary memory address register and uniquely specifies a memory word. In virtual address decoding, the WHERE function is more complex and the additional IF function must be performed. More generally, ordinary nonvirtual decoding could be thought of as virtual decoding with the IF functions always set in the "yes" state. However the given nonvirtual address will always be unique and real, which allows for a simple implementation, since a one-to-one correspondence exists between the address and the physical location. In virtual addressing, this correspondence is lost. As indicated in the general mapping form of Fig. 9.5-2a, a given page slot in primary storage can contain different pages at different times. Although the virtual page address  $N_{\rm r}$  uniquely specifies the virtual page in secondary storage,  $N_{\rm r}$  by itself is not sufficient to specify

IF and WHERE that page resides in primary storage. Thus additional information must be stored in some manner to tell how the mapping is performed, and this constitutes the mapping function. The manner in which this information is stored and used constitutes the address translation function. A mapping function is only a conceptual, logical view of how page slots are to be shared, and when implemented, it becomes part of the address translation function. Clearly these two must work closely together. As previously indicated, we must implement both Maps 2 and 3 of Fig. 9.5-9 - the secondary to primary logical address map and the primary logical to physical address map. The address translation must provide the IF and WHERE for both maps. However the logical IF is easily converted into a physical IF (e.g., by the hard-wired "Yes/No" control line on the primary memory address register as in Fig. 9.3-2). There are numerous ways of implementing this conversion, but it is relatively straightforward, and we concentrate here on the fundamentals of the address translation function to provide the logical IF, logical WHERE, and physical WHERE. The exact form of the address translation function varies in a continuous manner from a pure table requiring look-up for each request, to a simple associative directory, assuming a general form of mapping as in Fig. 9.5-2a. With such a mapping function, some form of association must be established between the real and the virtual page, irrespective of the method of address translation. The table form of translation provides this association by storing the real location of every virtual page, hence requires considerable storage. The associative directory provides this association very directly but requires a great deal of associative logic. Between these two methods lies a continuum of translation techniques requiring varying amounts of storage and associative logic, as might be expected. In fact this represents the fundamental tradeoffs in the choice of an address translation function; the table look-up is relatively slow because the table is stored in primary memory and requires additional memory access. The directory is small, thus can be fast, but it is expensive because of the necessary associative hardware.

The example of placing cards in boxes in Section 9.5 did not specify the details of implementing the mapping function because it is carried out by the address translation function. To see the range of possible schemes, let us continue with the "cards in boxes" example and consider two possible approaches, representing the end points of a continuum. After the example, we investigate address translation in its general form and derive important relationships.

Section 9.5 partially described these two cases of a table and an associative directory, but without the details and some remaining important considerations. We already know that certain mapping information must be stored somewhere, the exact amount varying with the address translation scheme

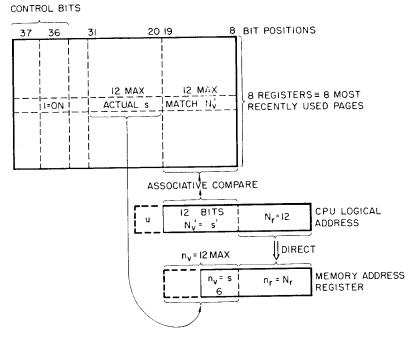

chosen. Let us store this information in a general random access memory called the "tag store" and see how much and what information it must actually contain. We arbitrarily define a table scheme as one for which no associative compares are needed and a directory as one for which associative compares are needed. If we are to avoid associative compares and use direct decoding instead, some form of Fig. 9.5-8a and b must be stored. We initially assume set associative mapping for both Maps 2 and 3. The tag store will have to contain at least one tag in the form of a table entry or word for each card. If we use a 5 bit address  $X_5, \ldots, X_1$  for each of the 32 cards, the logical name of each is replaced by an address of the tag store: hence the column labeled "Logical name" in Fig. 9.5-8a is unnecessary. To determine IF and WHERE a given card resides, the last column must be included. In addition, the information of Map 3, Fig. 9.5-8b, must somehow be incorporated. Note that the last column of Fig. 9.5-8a contains the logical tag for each of the four boxes and is redundant with the first column of Fig. 9.5-8b. Hence the physical WHERE of Map 3 can be included directly within the last column of Fig. 9.5-8a in place of the logical WHERE tag. This greatly simplifies both mapping information and address translation. Furthermore, since each of the four cards resident in a box now has the physical box location (i.e., shelf address) stored with its entry in the tag store, this address can be any of the four shelves within invoking any difficulties. Hence the box logical to physical mapping can be fully associative as easily as set associative, so the former is chosen. This does not necessarily have an effect on the secondary to primary logical Map 2. If the latter is set associative, we do not need to know where it possibly can reside for address translation because its address is already given by the physical WHERE. To swap a new card into a box, however, we would have to specify which logical boxes are permitted. But this is totally unnecessary: if the address translation does not need to know the set, we may as well make this mapping fully associative and eliminate the complexity of mapping and replacement. Thus columns 3 and 4 of Fig. 9.5-8a are unnecessary, leaving only the first column contained in the address decoding network of the tag store and the last column as the actual stored information. The IF function can be done with a one-bit logical operation called a flag. and the WHERE function must be able to specify at least one of  $2^{n_0}$  pages in primary storage, which requires  $n_e$  bits, or 2 in this case. The general form of this table (Fig. 9.6-1) represents that actually used, with some modification. in virtual memory systems as detailed in Section 9.9. The logical flag "IF." is shown converted to a physical IF by a direct enable input to the primary address decoder.

The associative directory can be approached in many different ways. If we study the table of Fig. 9.5-8a, we note that most of the entries contain "no" for the IF function. In fact, only four cards can ever be resident in a box:

FIGURE 9.6-1 Table address translation showing fully associative mapping for Maps 2 and 3.

thus it is necessary to store information about these four boxes only, which greatly reduces the size of the tag store. In other words, instead of storing information about each card, most of which is "no," we store information only about each box. The difficulty is that many different cards can reside in any given box, and although the required storage is reduced, the process of address translation becomes more complex.

We assume a fully associative mapping, giving  $s = n_c = 2$ . The tag store must now contain only one entry or word per box to implement Map 2. Since we do not know a priori the identity of the card in any box, this must be stored in the tag store word, which requires 5 bits of  $X_5, \ldots, X_1$ . This is equivalent to  $N_e$  or  $n_d + n_v$  bits, as is evident from Fig. 9.3-3 and 9.5-2b. To implement Map 3, we can do as previously with the table and store the real physical address of the box as part of the tag store word. The tag store then becomes a fully associatively addressed directory (Fig. 9.6-2). The 5 bit ID of each of the cards resident in a box would be stored in the  $N_r$  portion of each word. An associative match on each of these produces one "match" condition that is equivalent to IF = "yes," and the physical WHERE address of that box is the  $n_r$  portion of that match word. For instance, if we want to test for the ace of spades whose ID is 11111, each word of the tag store is matched against this ID. The second word in Fig. 9.6-2 will give a match, and the  $n_r$  portion indicates shelf 2 (binary 10), as originally indicated in Fig. 9.5-8. Thus Maps 2 and 3 are both contained in the directory, and both are fully associative in this example. The tag store is much smaller than previously with the table scheme, but now it must perform associative selection capabilities, which is more difficult.

FIGURE 9.6-2 Fully associative tag store (directory) for address translation.

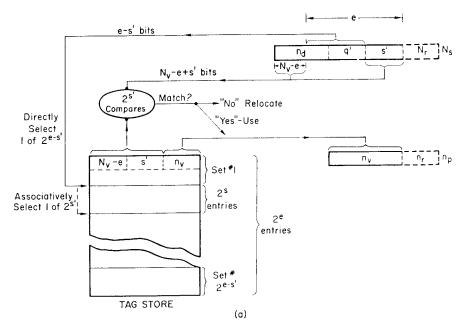

We now consider the address translation in its general form to see the "continuum" of schemes and subtle tradeoffs. Some profound conclusions that become evident are summarized later. For the general case, we assume the mapping to be the general set associative form of Fig. 9.5-2a. In our two specific examples of "cards in boxes," we saw that the amount and character of the additional stored information could vary considerably, depending on the implementation of the mapping function. Therefore let us assume that the required information is stored as 2e logical entries or words of as yet unspecified length, in some undefined tag store. These entries contain all tags and other information needed to implement Maps 2 and 3, as well as the address translation function. Let us first determine the bounds on the number of such logical entries, the amount of information that must be stored in each, and the various ways in which this information can be used to determine IF (logical) and WHERE (logical and physical) the real page exists in primary storage. We let e be some fraction of the total secondary virtual page bits as in Fig. 9.6-3, where the maximum value is  $e \le N_r$ . The minimum value for e can be deduced easily. Since there are  $2^{n_v}$  page slots in primary storage, it is necessary to store some information concerning at least each of these slots with one logical entry per page slot. Thus e must be at least as large as  $n_v$ , and the bounds on e are

$$N_{\rm p} \ge e \ge n_{\rm p} \tag{9.6-1}$$

Obviously the two previous cases of "cards in boxes" were the ends points  $e = N_r$  for the table and  $e = n_r$  for the directory. Let us now consider the various possible cases for some general value of e between the bounds of (9.6-1). First note that the associativity of the secondary logical to primary logical mapping functions, specified by s, can vary independent of e, that is,

**FIGURE 9.6-3** Relationship of tag store addressing bits e to the secondary and primary page-addressing bits  $N_v$  and  $n_v$ , for the general case.

any degree of associativity can be translated by any value of e satisfying (9.6-1). This is fundamentally true for the logical mapping, but the method of implementation forces certain relationships between e and s in terms of the number of bits that must be associatively compared. For the general case with  $e < N_v$ , the number of stored logical entries is less than one per virtual page by the amount  $2^{N_v-e}$ . To find IF and WHERE a given  $N_v$  address is resident in primary storage, this "unstored" information of length  $N_v-e$  bits must be stored in each logical entry. In addition, for a given mapping of associativity  $2^s$ , a required page might possibly reside in any of these  $2^s$  slots of a set. Hence s bits must also be stored in each logical entry of the tag store to assist in the logical IF and WHERE determination. Completing the search therefore requires

number of associative compares

$$= 2^s$$

(9.6-2)

number of bits/compare =

$$N_v - e + s$$

(9.6-3)

These fundamental requirements are valid irrespective of the primary logical to physical mapping or the remaining implementation. These associative compares provide only the logical IF and WHERE, the former signaled by a "yes/no" match condition. This can be easily converted to a physical IF by using a simple logic gate to activate or deactivate the primary address register as in Fig. 9.3-2. Other techniques are possible, but we assume the method just described in subsequent cases.

The primary logical to physical mapping (Map 3) can be done as previously, by storing the real address of length  $n_{\rm r}$  bits within each of the  $2^{\rm r}$  entries. As before, this makes Map 3 fully associative without affecting the overall address translation, irrespective of the value of s used in Map 2. We do not have to make Map 3 fully associative: if a set associative map of associativity  $S_2 = 2^{s_2}$  is used, only  $n_{\rm r} - s_2$  bits need be stored in this portion

of the tag store. Since this seldom saves many bits and greatly complicates the system, a fully associative Map 3 storing  $n_{\rm r}$  bits is typically used. A direct map could also be used, which would require no stored bits but only a direct *enable* or similar function on a page of a semiconductor chip (see Section 9.13). A direct map 3 becomes very important in one special case of a fully associative Map 2 as discussed later.

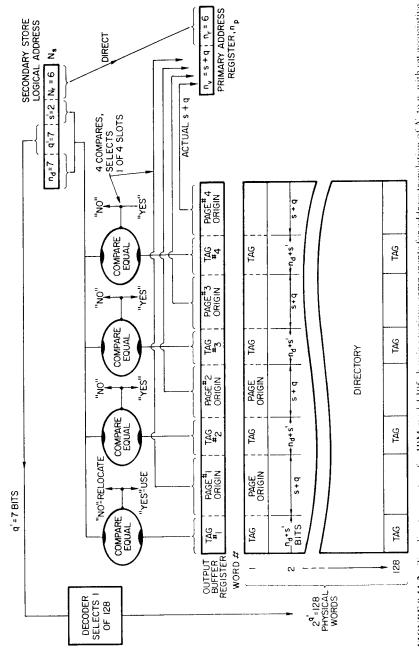

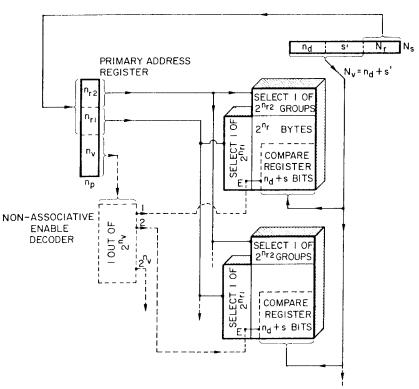

Now we have a tag store consisting of  $2^e$  entries or words, each storing  $N_v - e + s$  bits, which are associatively compared to provide the logical IF and WHERE for Map 2, and each contains also from 0 to  $n_r$  bits for Map 3 depending on the associativity of the latter. The general scheme is given in Fig. 9.6-4a, assuming that Map 3 is fully associative and Map 2 is of associativity  $2^s$ . Since at least  $2^s$  entries must be associatively addressed,  $2^{e-s}$  can be directly addressed. The address translation procedure would be as follows. For a given virtual page address  $N_r$ , the higher order bits  $e - s = n_d - (N_v - e) + q'$  are used to directly address one of the possible sets in the tag store; only  $2^q$  of these can have valid entries, since there are only  $2^q$  sets in primary storage. Comparison of the  $N_r - e + s$  bits stored within each of the  $2^s$  entries of the directly selected set with the same bit positions from  $N_r$  produces a "yes" or "no" match. If "yes," the  $n_r$  from the matched

**FIGURE 9.6-4** (a) General case of a tag store directory with  $2^{e}$  logical entries.

**FIGURE 9.6-4** (b) Example of minimum tag store directory implementing a set associative Map 2 and fully associative Map 3 showing 2' sequential compares.

entry provides the real WHERE address for the primary store address register as shown. In this case, the tag store must be accessed first to find the real  $n_v$  and subsequently the primary store is accessed using  $n_v + n_r$  to obtained the desired byte or word. A specific example for  $e = n_v$ , set associative Map 2 and fully associative Map 3 appears in Fig. 9.6-4b.

A fundamental relationship of considerable importance is the total number of possible pages in secondary storage that share the same logical set in the tag store. This is simply the total number of secondary pages divided by the number of logical sets in the tag store, or

secondary pages sharing each tag store set =

$$\frac{2^{N_v}}{2^{e-s}} = 2^{N_v - e + s}$$

(9.6-4)

This relation is used later to obtain a number of important conclusions about the tag store.

## 9.6.2 Special Cases of the Tag Store

We should be able to obtain previous examples of the table and fully associative directory from this general scheme by letting e take on the values  $N_{\rm r}$  and  $n_{\rm r}$ , respectively. Let us try these to see some important consequences.

## CASE 1

When  $e = N_v$  and s > 0, the tag store contains  $2^{N_v}$  entries. Following the general operation already given, a search requires a direct decoding to one out of  $2^{e-s}$  or  $2^{N_v-s}$  entries, and  $2^s$  associative compares on  $N_v - e + s = s$  bits. The result of a correct match must produce  $n_v$  bits for the real page address, assuming Map 3 to be fully associative.

Equation 9.6-4 indicates that the total number of possible secondary pages sharing the same logical set in the tag store is  $2^s$  pages. But since this is also the maximum number of logical page slots in a set, any number of pages of any mix can be accommodated simultaneously in the tag store. Hence the logical mapping is fully associative for any value of s in this special case. Let us choose s = 0, to permit the number of associative compares to reduce to  $2^0 = 1$ , and the number of bits to be compared to reduce to zero. This results in a direct decoding to one of  $2^{N_v}$  or the entire table, storage of  $n_v$  real address bits, and one associative compare over zero bits. The latter represents the degenerate case of merely specifying whether that page is resident. It could be done by performing a logical check on whether an  $n_v$  address is present. It is simpler to provide a one-bit logical flag; hence we have reduced the tag store to the previous table scheme.

#### CASE 2

When  $e = n_v$  and s > 0, the tag store contains  $2^{n_v}$  entries. A search requires a direct selection of one of  $2^{v-s} = 2^{n_v-s}$ ,  $2^s$  associative compares on  $N_v - n_v + s = n_d + s$  bits, and a match must produce the real  $n_v$  bits. This is a specific case of a set associative directory such as that in Fig. 9.6-4b. If we let  $s = n_v$ , the direct selection of one of  $2^{n_v-s}$  reduces to zero and  $2^{n_v}$  associative compares are required on  $n_d + s = n_d + n_v = N_v$  bits. This is the fully associative directory previously discussed.

A fundamental conclusion of profound consequences is that the associativity of the secondary to primary logical mapping, Map 2, provided by a general tag store, hence the required number of associative compares, is fixed at  $2^s$  for all values of e except for the special case of the table where  $e = N_v$ . The fundamental reason for this follows very directly from (9.6-4) and results from contention problems for logical page slots. Even when the real primary store is not full, contention problems can arise because the pages required simultaneously might happen to be all from the same logical set, and the number required might be greater than  $2^s$ . For instance, for any tag store with  $N_v - e \ge 1$  or  $e \le N_v - 1$ , the number of secondary pages sharing a logical set, given by (9.6-4), is obviously greater than  $2^s$ . But by chance, this larger number could be needed simultaneously in that logical set, whereas only  $2^s$  can be accommodated within the tag store (i.e., the

degree of associativity is 2s). Hence a new contention problem may arise within the tag store even though the primary store has empty page slots. Set associative mapping, therefore, introduces a second kind of contention problem, one for tag store space, in addition to the ordinary contention arising because the primary store is smaller than secondary storage. We did not have this contention problem in the special case of  $e = N_r$  because as previously discussed, the maximum number of secondary pages sharing a logical set is 2s, which exactly equals that which can be accommodated. Hence except for the special case, the associativity of the general tag store with  $2^e$  entries is determined only by s.

The above conclusion raises the question, What properties of the address translation are affected by changing e? As the number of entries e varies, only the number of bits that must be associatively decoded varies as

$$N_v - e + s \tag{9.6-5}$$

As e increases, the number of bits associatively compared decreases, and vice versa, Thus we merely trade the number of tag store entries for word size and associative bits compared. The minimum number of bits required in any tag store scheme is just the number of logical entries times the number of bits per entry. These various expressions and other important relations are summarized in Fig. 9.6-5 for the general case, the table, and the minimum sized directory. The table can require considerably more storage than the minimum directory. The ratio of total storage capacity for these two (from Fig. 9.6-5, assuming Map 3 to be fully associative) is

bit capacity

$$\frac{\text{table}}{\text{directory}} = \frac{(1 + n_v)2^{N_v}}{(n_d + s + n_v)2^{n_v}} = \frac{1 + n_v}{N_v + s} 2^{n_d}$$

(9.6-6)

Some typical values might be

$$N_v = 18$$

,  $n_v = 6$ ,  $s = 2 (q = 4)$ ,  $n_d = 12$

Substitution of these into (9.6-6) gives the ratio as  $0.35 \times 2^{12} = 1434$ , a substantial difference showing the value of the minimum directory. However we have said little about the hardware characteristics of the tag store for each case. Typically for the table implementation, the tag store uses primary (main) memory, since only random access addressing is required and the table can become quite large. A fundamental requirement of this table is that the entries be logically contiguous, since successive binary values of  $N_r$  refer to successive logical entries in the table. Thus even if many entries are blank, they cannot be removed from the table to make the table shorter.\* The table

| TAG STORE<br>Description                       |                  | ENTRIES                                      | DECODED         | NUMBER BITS<br>COMPARED<br>ASSOCIATIVELY | BITS PE            | NUMBER<br>R ENTRY<br>Map 3 |                                                     |

|------------------------------------------------|------------------|----------------------------------------------|-----------------|------------------------------------------|--------------------|----------------------------|-----------------------------------------------------|

| A. General<br>TAG STORE                        | 2 <sup>e</sup> * | 2 <sup>e-s</sup>                             | 2 <sup>s</sup>  | N <sub>v</sub> -e+s                      | N <sub>v</sub> e+s | O to n <sub>v</sub>        | (N <sub>v</sub> -e+s+n <sub>v</sub> )2 <sup>e</sup> |

| B. Minimum TAG<br>STORE<br>(e=n <sub>v</sub> ) | 2 <b>n</b> v*    | 2 <sup>n<sub>v</sub>-s</sup> =2 <sup>q</sup> | 2 <sup>\$</sup> | n <sub>d</sub> +s                        | n <sub>d</sub> +s  | O to n <sub>v</sub>        | (N <sub>v</sub> + s)2 <sup>n<sub>v</sub></sup>      |

| C. TABLE<br>(e=N <sub>v</sub> )                | 2 <sup>N</sup> v | 2 <sup>N</sup> v                             | 0               | 0                                        | <br>               | O to n <sub>v</sub>        | (1+n <sub>v</sub> )2 <sup>N</sup> v                 |

- \* Can be 2<sup>e-s</sup> physical words see section 9.12

- ≠ Assuming Map 3 = n<sub>v</sub> & excluding control bits

FIGURE 9.6-5 Comparison of tag store characteristics for different implementations.

must contain one entry for each possible logical (virtual) page. A method for reducing the amount of this table that must be stored in primary memory is described in Section 9.8, and examples are given in Section 9.9. For the minimum directory implementation, the tag store is usually a separate random access memory because of the required associative compares. Further discussions concerning the various design considerations are given in Sections 9.8 and 9.10.

It is clear that the choice of mapping function has a significant effect on the method of address translation. This effect can be linked to a telephone directory in which names are listed in various ways. If we assume that no two names are identical, a purely alphabetical listing is like direct mapping: there is one and only one possible logical position for each unique name, and it is easily found. If the listing is purely random or has no structure, this is comparable to fully associative mapping and requires the capability for an associative search on every name, to be able to find the final phone number. Set associative mapping would be analogous to listing together all names say, starting with A, then all those starting with B, etc., but no order within the A's or B's, etc. Hence the number of associative searches equals the number of names under the letter of interest, which is identical to the number S of possible logical names per set.

In all the above examples we have emphasized the use of fully associative mapping for the primary logical to physical Map 3, even though in principle, direct or set associative mapping can be used. The reason is practical in that a direct or set associative Map 3 would involve additional complexity in the actual page swapping and would greatly limit the ability to incorporate operating systems and memory expansion. Thus a fully associative Map 3 is

<sup>\*</sup> Except for the rare case that all entires above a certain binary address are blank or the user requests a smaller total number of pages, which automatically makes the table smaller

most desirable. A very special and important case arises in which this Map 3 has the appearance of being fully associative even though it is a direct mapping, in fact can be a hard-wired direct mapping. This situation occurs when the secondary to primary logical mapping (Map 2) is fully associative; that is,  $s = n_r$ . In such a case, any virtual page can reside in any logical page slot. If a direct Map 3 is used, logical and physical page slots become identical. Now, any virtual page can reside in any physical page slot as desired, and Map 3 has no effect on this capability. This principle is discussed more fully in Section 9.13 with example.

Some important conclusions about address translation are as follows.

- 1. The address translation function cannot be implemented without including the mapping function for both Maps 2 and 3.

- 2. Translation schemes form a continuum of tag stores of varying number of entries e, with the table and minimum directory at the two extremes for e equal to  $N_v$  and  $n_v$ , respectively.

- 3. Any secondary to primary logical mapping with associativity of degree  $2^s$  must perform  $2^s$  associative compares on  $N_r - e + s$  bits: a special case occurs for  $e = N_r$ , which yields a table of any degree of associativity.

- 4. Increasing the number of entries e in the tag store only reduces the number of bits that must be associatively compared; it does not change the required number of such compares.

- 5. Implementation of the logical to physical IF function is very simple.

- 6. Implementation of the primary logical to physical WHERE map is much easier than the secondary logical to primary logical WHERE map, and the former can typically be fully associative as easily as any other mapping.

- 7. When the secondary logical to primary logical mapping function is fully associative, the primary logical to physical map can be direct while giving the appearance of being fully associative in the sense that complete freedom is provided for the physical location of any page in the primary store. This is a special case.

Fundamentally, the address translation function is required only to perform the IF and WHERE translation of virtual to real pages. In practical systems it is also desirable to provide a certain amount of "status and control" information. For instance, if no changes (i.e., no writing) have been made within a given page, it can be erased when it is to be swapped out of primary memory. In addition, storage protection in the form of access rights can be implemented within the address translation function if desired. Additional information stored within the previous necessary logical entries of the tag store can control access and sharing of pages among various users. Examples

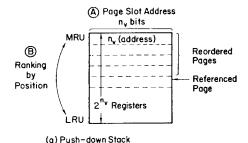

### Replacement Algorithms and Implementation

are given in Section 9.9. When the address translation is accomplished with a directory, the need for speed dictates that the information for the replacement algorithm be contained within the logical entries or an equivalent hardware scheme (see Section 9.7). Thus the various schemes for storing the additional information for address translation sometimes contain status and control information in addition to the IF and WHERE information.

## REPLACEMENT ALGORITHMS AND IMPLEMENTATION

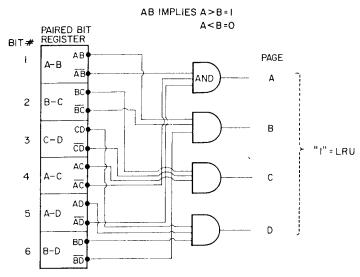

Replacement algorithms can be placed arbitrarily into two broad categories: (a) algorithms that do not use historical information to determine which page to remove from primary, and (b) algorithms that do use historical information for replacement.

The first category does not require storing any information about page referencing, hence essentially includes random or near-random replacement algorithms. The second category requires storage of some kind of information about page referencing, depending on the exact nature of the algorithm. This represents the bulk of algorithms-first in, first out (FIFO), least recently used (LRU), least frequency used (LFU), and so on. The implementation of the first type—say, a near-random replacement—is simple in principle. requiring only a pseudo-random number generator. The second type requires additional storage hardware and logic processing functions, both of which can vary considerably depending on the exact nature of the algorithm and sometimes are quite complex.

Intuitively it would seem that if data clustering (Section 9.4) occurs. page replacement should be based on some history of page usage. This generally seems to be the case, but there are many exceptions wherein a random replacement can give a better hit ratio. Unfortunately, the best algorithm cannot be derived from first principles but must be obtained from simulation of actual job streams as was done in Section 9.4. Vavious studies (Belady, 1966) have resulted in the conclusion that no one best algorithm exists; rather, certain algorithms are best for particular classes of problems and worse for other classes. As a result, disk-main memory virtual systems use a "not recently used" type of algorithm that is an approximation to the LRU algorithm. This can be implemented in many ways. Intuitively it seems reasonable to suppose that the more historical bits that are maintained about page usage, the better would be the choice of page to be replaced. However this requires more stored information and updating, which is expensive and time-consuming. Hence a tradeoff is necessary. In the selection of a page for replacement, one would expect that if a page has not been referenced over a certain time period, it is less likely to be needed next than pages that have been referenced. Hence a reference bit R for a certain time period is necessary. But before selecting a page for removal, it must be recognized that if a page has not been modified (i.e., has not been written into), it need not be written back onto disk but simply can be overlaid (i.e., erased). If it has been modified, however, it must be placed back on the disk before erasure. Since this requires considerably more time than just overlaying, a second status bit is also stored with the previous R "reference" bit. The second bit M specifies whether the page has been modified while residing in main. A page that has not been modified is more eligible for replacement than one that has been modified. In addition, locking bits are often used to protect storage when a page is undergoing swapping, or for other reasons, which we ignore for now.

In principle, the replacement algorithm can be implemented with the R and M bits alone. Whenever a page is referenced, its associated R bit is automatically set to "1"; likewise, M is set to "1" when that page is modified. Eligibility for replacement then goes as "not modified and not referenced," "not modified but referenced," and so on. The time period over which the "not referenced" criterion exists requires some consideration. The M bit is not affected because once modified, a page must be so indicated for the entire time it is resident in main memory. The time period over which the R bit is evaluated can be a fixed or variable period.