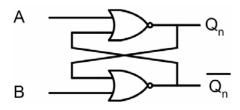

(1) Complete the excitation table for the following storage element:

| <b>Q</b> <sub>n</sub> | Q <sub>n+1</sub> | A | В |

|-----------------------|------------------|---|---|

| 0                     | 0                |   |   |

| 0                     | 1                |   |   |

| 1                     | 0                |   |   |

| 1                     | 1                |   |   |

## SOLUTION

| Q <sub>n</sub> | Q <sub>n+1</sub> | A | В |

|----------------|------------------|---|---|

| 0              | 0                | - | 0 |

| 0              | 1                | 0 | 1 |

| 1              | 0                | 1 | 0 |

| 1              | 1                | 0 | - |

(2) Write the characteristic equation for this storage element.

# $Q_{n+1} =$

# SOLUTION

$Q_{n+1} = B + A'Q_n$

The following characteristic table describes a storage element A-B

| Α | В | <b>Q</b> <sub>n+1</sub> | Operation |

|---|---|-------------------------|-----------|

| 0 | 0 | Q <sub>n</sub>          | Hold      |

| 0 | 1 | 0                       | Reset     |

| 1 | 0 | Q n                     | Hold      |

| 1 | 1 |                         | Toggle    |

(1) Write the characteristic equation for the storage element A-B.

$Q_{n+1} =$

# SOLUTION

$$Q_{n+1} = Q Q \overline{Q} \overline{Q} + \overline{Q} Q_n$$

(2) Implement the A-B storage element using additional gates and an S-R Latch. Show your schematic diagram and derivation process.

| S | Q |

|---|---|

| R | Q |

| 2 & Qm<br>0 0 0<br>0 0 1 | Qn44<br>0<br>1 | S<br>O<br>X | r<br>× O    | a { [ ] x [ ] a { x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] x [ ] |

|--------------------------|----------------|-------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 010                      | 0<br>10<br>0   |             | ×<br>1<br>× | 5=aba R=ba                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 101                      | 1 1 0          | ×<br>1<br>0 | 001         | ā Dro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Design a 3-bit counter which counts in the sequence: 010, 101, 011, 110, 001, 111, 000, 100, 010, ...

Implement the 3-bit counter using J-K Flip-Flops. Draw the state transition table, appropriate K-maps and derive the J-K flip-flop input equations

| CBA<br>0 06<br>0 01<br>0 10<br>0 11<br>1 00<br>1 0 1<br>1 1 0<br>1 1 1 | C <sup>+</sup> B <sup>+</sup> A <sup>+</sup><br>1 00<br>1 1 1<br>1 0 1<br>1 0 1<br>0 1 0<br>0 1 0<br>0 1 1<br>0 0 1<br>0 0 0 | Jc Kc<br>1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | JEKO<br>OX<br>AX<br>X 1<br>X 0<br>AX<br>AX<br>X 1<br>X 1 | jak a<br>0×<br>×0<br>4×<br>×4<br>0×<br>×4<br>0×<br>×4<br>×4 |  |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------|--|

| Jc<br>Jo                                                               |                                                                                                                              | 1 X B                                          | Ko T                                                     | X X A                                                       |  |

| c SE                                                                   |                                                                                                                              |                                                |                                                          |                                                             |  |

$$J_{c} = 1 \quad K_{c} = 1$$

$$J_{B} = C + A \ _{1}K_{B} = \overline{A} + C$$

$$J_{A} = B \ _{1}K_{A} = B$$

| Present State<br>S <sub>n</sub> | Next<br>S <sub>r</sub><br>X=0 |   | Output<br>Z |

|---------------------------------|-------------------------------|---|-------------|

| а                               | а                             | b | 1           |

| b                               | с                             | е | 0           |

| С                               | f                             | g | 1           |

| d                               | с                             | а | 0           |

| е                               | i                             | g | 1           |

| f                               | h                             | i | 1           |

| g                               | С                             | f | 0           |

| h                               | f                             | b | 1           |

| i                               | С                             | е | 0           |

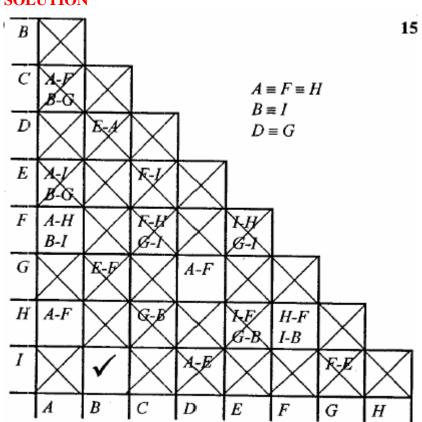

Reduce the following state table to a minimum number of states.

(1) Write the resulting state table. Determine the equivalent states – show them.

[extra space for Problem 4]

(2) Draw the resulting state diagram with all states, transitions and outputs.

|       | Next State |       |   |

|-------|------------|-------|---|

| State | X = 0      | X = 1 | X |

| A     | A          | В     | 1 |

| В     | С          | Ε     | 0 |

| С     | A          | D     | 1 |

| D     | С          | A     | 0 |

| Ε     | B          | D     | 1 |

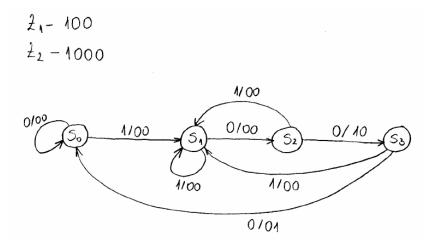

Design a Mealy sequential circuit which has one input (X) and two outputs ( $Z_1$  and  $Z_2$ ) which meets the following specifications:

1) Output  $Z_1$  is 1 when the sequence 100 is detected, otherwise it is 0.

2) Output  $Z_2$  is 1 when the sequence 1000 is detected, otherwise it is 0.

(1) Draw the state diagram

#### **SOLUTION**

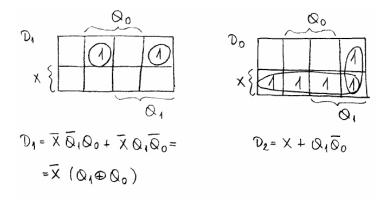

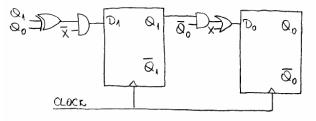

# (2) Derive the input equations for an implementation using D Flip Flops. **SOLUTION**

| X Q Q Q O<br>0 0 0 0<br>0 0 1<br>0 1 0<br>0 1 1<br>1 0 0<br>1 0 1<br>1 0 0 | $ \begin{array}{c}                                     $ |    | D1 D0<br>0 0<br>1 0<br>1 0<br>1 0<br>0 1<br>0 1<br>0 1 |

|----------------------------------------------------------------------------|----------------------------------------------------------|----|--------------------------------------------------------|

| 111                                                                        | 01                                                       | 00 | 01                                                     |

(3) Determine the output equations for  $Z_1$  and  $Z_2$ .

$Z_1 = Z_2 =$

## **SOLUTION**

$\begin{array}{l} Z_1 = X'Q_1Q_2'\\ Z_2 = X'Q_1Q_2 \end{array}$

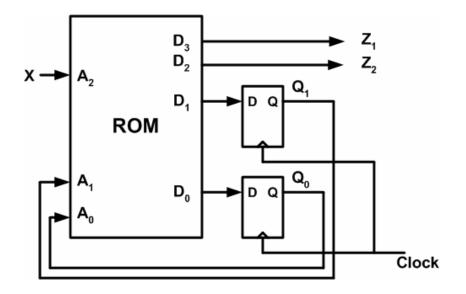

(4) Implement the FSM using ROM and D-Latch Registers

| Address<br>A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> | $\begin{array}{c} \text{Content of ROM} \\ \text{D}_3 \text{D}_2 \text{D}_1 \text{D}_0 \end{array}$ |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| 000                                                     |                                                                                                     |

| 001                                                     |                                                                                                     |

| 010                                                     |                                                                                                     |

| 011                                                     |                                                                                                     |

| 100                                                     |                                                                                                     |

| 101                                                     |                                                                                                     |

| 110                                                     |                                                                                                     |

| 111                                                     |                                                                                                     |

| Address<br>A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> | Content of ROM<br>D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> |

|---------------------------------------------------------|-------------------------------------------------------------------------------|

| 000                                                     | 0000                                                                          |

| 001                                                     | 0010                                                                          |

| 010                                                     | 10 1 1                                                                        |

| 011                                                     | 01 00                                                                         |

| 100                                                     | 00 01                                                                         |

| 101                                                     | 00 04                                                                         |

| 110                                                     | 00 01                                                                         |

| 111                                                     | 00 01                                                                         |

| ×Q,Qo                                                   | ZiZ2 DiDo                                                                     |

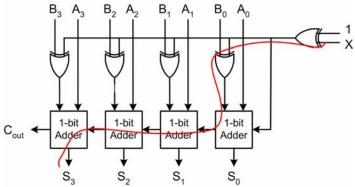

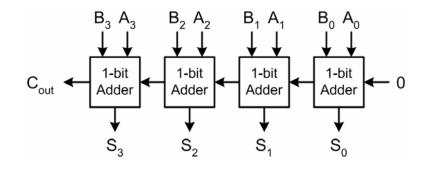

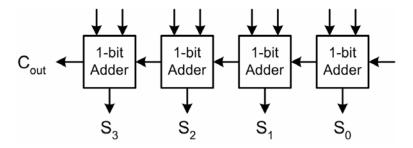

Analyze the following 2's complement 4-bit Ripple Carry Adder

(1) Draw the critical path on the adder.

(2) Show a sequence of input vectors that creates this critical path.

#### **SOLUTION**

Vector1 [A,B] = [0000, 0000] Vector2 [A,B] = [1111, 0001]

(3) Using only XOR gates, modify the four-bit ripple carry adder below to perform 2's complement addition when a control signal X = 1, and 2's complement subtraction (A-B) when X = 0.

(4) Draw the critical path. **SOLUTION**