## EEC180A

# DIGITAL SYSTEMS I Winter, 2006.

## **Solutions for Homework #9**

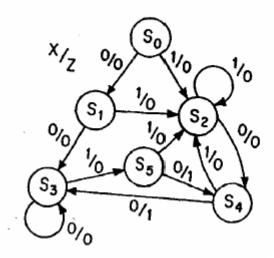

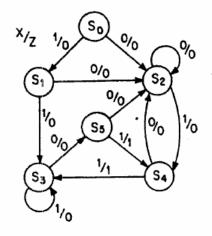

16.1

|                | X = 0            | 1  | X = 0 | 1 |

|----------------|------------------|----|-------|---|

| S              | S <sub>1</sub>   | S2 | 0     | 0 |

| S              | . S <sub>3</sub> | S2 | 0     | 0 |

| S <sub>2</sub> | S <sub>4</sub>   | S2 | 0     | 0 |

| S <sub>3</sub> | S <sub>3</sub>   | S  | 0     | 0 |

| S4             | $S_3$            | S2 | 1     | 0 |

| S <sub>5</sub> | $S_4$            | S2 | 1     | 0 |

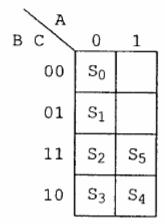

Assignment by guidelines:

I.

$$(1,3,4)$$

$(2,5)$   $(0,1,2,4,5)$

II.  $(1,2)$   $(2,3)_2$   $(2,4)_2$   $(3,5)$

III.  $(0,1,2,3)$   $(4,5)$

#### From Q+ maps:

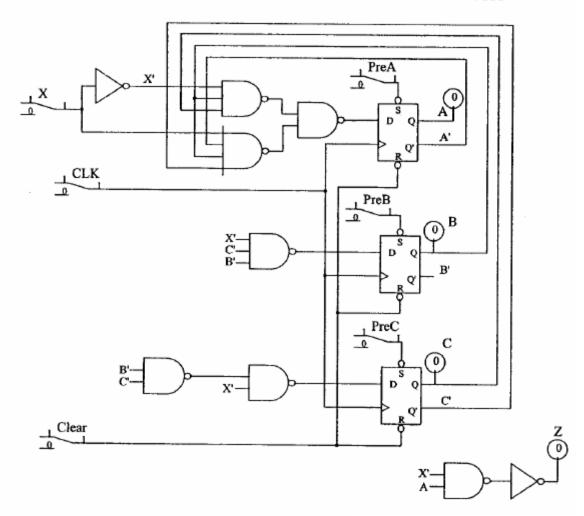

$$A^{+} = X'BC + XA'BC'$$

$B^{+} = X + C + B$   $C^{+} = B'C' + X$   $Z = X'A$

#### Test sequences:

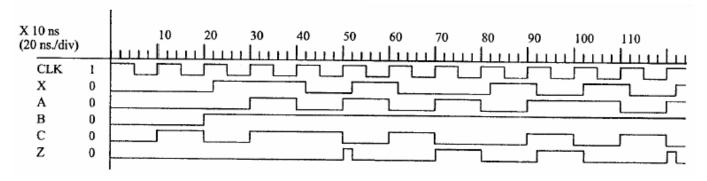

- a) X = 001101001010100010010010

- Z = 000000010100001001101101

- b) X = 110011001010101010101010

- Z = 000100010100001010000101

|                | X == 0         | 1_    | X = 0 | 1 |

|----------------|----------------|-------|-------|---|

| S              | S <sub>2</sub> | S,    | 0     | 0 |

| S              | S2             | $S_3$ | 0     | 0 |

| S <sub>2</sub> | S2             | $S_4$ | 0     | 0 |

| $S_3$          | S <sub>5</sub> | $S_3$ | 0     | 0 |

| $S_4$          | S <sub>2</sub> | $S_3$ | 0     | 1 |

| S,             | S <sub>2</sub> | $S_4$ | 0     | 1 |

Guidelines and state assignments are the same as for 16.1

Flip-flop and output equations and logic circuit are the same as 16.1, except interchange X and X' throughout

Test sequences a)  $X = \frac{11001011010101101101101}{Z = 000000010100001001101101}$

b)

X = 001100110101011010101101

Z = 000100010100001010000101

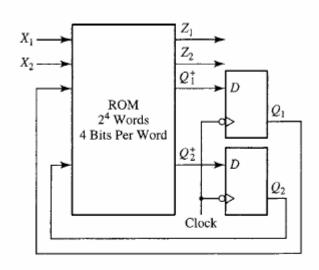

16.15

| <b>X</b> <sub>1</sub> | X <sub>2</sub> | $Q_1$ | $Q_2$ | $Q_1^+$ | $Q_2^+$ | $Z_1$ | Z <sub>2</sub> |

|-----------------------|----------------|-------|-------|---------|---------|-------|----------------|

| 0                     | 0              | 0     | 0     | 1       | 1       | 0     | 0              |

| 0                     | 0              | 0     | 1     | 0       | 0       | 1     | 0              |

| 0                     | 0              | 1     | 0     | 1       | 1       | 0     | 0              |

| 0                     | 0              | 1     | 1     | 1       | 0       | 0     | 0              |

| 0                     | 1              | 0     | 0     | 1       | 0       | 1     | 0              |

| 0                     | 1              | 0     | 1     | 0       | 1       | 1     | 0              |

| 0                     | 1              | 1     | 0     | 0       | 0       | 1     | 0              |

| 0                     | 1              | , 1   | 1     | 1       | 0       | 0     | 0              |

| 1                     | 0              | 0     | 0     | 0       | 1       | 1     | 1              |

| 1                     | 0              | 0     | 1     | 1       | 0       | 1     | 1              |

| 1                     | 0              | 1     | 0     | 0       | 1       | 1     | 1              |

| 1                     | 0              | 1     | 1     | 0       | 1       | 0     | 1              |

| 1                     | 1              | 0     | 0     | 0       | 0       | 0     | 1              |

| 1                     | 1              | 0     | 1     | 1       | 1       | 1     | 1              |

| 1                     | 1              | 1     | 0     | 0       | 1       | 0     | 1              |

| 1                     | 1              | 1     | 1     | О       | 0       | 0     | 1              |

|                       |                |       |       |         |         |       |                |

16.16 (a) Same as Figure 16-10 with ROM replaced by PLA.

| X | Α | В   | С | Z | $D_A$ | $D_B$ | $D_{C}$ |

|---|---|-----|---|---|-------|-------|---------|

| 0 | - | -   | - | 0 | 1     | 0     | 0       |

| 0 | - | -   | 0 | 0 | 0     | 1     | 0       |

| - | 0 | - ' | 1 | 0 | 0     | 1     | 0       |

| - | 0 | 1   | - | 0 | 0     | 1     | 0       |

| - | 1 | -   |   | 0 | 0     | 0     | 1       |

| 1 | - | 0   | - | 0 | 0     | 0     | 1       |

| 0 | 1 | 0   | 1 | 1 | 0     | 0     | 0       |

| 1 | 0 | 1   | 0 | 1 | 0     | 0     | 0       |

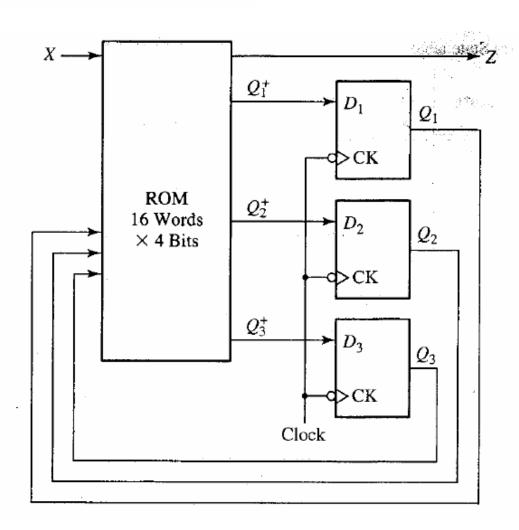

FIGURE 16-10 Realization of Table 16.6(a) Using a ROM