## EEC118 – Spring '03

## Homework Solution #3

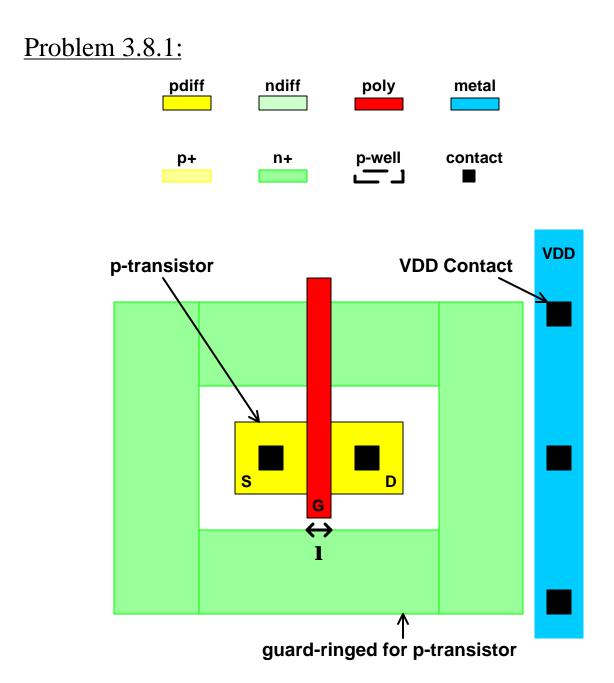

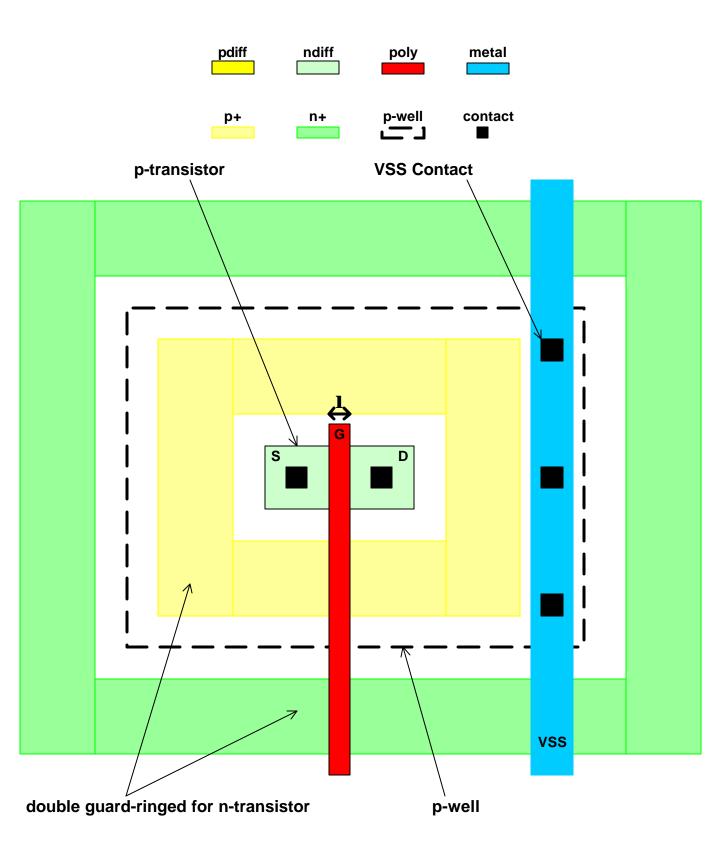

Note: in p-well process, the substrate is n-type.

- VDD contact is needed for the substrate;

VSS contact is needed for the p-well

- (2) Double guard-ringed is applied to n-transistor

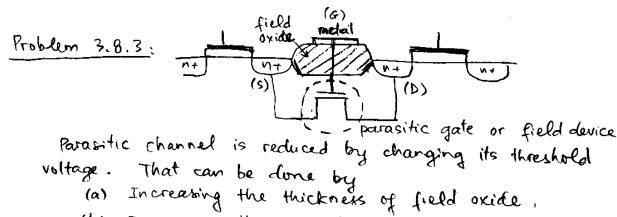

(b) Increasing the impurity concentration under the field oxide

Problem 3.8.4:

A field transistor can be used to prevent overvoltage in a CMOS chip. It is done by controlling the threshold voltage of the field transistor such that the field transistor is ON when voltage exceeds a certain level. That allows the extra charge due to overvoltage to be dumped off the circuit.

Problem 3.8.5 :

Substrate and well contacts are important.

(a) They ensure that the voltages of the substrate and the well are well established to eliminate the bodyvoltage variation which can affect circuit performance

(b) They also prevent lateh-up when being placed next to potentially affected nodes.

Problem 3.8.6:

A "dummy collector" prevents latchup by reducing the current gain (3 of the parasitic BJT. It is done by capturing (or recombining) minority carriers and therefore reducing the amount of these carriers injected into the base of the BJT. therefore reducing the amount of charge collected at the collector.

Problem 3.8.7:

A pull-up resistor for a pad is a p-transistor. It will potentially drive a lot of current and therefore will subject to a lot of noise. Latchup can occur when this p-transistor coupling to nearby n-transistors. So, latchup protection is needed.

with the same reasoning, latch-up protection is needed for the pull-down resistor as well.