# EEC 118 Lecture #5: CMOS Inverter AC Characteristics

Rajeevan Amirtharajah University of California, Davis Jeff Parkhurst Intel Corporation

### Acknowledgments

• Slides due to Rajit Manohar from ECE 547 <u>Advanced VLSI Design</u> at Cornell University

# Outline

- Review: CMOS Inverter Transfer Characteristics

- CMOS Inverters: Rabaey 5.4-5.5 (Kang & Leblebici, 6.1-6.4, 6.7)

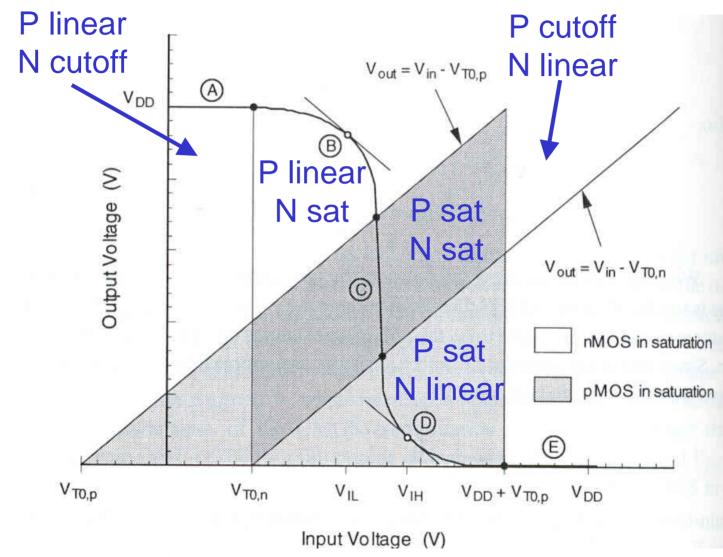

### **CMOS Inverter VTC: Device Operation**

Amirtharajah/Parkhurst, EEC 118 Spring 2011

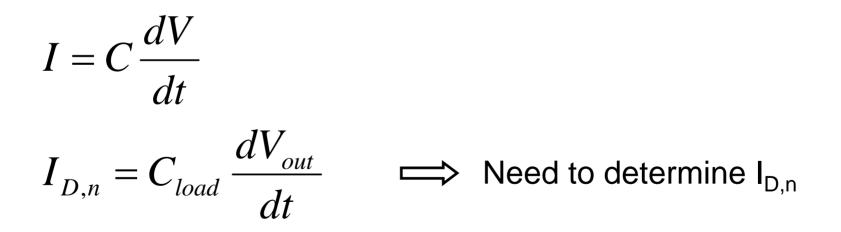

For CMOS (or almost all logic circuit families), only one fundamental equation necessary to determine delay:

$$I = C \frac{dV}{dt}$$

- Consider the discretized version:  $I = C \frac{\Delta V}{\Delta t}$

- Rewrite to solve for delay:

$$\Delta t = C \frac{\Delta V}{I}$$

• Only three ways to make faster logic:  $\Box C$ ,  $\Box \Delta V$ ,  $\Box I$

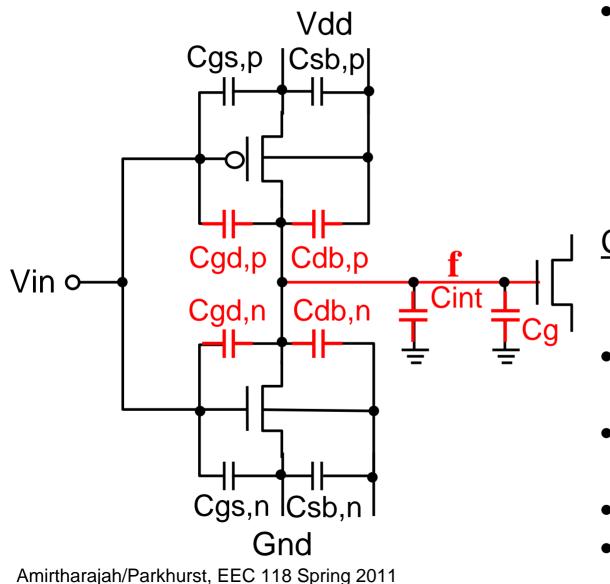

# **CMOS Inverter Capacitances**

Assume input transition is fixed, then delay determined by output

<u>Capacitance on</u> node f (output):

- Junction cap Cdb,p and Cdb,n

- Gate capacitance Cgd,p and Cgd,n

- Interconnect cap

- Receiver gate cap

### **CMOS Inverter Junction Capacitances**

• Junction capacitances C<sub>db,p</sub> and C<sub>db,n</sub>:

– Equation for junction cap:

$$C_{j}(V) = \frac{AC_{j0}}{\left(1 - \frac{V}{\phi_{0}}\right)^{m}}, \qquad C_{j0} = \left(\frac{\varepsilon q}{2} \frac{N_{a}N_{d}}{N_{a} + N_{d}} \frac{1}{\phi_{0}}\right)^{m}$$

- Non-linear, depends on voltage across junction

- Use  $K_{eq}$  factor to get equivalent capacitance for a voltage transition

$$C_{db} = AK_{eq}C_j + PK_{eqsw}C_{jsw}$$

- Gate capacitances C<sub>GD,p</sub> and C<sub>GD,n</sub>:

- Just after the input switches(t = 0<sup>+</sup>), what regions are transistors in?

- One is in cutoff:  $C_{GD}$  = Overlap Cap

- One is in Saturation:  $C_{GD}$  = Overlap Cap

- Therefore, gate-to-drain capacitance is due to overlap capacitance :

$$C_{gd,p} = C_{gd,n} = C_{ox}WL_D$$

However, also need to consider *<u>Miller effect</u>*...

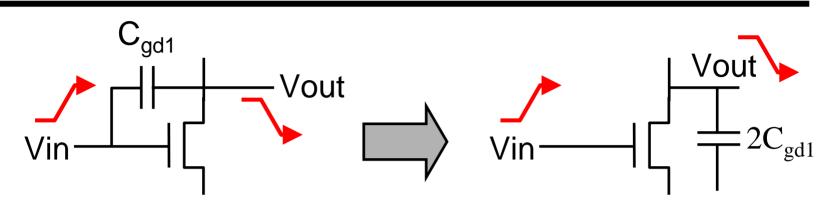

# **CMOS Inverter Capacitances: Miller Effect**

- When input rises by  $\Delta V$ , output falls by  $\Delta V$

- Change in stored charge:  $\Delta Q = C_{gd1} \Delta V (-C_{gd1} \Delta V)$

- Effective voltage change across  $C_{gd1}$  is  $2\Delta V$

- Effective capacitance to ground is *twice* C<sub>ad1</sub>

- Including Miller effect:

$$C_{gd,p} = C_{gd,n} = 2C_{ox}WL_D$$

(For transistor in Cutoff)

### **CMOS Inverter Capacitances: Receiver**

- Receiver gate capacitance

- Includes all capacitances of gate(s) connected to output node

- Unknown region of operation for receiver transistor: total gate cap varies from (2/3)WLC<sub>ox</sub> to WLC<sub>ox</sub>

- Ignore Miller effect (taken into account on output)

- Assume worst-case value, include overlap

$$C_g = WL_{eff}C_{ox} + 2WL_DC_{ox}$$

$$C_g = WL C_{ox}$$

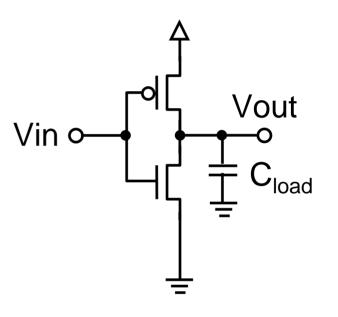

### **Inverter Capacitances: Analysis**

• Simplify the circuit: combine all capacitances at output into one lumped linear capacitance:

• Cgs,n and Cgs,p are not connected to the load. These are part of the gate capacitance Cg

- Suppose ideal voltage step at input

- Assume: Current charging or discharging capacitance C<sub>load</sub> is nearly constant I<sub>avg</sub>

•

$$t_{PHL} = C_{load} (Vdd - Vdd/2) / I_{avg}$$

•

$$t_{PLH} = C_{load} (Vdd/2 - Vss) / I_{avg}$$

# Inverter Delay: Falling $\int I_{D.n} = C_{load}$

Assume PMOS fully off (ideal step input, I<sub>D,p</sub> = 0)

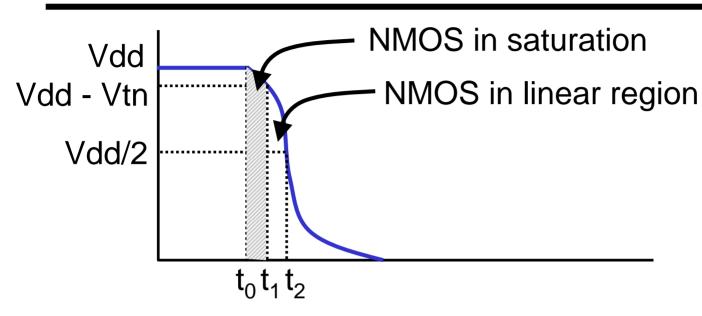

# **Inverter Delay: Falling**

- From t<sub>0</sub> to t<sub>1</sub>: NMOS in saturation

- From t<sub>1</sub> to t<sub>2</sub>: NMOS in linear region

- Find I<sub>D</sub> in each region

### **Inverter Delay: Falling t<sub>1</sub>-t<sub>0</sub>**

- Assumption: Input fast enough to go through transition before output voltage changes

- $V_{out}$  drops from  $V_{OH}$  to  $V_{DD}$ - $V_{TN}$  (NMOS saturated)

$$I_{DS} = k_n (V_{in} - V_{T0,n})^2 / 2 = k_n (V_{OH} - V_{T0,n})^2 / 2$$

$$\int_{t_0}^{t_1} dt = \frac{-2C_L}{k_n (V_{OH} - V_{T0,n})^2} \int_{V_{OH}}^{V_{OH} - V_{T0,n}} dV_{out}$$

$$t_1 - t_0 = \frac{2C_L V_{T0,n}}{k_n (V_{OH} - V_{T0,n})^2}$$

### **Inverter Delay: Falling t<sub>2</sub>-t<sub>1</sub>**

- $V_{out}$  drops from ( $V_{OH}$ - $V_{T0,n}$ ) to  $V_{DD}/2$

- NMOS in linear region

$$I_{DS} = k_n \left[ (V_{OH} - V_{T0,n}) V_{out} - \frac{1}{2} V_{out}^2 \right]$$

$$t_2 - t_1 = -C_L \int_{V_{OH} - V_{T0,n}}^{(V_{OH} + V_{OL})/2} \frac{dV_{out}}{k_n \left[ (V_{OH} - V_{T0,n}) V_{out} - \frac{1}{2} V_{out}^2 \right]}$$

$$t_2 - t_1 = \frac{C_L}{k_n (V_{OH} - V_{T0,n})} \ln \left[ \frac{2(V_{OH} - V_{T0,n}) - (V_{OH} + V_{OL})/2}{(V_{OH} + V_{OL})/2} \right]$$

### **Inverter Delay: Falling, Total**

• Total fall delay =  $(t_1-t_0) + (t_2-t_1)$

$$t_{PHL} = \frac{C_L}{k_n (V_{OH} - V_{T0,n})} \left[ \frac{2V_{T0,n}}{V_{OH} - V_{T0,n}} + \ln \left( \frac{4(V_{OH} - V_{T0,n})}{V_{OH} + V_{OL}} - 1 \right) \right]$$

- Similar calculation as for falling delay

- Separate into regions where PMOS is in linear, saturation

$$t_{PLH} = \frac{C_L}{k_p (V_{OH} - V_{OL} - |V_{T0,p}|)} \left[ \frac{2|V_{T0,p}|}{V_{OH} - V_{OL} - |V_{T0,p}|} + \ln \left( \frac{4(V_{OH} - V_{OL} - |V_{T0,p}|)}{V_{OH} + V_{OL}} - 1 \right) \right]$$

• Note: to balance rise and fall delays (assuming  $V_{OH} = V_{DD}$ ,  $V_{OL} = 0V$ , and  $V_{T0,n} = V_{T0,p}$ ) requires

$$\frac{k_p}{k_n} = 1 \qquad \frac{\left(\frac{W}{L}\right)_p}{\left(\frac{W}{L}\right)_n} = \frac{\mu_n}{\mu_p} \approx 2.5$$

### **Inverter Rise, Fall Times**

- Summary -- Exact method: separate into two regions

- $V_{out}$  drops from 0.9 $V_{DD}$  to  $V_{DD}$ - $V_{T,n}$  (NMOS in saturation)

- $V_{out}$  rises from 0.1 $V_{DD}$  to  $|V_{T,p}|$  (PMOS in saturation)

- t<sub>2</sub>

- t<sub>1</sub>

- $V_{out}$  drops from  $V_{DD}\text{-}V_{T,n}$  to  $0.1V_{DD}$  (NMOS in linear region)

- +  $V_{out}$  rises from  $|V_{T,p}|$  to 0.9  $V_{DD}$  (PMOS in linear region)

$- t_{f,r} = t_1 + t_2$

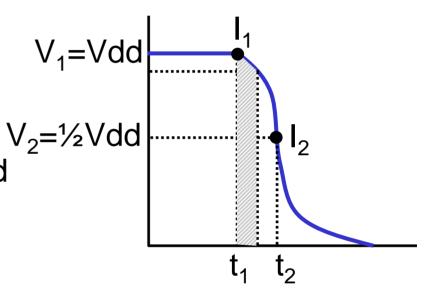

- Review of approximate method

- Assume a constant average current for the transition

- I<sub>avg</sub> = average of drain

current at beginning and end of transition

$$t_{PHL} = \frac{C_{load}}{I_{avg}} \left( V_{DD} - \frac{1}{2} V_{DD} \right)$$

$$t_{PLH} = \frac{C_{load}}{I_{avg}} \left(\frac{1}{2}V_{DD} - V_{SS}\right)$$

$$I_{avg} = \frac{1}{2}(I_1 + I_2)$$

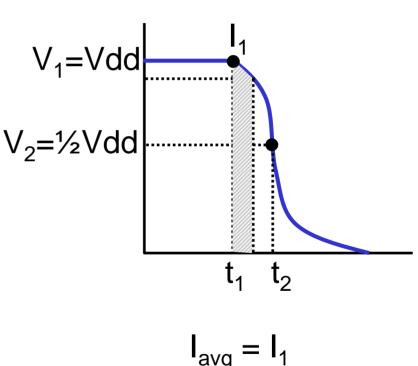

# **CMOS Inverter Delay: 2<sup>nd</sup> Approximation**

- Another approximate method:

- Again assume constant I<sub>avg</sub>

- $I_{avg}$  = current  $I_1$  at start of transition

$$t_{PHL} = \frac{C_{load}V_{DD}}{k_n (V_{DD} - V_{Tn})^2}$$

$$t_{PLH} = \frac{C_{load}V_{DD}}{k_p (V_{DD} - |V_{TP}|)^2}$$

Why is this a good approximation (esp. for deep submicron)?

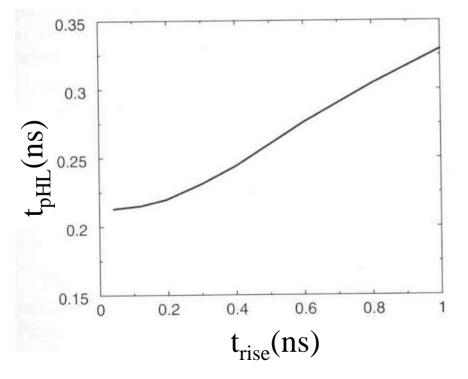

### **CMOS Inverter Delay: Finite Input Transitions**

- What if input has finite rise/fall time?

- Both transistors are on for some amount of time

- Capacitor charge/discharge current is reduced

**Empirical equations:**

$$t_{phl}(actual) = \sqrt{t_{phl}^2(step) + \left(\frac{t_r}{2}\right)^2}$$

$$t_{plh}(actual) = \sqrt{t_{plh}^2(step) + \left(\frac{t_f}{2}\right)^2}$$

- Minimize load capacitances

- Small interconnect capacitance

- Small Cg of next stage

- Raise supply voltage

– Increases current faster than increased swing  $\Delta V$

• Increase transistor gain factor

Increase transistor drive current for charging/discharging output capacitance

• Use low threshold voltage devices

More subthreshold leakage power dissipation

- Static power consumption (ideal) = 0

- Actually DIBL (Drain-Induced Barrier Lowering), gate leakage, junction leakage are still present

- Dynamic power consumption

$$P_{avg} = \frac{1}{T} \int_{0}^{T} v(t) i(t) dt$$

$$P_{avg} = \frac{1}{T} \left[ \int_{0}^{T/2} V_{out} \left( -C_{load} \frac{dV_{out}}{dt} \right) dt + \int_{T/2}^{T} \left( V_{DD} - V_{out} \right) \left( C_{load} \frac{dV_{out}}{dt} \right) dt \right]$$

$$P_{avg} = \frac{1}{T} \left[ \left( -C_{load} \frac{V_{out}^{2}}{2} \right) \right]_{0}^{T/2} + \left( V_{DD} V_{out} C_{load} - \frac{1}{2} C_{load} V_{out}^{2} \right) \right]_{T/2}^{T}$$

$$P_{avg} = \frac{1}{T} C_{load} V_{DD}^{2} = C_{load} V_{DD}^{2} f$$

# **Next Time: Combinational Logic**

- Combinational MOS Logic

- DC Characteristics, Equivalent Inverter method

- AC Characteristics, Switch Model