Name: Salutions Lab Section:

For all transistors:  $L_{min} = 1~\mu m,~W_{min} = 1~\mu m,~V_{T,p} = -1~V,~\mu_p C_{ox} = (1/6)~x~10^{-3}~A/V^2,~\lambda_p = 0.0V^{-1},~V_{T,n} = 1~V,~\mu_n C_{ox} = (1/2)~x~10^{-3}~A/V^2,~\lambda_n = 0.0V^{-1}.$

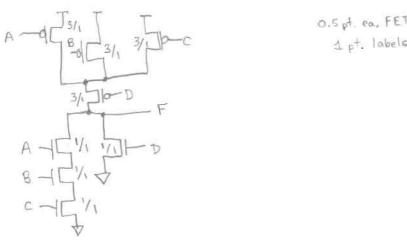

**Problem 1 (5 points)** Design a four-input static CMOS logic gate which implements the Boolean expression  $F = \overline{A \cdot B \cdot C + D}$ . Clearly label all inputs, outputs, and power supply connections. Pick sizes for the transistors such that the worst case rise and fall times of the output are equal to a minimum-sized inverter.

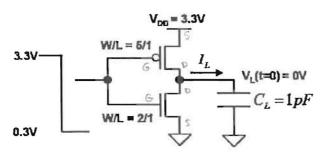

**Problem 2 (5 points)** A step input is applied at time t=0 to the loaded inverter with dimensions and initial conditions as shown below. What is the current  $I_L$  immediately after the step is applied?

PMOS:  $V_{GS} = -3\sqrt{V_{DS} = -3.3V}$

$$V_{GS} - V_{T,p} = -2V > V_{DS} \quad \frac{\text{Saturation}}{\text{Saturation}} \quad \text{(1pt.)}$$

$$V_{L}(t=0) = 0V$$

$$= C_{L} = 1pF \qquad I_{L} = I_{DS,p} = \frac{M_{P}(0)}{2} \left(\frac{W}{L}\right) \left(V_{GS,p} - V_{T,p}\right)^{2} \quad (2pts.)$$

$$= \frac{11/6 \times 10^{-3} \, \text{A/V}^{2}}{2} \left(\frac{S}{1}\right) \left(3.0V - -1V\right)^{2} \quad (0.5pt.)$$

$$= \frac{1.67 \, \text{mA}}{2} \quad (0.5 \, pt.)$$