EEC116 Problem Set #4 Solution

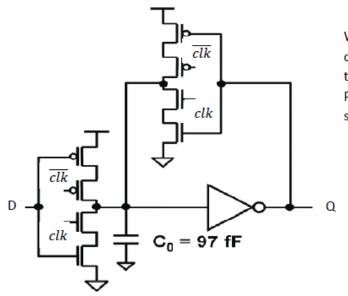

# **1.** Transparent Latch

Problem 1.1

We want the latch to be transparent when clk is positive, so we put clk at the gates of the NMOS's and clk\_bar at the gates of the PMOS's. The feedback inverter makes it static instead of dynamic.

### Problem 1.2

Since the output equals the input after some delay, we imagine the input D at V<sub>DD</sub> and the output Q low before the clk signal goes high. We're given the  $t_{pLH}$  for the second inverter which is the delay for the output to go from GND to 0.5 V<sub>DD</sub>. Assuming that  $t_{pLH2}$  is the time from when the input changes to it's 50% value till the output rises to the 50% value, the  $t_{pLH}$  from the input to the output is approximately $t_{HL1} + t_{pLH2}$  because we need the time it takes the voltage at the capacitor  $V_{C_0}$  or the input to the second inverter to become 0.5 V<sub>DD</sub>. We don't have to calculate the full fall time for the first inverter.

Using the average current method,

$$\tau_{pHL1} = \frac{c_{load}\Delta V}{I_{avg}}$$

where  $\Delta V$  is  $0.5V_{DD}$ .

$I_{avg} = \frac{1}{2} \left[ I \left( V_{in} = 1.8, V_{C_0} = 1.8 \right) + I \left( V_{in} = 1.8, V_{C_0} = 0.9 \right) \right]$

Saturation since Linear since  $G$

$V_{DS} \ge V_{GS} - V_{T,n}$

$V_{DS} < V_{GS} - V_{T,n}$

$V_{DS} < V_{GS} - V_{T,n}$

We can treat the two NMOS in series as one NMOS with an effective length of 2\*L.

$$I_{avg} = \frac{k_n}{4} \Big[ (V_{GS} - V_{T,n})^2 + 2(V_{GS} - V_{T,n}) V_{DS} - V_{DS}^2 \Big] = \frac{300\mu A}{4} \frac{0.45}{2 * 0.180} [1.2^2 + 2(1.2)(0.9) - 0.9^2] = 262 \,\mu A$$

$$\tau_{HL} = \frac{97 \, fF * 0.9 \, V}{262 \, \mu A} = \frac{333 \, \text{ps}}{233 \, \text{ps}}$$

$$t_{pLH} = 333 \, ps + 45 \, ps = 378 \, ps$$

You can also use the 2<sup>nd</sup> approximation using the saturation current, which gives  $\tau_{HL} = 323 \text{ ps}$  and  $t_{pLH} = 323 \text{ ps} + 45 \text{ ps} = 368 \text{ ps}$ .

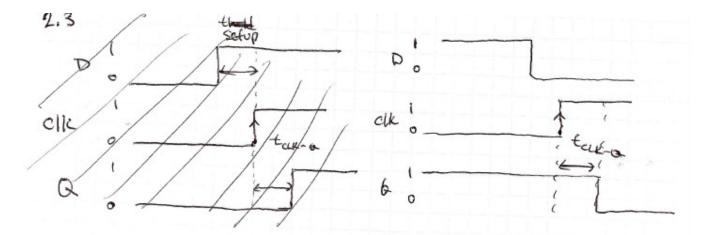

### Problem 1.3

The same can be done as in the previous problem, but for the output falling from high to low and the input low before clock goes high. Therefore, we will be focus on the PMOS in the first inverter, and the second inverter has  $t_{pHL} = 45$  ps. 1.8

$$\begin{split} I_{avg} &= \frac{1}{2} \begin{bmatrix} I \left( V_{in} = 0, V_{C_0} = 0 \right) + I \left( V_{in} = 0, V_{C_0} = 0.9 \right) \end{bmatrix} & S \\ & \text{Saturation since} & \text{Linear since} & 0 \\ & |V_{DS}| \ge |V_{GS}| - |V_{T,p}| & |V_{DS}| < |V_{GS}| - |V_{T,p}| & G \\ & D & V_{C_0} \end{bmatrix} \\ I_{avg} &= \frac{k_p}{4} \begin{bmatrix} (V_{GS} - V_{T,p})^2 + 2(V_{GS} - V_{T,p})V_{DS} - V_{DS}^2 \end{bmatrix} \\ &= \frac{100\mu A}{4} \frac{1.44}{2*0.180} [(-1.1)^2 + 2(-1.1)(-0.9) - (-0.9)^2] = 238 \ \mu A \\ \tau_{pLH1} &= \frac{97 \ fF*0.9 \ V}{238 \ \mu A} = 367 \ \text{ps} \end{bmatrix} \\ & t_{pHL} = 367 \ ps + 45 \ ps = 412 \ \text{ps} \end{bmatrix} \end{split}$$

### Problem 1.4

The Master stage latch in the flip-flop determines when a signal is "let in" or is the first of the two cascaded latches. In this case since the flip-flop is negative edge triggered, meaning that the output will hold the input value when the clock goes low, the master latch is active when the clock is high. The setup time is the time the input has to be stable before the active edge so that it can propagate to the input of the slave stage and be held. In this case, the longest possible propagation delay will determine the setup time. The longest propagation delay we see from the ideal clock pulse to the output changing to the 50% value is 412 ps. To be more conservative so that output reaches GND and since it's an ideal clock, it would most likely take another 45 ps resulting in a setup time of <u>457 ps.</u>

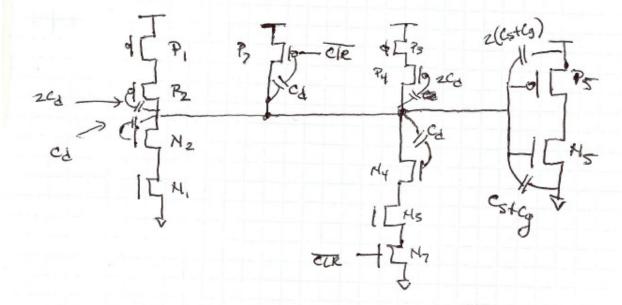

# 2. Flip-Flop

2.2

$$V_{PN} = \frac{V_{DD}}{V_{PN}} = \frac{T_{P} = T_{N}}{2} \left( \frac{V_{PN} - V_{TN}}{2} = \frac{K_{P}}{2} \left( \frac{V_{DD} - V_{N}}{N} - \left| \frac{V_{P}}{N} \right| \right)^{2}$$

$$= \sqrt{\frac{K_{H}}{K_{P}}} \left( \frac{V_{M} - V_{TN}}{K_{P}} \right)^{2} = \left( \frac{V_{DD} - V_{M}}{V_{DD}} - \left| \frac{V_{TN}}{N} \right| \right)^{2}$$

$$= \sqrt{\frac{K_{H}}{K_{P}}} \left( \frac{V_{DD} - V_{M}}{K_{P}} - \left| \frac{V_{DD}}{K_{P}} \right| \right) = \sqrt{\frac{K_{H}}{K_{P}}} \frac{V_{M}}{V_{M}} + V_{M} = V_{DD} + \sqrt{\frac{K_{H}}{K_{P}}} \frac{V_{TN} - \left| \frac{V_{HD}}{K_{P}} \right|$$

Solve for  $V_{M} = \frac{V_{DD} + \sqrt{\frac{K_{H}}{K_{P}}} \frac{V_{TN} - \left| \frac{V_{HD}}{K_{P}} \right|}{1 + \sqrt{\frac{K_{H}}{K_{P}}}}$

The only difference between the cross stage and the inverter is the ratio of  $\frac{kn}{kp}$ for the inverter  $\frac{kn}{kp} = \frac{300 mA/v^2 \cdot \frac{1.4}{0.6}}{100 mA/v^2 \cdot \frac{2.9}{0.6}} = \frac{800}{466} = 167$   $\frac{kn}{kp} = \frac{300 mA/v^2 \cdot \frac{1.4}{1.2}}{100 mA/v^2 \cdot \frac{2.9}{1.2}} = \frac{400}{235} = 1.7$

The Ration of KH/Kp is equal so the threshild (Vm) are equal,

When the clock is Low, the storage node formed by the gates of transistors N1 \$ P1 is discharged when the signal D fills. is Low.

After the clock rises, the "o" stored on the gates of XI \$PI is passed to Q. when the clock signal is high the c<sup>2</sup> mos stage drives the inverter formed By transistors NS \$ P5 to a logic "i". This inverter then drives the output & low. from the we see that we need to compute the delay through the c<sup>2</sup>ms stage \$ the inverter.

ALL PIMOS devices have capacitees which are 2x Larger as they have twice the area.

C = 7cd + 3cs + 3cg = 10Cs + 3cgC = 10.10FF + 3.15FF = 145FF

$$(p_{LH})_{2mos} = \frac{14sFF \cdot 0.aV}{12a.2s.vA} = 1.uS$$

$$T_{PHL}_{THV} = \frac{C}{T_{AVg}} \qquad T_{AVg} = \frac{1}{2} \left( \frac{1}{5xt_{1}H} + \frac{1}{14v_{1}H} \right)$$

$$T_{Sat_{1}H} = \frac{k_{H}}{2} \left( \frac{1}{8x - V_{H}} \right)^{2} \qquad k_{H} = A_{H} Coc \frac{1}{14} = 700 \text{ mJ}_{1/2}$$

$$T_{Sat_{1}H} = \frac{k_{H}}{2} \left( \frac{1}{8 - 0.6} \right)^{2} = 504 \text{ mJ}$$

$$T_{400, H} = \frac{k_{H}}{2} \left( \frac{1}{8 - 0.6} \right)^{2} = 504 \text{ mJ}$$

$$T_{400, H} = \frac{k_{H}}{2} \left( \frac{1}{8 - 0.6} \right)^{2} = 504 \text{ mJ}$$

$$T_{400, H} = \frac{k_{H}}{2} \left( \frac{1}{8 - 0.6} \right)^{2} = \frac{1}{2} \sqrt{2} \right]$$

$$Assime mud part \quad Vos = \frac{1}{2} \sqrt{2} = 0.6$$

$$T_{140, H} = 700 \text{ mJ}_{1} \approx \frac{1}{2} \left( \frac{1}{8 - 0.6} \right) \frac{1}{6} \cdot 0.6^{2} \right] = 378 \text{ mA}$$

$$T_{400, H} = \frac{504 \text{ mJ}_{1} + 378 \text{ mJ}_{2} = 441 \text{ mJ}_{1}}{2}$$

$$C = 600 + 365 + 36g$$

$$C = 155 \text{ FF}$$

$$N_{H} = \frac{1}{14} \frac{1}{14}$$

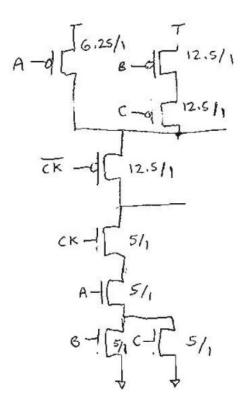

## 3. Mixed Combinational and Sequential Logic

F= A (B+C)

For  $+fall = trise, \mu_n W_n = \mu_p W_p$   $\implies W_p = \mu_n W_n = 2.5 W_n$  $\mu_p$

Other solutions possible ...