# USERS' MANUAL FOR SWITCAP2 ${\rm VERSION}~1.1^{1}$

K. Suyama

Department of Electrical Engineering

and Center for Telecommunications Research

Columbia University

New York, NY 10027

S. C. Fang<sup>2</sup>

February 1 1992

$<sup>^{1}\</sup>mathrm{Copyright}$  ©1990, 1992 by Columbia University. All rights reserved.

<sup>&</sup>lt;sup>2</sup>S. C. Fang is the author of the original SWITCAP manual which was written in 1982 at Department of Electrical Engineering, Columbia University.

# Contents

| 1 | INT           | RODU   | UCTION                                                         | 5  |

|---|---------------|--------|----------------------------------------------------------------|----|

| 2 | $\mathbf{FU}$ | NDAM   | IENTALS                                                        | 11 |

|   | 2.1           | Relat  | ion of SWITCAP2 to Laboratory Setup                            | 11 |

|   | 2.2           | Linea  | r SCN Example: A SC Integrator                                 | 12 |

|   |               | 2.2.1  | Timing Section                                                 | 12 |

|   |               | 2.2.2  | Network Section                                                | 16 |

|   |               | 2.2.3  | Sinusoidal Steady-State Analysis                               | 18 |

|   |               | 2.2.4  | Input Format                                                   | 22 |

|   |               | 2.2.5  | Piecewise-Constant Waveforms, Sampling, and Discrete-Time Fre- |    |

|   |               |        | quency Response                                                | 23 |

|   |               | 2.2.6  | Sensitivity Analysis                                           | 38 |

|   | 2.3           | Time   | -Domain analysis of Mixed SC/Digital Networks                  | 43 |

|   |               | 2.3.1  | Definition of mixed SC/D networks                              | 44 |

|   |               | 2.3.2  | SC Sigma-Delta Modulator                                       | 47 |

|   |               | 2.3.3  | Timing Section                                                 | 50 |

|   |               | 2.3.4  | Network Section                                                | 50 |

|   |               | 2.3.5  | Nonlinear Transient Analysis:NTRAN                             | 52 |

|   |               | 2.3.6  | Initialization                                                 | 53 |

|   |               | 2.3.7  | Subcircuit Revisited: Initialization Within Subcircuit         | 53 |

| 3 | AD            | VANC   | ED FEATURES                                                    | 56 |

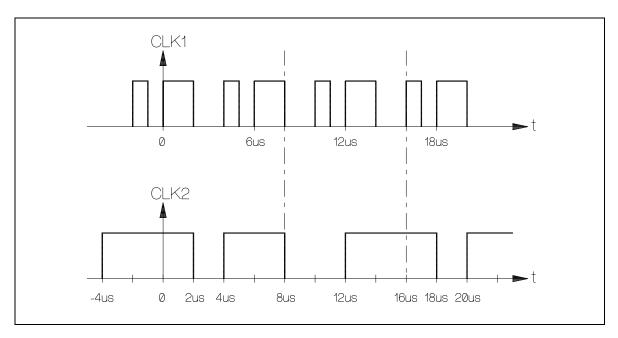

|   | 3.1           | Multi  | ple Clocks and Multiple Samples                                | 56 |

|   | 3.2           | Frequ  | iency Overlap                                                  | 58 |

|   | 3.3           | Time   | -Domain Waveforms                                              | 58 |

|   | 3.4           |        | l Values in TRAN for Linear SCN's                              | 60 |

|   | 3.5           | Initia | l Values in NTRAN                                              | 60 |

|   | 3.6           | Finite | Resistance Simulation                                          | 61 |

|   | 3.7            | Operational Amplifier Poles    | 63 |

|---|----------------|--------------------------------|----|

|   | 3.8            | Clock Feedthrough              | 65 |

|   | 3.9            |                                | 69 |

| 4 | $\mathbf{OP}'$ | IONS AND OUTPUTS               | 71 |

|   | 4.1            | Option Statements              | 71 |

|   | 4.2            | PRINT and PLOT Statements      | 72 |

|   |                | 4.2.1 Voltage Across Two Nodes | 72 |

|   |                | 4.2.2 Plot Window              | 73 |

|   |                | 4.2.3 Plot Numbering           | 73 |

|   |                | 4.2.4 Plot Overlaying          | 74 |

|   |                |                                | 75 |

|   |                | ·                              | 76 |

|   |                |                                | 77 |

|   | 4.3            |                                | 78 |

|   | 4.4            |                                | 78 |

| 5 | RE             | ERENCE MANUAL                  | 79 |

# List of Figures

| 2.1  | General laboratory setup                                                        |

|------|---------------------------------------------------------------------------------|

| 2.2  | SWITCAP2 overall structure                                                      |

| 2.3  | A simple switched-capacitor network                                             |

| 2.4  | Measuring Sinusoidal Steady-state Response                                      |

| 2.5  | Input Sample-and-Hold                                                           |

| 2.6  | Output Sample-and-Hold                                                          |

| 2.7  | Input Pulse Waveform                                                            |

| 2.8  | Cascade of Two Circuits                                                         |

| 2.9  | Structure of mixed SC/D network defined in SWITCAP2                             |

| 2.10 | Latched comparator and its operation                                            |

| 2.11 | An equivalent model of a latched comparator                                     |

| 2.12 | (a)SCN implementation of a second-order sigma-delta modulator, (b) timing       |

|      | waveforms, and (c) a balanced op amp model                                      |

| 3.1  | Multiple Clock Waveforms                                                        |

| 3.2  | Multiple sampling instants per sampling period                                  |

| 3.3  | Switched-capacitor equivalent resistor                                          |

| 3.4  | Finite-gain single-pole operational amplifier                                   |

| 3.5  | Transfer function of finite-gain single-pole operational amplifier using equiv- |

|      | alent SC network for finite resistance                                          |

| 3.6  | MOS Transistor Switch Model                                                     |

| 3.7  | MOS Transistor Switch Model                                                     |

# ACKNOWLEDGEMENT

Professor Yannis Tsividis has contributed to the original concept of SWITCAP and SWITCAP2. The authors would like to thank Ilya Yusim for his help with the programming of the input parser for SWITCAP2 and with the integration of figures and text in this manual.

### Chapter 1

### INTRODUCTION

SWITCAP2 is a general simulation program for analyzing linear switched-capacitor networks (SCN's) and mixed switched-capacitor/digital (SC/D) networks. The major features of the program are as follows:

#### 1. SWITCHING INTERVALS

An arbitrary number of switching intervals per switching period is allowed. The durations of the switching intervals may be unequal and arbitrary.

#### 2. NETWORK ELEMENTS

The program can simulate linear SCN's containing the following types of ideal analog components: ON-OFF switches, linear capacitors, linear voltage-controlled voltage sources (VCVS's), and independent voltage sources. The waveforms of the independent sources may be continuous or piecewise-constant. The switches in linear SCN's are controlled by periodic clock waveforms only.

In addition to the above elements mentioned, a mixed SC/D network may contain comparators and logic gates such as AND, OR, NOT, NAND, NOR, XOR, and XNOR. The ON-OFF switches in a mixed SC/D network may be controlled not only by periodic waveforms but also by nonperiodic waveforms from the output of comparators and logic gates.

#### 3. TIME-DOMAIN ANALYSES OF LINEAR SCN'S AND MIXED SC/D NETWORKS

The program provides two kinds of time-domain analyses. One is only applicable for linear SCN's and it computes the transient response of linear SCN's to any prescribed input waveform for  $t \geq 0$  after computing the steady-state values for a set of dc inputs for t < 0.

The other time-domain analysis applies to mixed SC/D networks as well as linear SCN's. It computes the transient response of networks without computing the steady-state values as initial conditions. A set of the initial condition of analog and digital nodes at  $t = 0^-$  may be specified by user.

#### 4. VARIOUS WAVEFORMS FOR TIME DOMAIN ANALYSES

Various time-domain waveforms such as pulse, pulse train, cosine, exponential, exponential cosine, piecewise linear, and dc sources are available as the input for transient analysis.

#### 5. FREQUENCY DOMAIN ANALYSES OF LINEAR SCN'S

Since SCN's are time-varying networks, a single-frequency sinusoidal input can produce a steady-state output containing many frequency components. The program can determine all of these output frequency components for both continuous and piecewise-constant input waveforms. Z-domain quantities can also be computed.

Frequency-domain group delay and sensitivity analyses are also provided.

#### 6. BUILT-IN SAMPLING FUNCTIONS

Both the input and output waveforms may be sampled and held at arbitrary instants to produce the desired waveforms for time- and frequency-domain analyses of linear SCN's except for sensitivity analysis. The output waveforms may also be sampled with a train of impulse functions for z-domain analyses.

#### 7. SUBCIRCUIT FACILITY

Subcircuits, including analog and/or digital elements, may be defined with symbolic values for capacitances, VCVS gains, clocks, and other parameters. The symbolic values may then be replaced with actual values during each reference to a subcircuit. This facility provides a convenient means for building a library of often-used building-block circuits from which more complicated circuits may be pieced together. It also facilitates a hierarchical design approach.

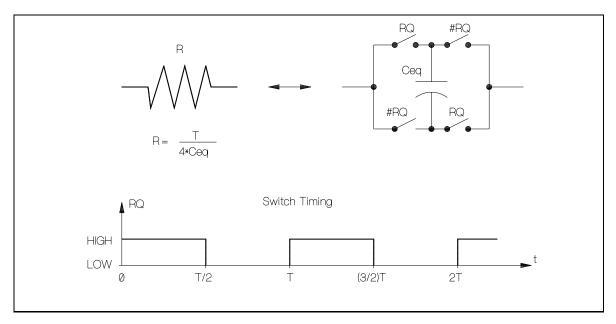

## 8. FINITE RESISTANCES, OPERATIONAL AMPLIFIER POLES, AND SWITCH PARASITICS

Finite resistances (say associated with nonideal switches or anti-aliasing filters) may be simulated by equivalent SC networks. To obtain good accuracy, the switches associated with the finite-resistor equivalent SC networks may be switched at a frequency much higher than both the input signal frequency and the switching frequency of the actual switches of the circuit. The time-constants introduced by the resistors may be longer than the length of an actual switching interval (i.e., the network need not be equilibrated).

Operational amplifiers with limited frequency response may also be simulated. The frequency response may be modeled with an RC network and then simulated with the R's replaced by equivalent SC networks.

Clock feedthrough from switch parasitics may be simulated in both the time and the frequency domains. The frequency-domain simulation of this effect is particularly efficient using the dc steady-state analysis capability of the program which does not require the direct computation of the Fourier components of any clock waveform.

To incorporate these higher order effects in a simulation, the subcircuit facility of the program may be used to advantage. A circuit can be simulated with, say, ideal elements at a high level of abstraction, or complex subcircuits including parasitics and nonidealities can be substituted for ideal elements to carry the simulation to a lower level. However, it must be warned that the simulation of these nonideal effects is computationally time consuming due to the need for higher switching rate to model the nonideal effects.

#### 9. INPUT FILE COMPATIBILITY WITH SWITCAP

The input parser in SWITCAP is completely rewritten to allow the flexibility necessary to add new features. However, the new parser in SWITCAP2 is designed such that any old SWITCAP input files can be used in SWITCAP2 without any modifications. Should any incompatibilities come up, please contact SWITCAP Distribution Center immediately.

Internally, SWITCAP2 consists of several different algorithms depending on the type of desired analysis. For time- and frequency-domain analyses (excluding group delay and sensitivity analyses) of linear SCN's, SWITCAP2 uses an algorithm based on the formulation published in [1, 2, 3, 4, 5, 6, 7, 8, 9]. This formulation, which was incorporated in the original SWITCAP [6, 7], uses a set of charge variables as the network variables for computation. The number of charge variables is typically very small. For example, an nth order filter implemented in a leap-frog configuration wherein the number of integrators is the same as the order would have n charge variables per switching interval. As a result of the small number of network variables, the iterative steps in the computation are very efficient. The most memory-intensive portion of the computation is in the preprocessing stage during which the network matrices to be used in the subsequent iterations are computed

and stored. Because of this memory requirement, a dynamic memory allocation scheme has been implemented. With this allocation scheme, the maximum complexity (number of elements times the number of unique switching intervals) of an SCN that can be simulated is limited solely by the user's computer memory size.

The analytical expressions that allow exact analyses of group delay and sensitivity for many-phase linear SCN's are derived from the above mentioned state charge variable formulation [10, 11]. The analytical expressions not only lead to efficient algorithms for computing the group delay and sensitivity but also retain efficiencies similar to those that were realized for simple time- and frequency-domain analyses using the state charge formulation.

The transient analysis of mixed SC/D networks is formulated in such a way that separate algorithms are used for analog, digital, and interface subgroups to take full advantage of their own properties. Detailed technical discussions of the algorithms and their applications can be found in [11, 12, 13].

This document is the user's guide for SWITCAP2. Chapter 2 of this guide gives an overview of the features of SWITCAP2 in a tutorial style. After reading this chapter, the user will be able to simulate most SCN's he or she is likely to encounter in practice. More advanced features or more subtle points of SWITCAP2 are described in the later chapters. The last chapter contains the SWITCAP2 Language Reference which is intended as a reference for users who are already familiar with SWITCAP2. The first-time user is encouraged to read through Chapter 2 first.

Columbia University welcomes all comments about the program and this manual. Comments can be addressed to:

SWITCAP Distribution Center Columbia University 411 Low Memorial Library New York, N.Y. 10027 U.S.A

## **Bibliography**

- [1] Y. P. Tsividis, "Analysis of switched capacitive networks," *IEEE Trans. Circuits Syst.*, vol. CAS-26, no. 11, pp. 935-947, Nov. 1979.

- [2] S. C. Fang and Y. P. Tsividis, "Modified Nodal Analysis with Improved Numerical Methods for Switched Capacitive Networks," in *Proc. IEEE Int. Symp. Circuits Syst.* (Houston, TX), pp. 977-980, Apr. 1980.

- [3] S. C. Fang, Y. P. Tsividis, and O. Wing, "Analysis of SCN's with Nonlinear and Time-Varying Elements Using Time-Invariant Charge Variables," in *Proc. IEEE Int. Symp. Circuits Syst.* (Rome, Italy), pp. 1-4, May 1982.

- [4] S. C. Fang, Y. P. Tsividis, and O. Wing, "Efficient algorithms for analyzing many-phase switched-capacitor networks," in *Proc. IEEE Int. Symp. on Circuits and Systems*, (Newport Beach, CA), pp. 60-63, May 1983.

- [5] S. C. Fang, Analysis, Computer Simulation, and Properties of Switched-Capacitor Networks, Ph.D. dissertation, Columbia University, New York, 1983.

- [6] S. C. Fang, Y. P. Tsividis, and O. Wing, "SWITCAP: A switched-capacitor network analysis program. Part I: basic features," *IEEE Circuits Systems Magazine*, vol. 5, no. 3, pp. 4-10, Sept. 1983.

- [7] S. C. Fang, Y. P. Tsividis, and O. Wing, "SWITCAP: A switched-capacitor network analysis program. Part II: advanced features," *IEEE Circuits Systems Magazine*, vol. 5, no. 4, pp. 41-46, Dec. 1983.

- [8] S. C. Fang, Y. P. Tsividis, and O. Wing, "State charge formulation of switched-capacitor networks containing nonlinear and time-varying elements," *IEEE Trans. Circuits Syst.*, vol. CAS-31, no. 11, pp. 968-974, Nov. 1984.

- [9] S. C. Fang, Y. P. Tsividis, and O. Wing, "Time- and frequency-domain analysis of linear switched-capacitor networks using state charge variables," *IEEE Trans. on Computer-Aided Design*, vol. CAD-4, no. 4, pp. 651-661, Oct. 1985.

- [10] K. Suyama and S. C. Fang, "Efficient state charge variable analyses of group delay and sensitivity for switched capacitor networks," *Proc. 29th Midwest Symp. on CAS*, Lincoln, NE, pp. 789-792, Aug. 1986.

- [11] K. Suyama, Analysis, Simulation, and Application of Linear and Nonlinear Switched-Capacitor and Mixed Switched-Capacitor/Digital Networks, Ph.D dissertation, Columbia University, New York, 1989.

- [12] K. Suyama, S. C. Fang, and Y. P. Tsividis, "Simulation of mixed switched-capacitor/digital networks with signal-driven switches," *IEEE J. Solid-State Circuits*, vol. SC-25, no. 6, pp. 1403-1413, Dec. 1990.

- [13] K. Suyama, S. C. Fang, and Y. P. Tsividis, "Simulation methods for mixed switched-capacitor/digital networks," To be published.

### Chapter 2

### **FUNDAMENTALS**

This chapter covers the basics of SWITCAP2. A user should be able to get started with running the program by reading just this chapter. It is recommended that this chapter be read first since the later chapters in this user's guide will assume a familiarity with the contents here. It is also recommended that this chapter be read sequentially for a similar reason.

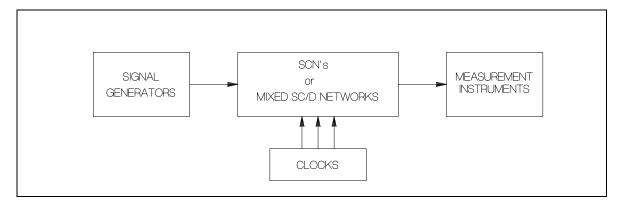

#### 2.1 Relation of SWITCAP2 to Laboratory Setup

The input format for SWITCAP2 has been designed to correspond as much as possible to actual laboratory setups which one might use for making measurements on SCN's and mixed SC/D networks. Figure 2.1 shows schematically such a possible setup. In this setup, the signal generators may be, for example, a sinewave oscillator or a square wave generator. The measurement instruments may be a spectrum analyzer or an oscilloscope. The clocks are control signals for turning on and off a set of switches inside the network. To describe this setup to SWITCAP2, the input file is divided into three sections: First, there is a TIMING SECTION in which all of the clock and timing data are specified. Next, there is a NETWORK SECTION in which the network is specified (topology and element values). Finally, there is an ANALYSIS SECTION in which the input signals and output measurements are specified.

In the following, two complete examples will be worked through from circuit diagram and timing waveform to the final SWITCAP2 input description and output printout. The first example is a simple SC integrator and it is used to describe various analysis facilities for linear SCN's. The second example explains simulation capabilities for mixed SC/D networks using a second-order sigma-delta modulator.

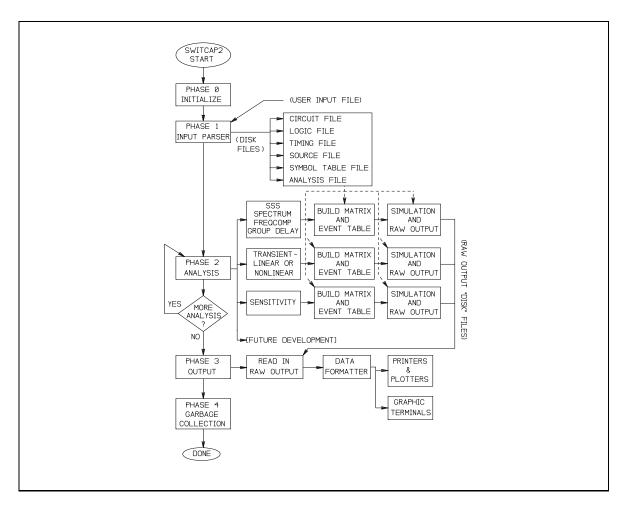

The overall architecture of the program is shown in Fig. 2.2. The input parser translates

Figure 2.1: General laboratory setup.

the user input file into several intermediate disk files. The files are then used to construct necessary matrices and event tables for each analysis.

#### 2.2 Linear SCN Example: A SC Integrator

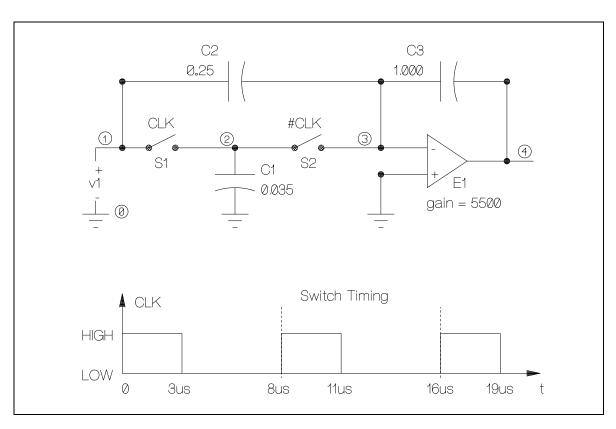

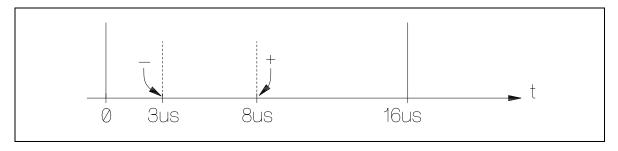

Consider the SCN and its switch timing diagram shown in Fig. 2.3. This circuit contains three capacitors, C1, C2 and C3, two switches, S1 and S2, and an operational amplifier E1. Switch S1 is controlled by the the clock CLK. The switch is closed when the clock is HIGH and is open when the clock is Low. Switch S2 is controlled by the complement value of CLK (this is indicated by the "#" sign before the clock name), so it is open when CLK is HIGH and closed when CLK is LOW. The clock CLK has a period of 8 us. The node numbers are enclosed in circles.

#### 2.2.1 Timing Section

The first thing we must describe to SWITCAP2 is the switch timing information. We shall call each instant at which a clock makes a transition a "clock time". Each clock time corresponds to a switching instant. In Fig. 2.3 the clock times are at 0 us, 3 us, 8 us, and so on. SWITCAP2 uses a scheme of specifying all clock time values **normalized to the period of a fictitious master clock**. In addition, the master clock period chosen must be such that the resulting normalized time can be expressed as a **rational number**. We define the duration of one Master Clock Period as one MCP unit of time. Looking at the timing diagram in Fig. 2.3, we see that if we had a master clock period of 8 us, then all clock times could be expressed in rational numbers of units of mcp. For example, 3 us would be equal to 3/8 mcp, 8 us would be 1mcp, and so forth. This timing can be specified to

Figure 2.2: SWITCAP2 overall structure.

Figure 2.3: A simple switched-capacitor network.

SWITCAP2 by the statements:

```

1 TIMING;

2 PERIOD 8e-6;

3 CLOCK clk 1 (0 3/8);

4 END:

```

There are four SWITCAP2 statements in (1-4). The indentation of each statement is arbitrary. The statement labels "1", "2", etc. are for reference only and are not part of the SWITCAP2 statements. The keywords "TIMING" and "END" define a TIMING block. (All keywords recognizable to SWITCAP2 will in this manual be written in CAPITAL letters, though this is not necessary for SWITCAP2 input file.) The middle two statements have the following meaning:

#### PERIOD 8e-6:

This statement defines the master clock period as being 8 us. It establishes the correspondence between 1mcp and an absolute unit of time.

#### CLOCK clk 1 (0 3/8);

This statement defines a switch-controlling clock. "clk" is the name of the clock. This name will later be referenced in the switch specification statements in the network section to indicate which switches are being controlled by which clocks. The "1" means that the period of this clock is 1mcp. The starting and ending times of the HIGH interval of the clock are at 0mcp and 3/8mcp, respectively. (Note that rational numbers are written as a ratio of two integers and not as a decimal.) Clock names must be a string of 78 or fewer alphanumeric characters, the first of which must be a letter (a-z).

#### \* IMPORTANT NOTE \*

It is important to keep in mind that all time values expressed here are in units of the master clock period defined in the PERIOD statement and *not* in units of the period of the individual switch-controlling clocks. For example, if another clock had a period of 16 us with HIGH intervals (0 us, 3 us), (16 us, 19 us), and so forth, it would be defined by the statement: CLOCK clk2 2 (0 3/8);

In each input file the period defined by the PERIOD statement is the only time base by which all clock times are reckoned.

In general, an SCN may have several switching-controlling clocks of different periods. Each clock may also have more than one HIGH intervals. (See Section 3.1 for more details.)

#### 2.2.2 Network Section

To describe the network topology and the element values in the circuit in Fig. 2.3, we can use the statements:

| 5  | CIRCUIT;          |

|----|-------------------|

| 6  | S1 (1 2) clk;     |

| 7  | S2 (2 3) #clk;    |

| 8  | C1 (2 0) 0.035;   |

| 9  | C2 (1 3) 0.250;   |

| 10 | C3 (3 4) 1.000;   |

| 11 | E1 (4 0 0 3) 5500 |

| 12 | V1 (1 0);         |

| 13 | $\mathrm{END};$   |

The keywords "CIRCUIT" and "END" define a CIRCUIT block. Statements (6-12) are the actual statements that describe the network elements. These statements follow the general format:

```

< r > < elementname > (< nodelist >) < elementvalue >;

```

where

- < r > is a key character indicating the type of element being defined. The key character designations are:

- S for switches

- C for capacitors

- E for voltage-controlled voltage sources (VCVS)

- V for independent voltage sources

- < elementname > is a string of alphanumeric characters less than 78 characters long which serves as a label for the element. Element names among elements of the same type should be unique.

- < nodelist > is a list of the nodes to which the element is connected. This list must be enclosed in parentheses. Node names may be any string of 78 or fewer alphanumeric characters. The ground node is always 0 (the digit zero).

- < elementvalue > gives the "value" of the element that is appropriate for the element.

The more specific features of statements (6-12) are described below. The portions of a statement being highlighted by the discussion are underlined.

S1 (1 2) clk;

#### S2 (23) #clk;

These are the clocks controlling the switches. The negate sign (#) indicates that the switch S2 is controlled by the complementary value of the clock "clk". A clock (without the # sign) must match one of the clock names specified in the TIMING block. The sequence of switch actions at each clock time is such that all switches to be opened are opened before any switch to be closed is closed, regardless of whether the switch is controlled by a clock or a complemented clock.

C1(20)0.035;

C2 (1 3) 0.250;

#### C3 (3 4) 1.000;

These are capacitance values. Since in SCN's the node voltages can depend only on the ratios of the capacitances, these capacitance values may be in arbitrary units.

#### E1 (4 0 0 3) 5500;

The branch relation of a VCVS can be written as

$$v(n+) - v(n-) = k \times [v(nc+) - v(nc-)]$$

where (n + n -) are the nodes of the controlled branch, (nc + nc -) are the nodes of the controlling branch, and k is the gain constant. In statement 11 the nodes (4 0 0 3) are in the order of (n + n - nc + nc -) and 5500 is the gain k.

#### V1 (1 0);

Note that no specific value is defined for the independent voltage source. In this network section we only define the nodes to which the source is connected. Since the actual value of the source will depend on the type of simulation we want to perform, we defer the source value specification to the analysis section. The name V1 will be referenced later in the analysis section when the value associated with this source is defined.

An unlimited number of each type of element (including independent voltage sources) may be specified in a CIRCUIT block. The network topology and the action of the switches must be such that within each switching interval:

- 1. the network remains connected (an open switch does not count as a connection); and

- 2. there are no loops of only independent voltage sources, controlled branches of VCVS's, and closed switches.

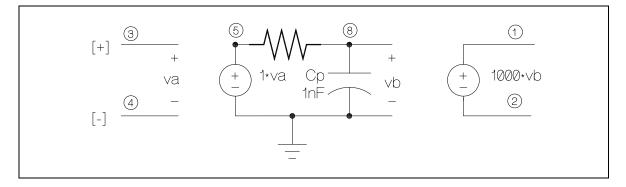

#### 2.2.3 Sinusoidal Steady-State Analysis

Having now specified the system timing and the network, we are ready to specify the analysis to be performed. For the moment let us suppose that we are interested in the sinusoidal steady-state (s.s.s.) response of this circuit from node (1) to node (4). By "the s.s.s. response" of this circuit at (any) frequency  $f_0$  we mean the following (we will define it in such a way as to correspond to an actual laboratory measurement using a spectrum analyzer): We will attach a sinusoidal oscillator to the circuit between node (1) and ground and set it to the frequency  $f_0$ . Let the input waveform be of the form

$$v_1(t) = A\cos(2\pi f_0 t + \phi), \text{ for all } t$$

(2.1)

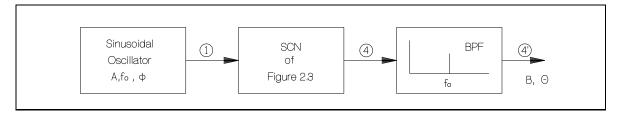

where A is magnitude and  $\phi$  is the phase angle of the cosine waveform. The output waveform  $v_4(t)$  on node (4) will contain a frequency component at frequency  $f_0$  and, in general, since the circuit is a time-varying network, will also contain frequency components at frequencies other than  $f_0$ . Now, to correspond to the operation of a spectrum analyzer, we will attach a very narrow bandpass filter (BPF) to the output at node (4), as shown in Fig. 2.4, and tune its center frequency to that of the input. The BPF is assumed to have unity gain and zero phase shift at its center frequency. Now the only frequency component present at the output of the BPF is the one whose frequency is the same as the input frequency. In other words, the SCN and the BPF together, viewed as a whole, now have a sinusoidal input and a steady-state sinusoidal output (with the same frequency as the input). We define the waveform at the output of the BPF to be the S.S.S. response of the SCN. We emphasize that the S.S.S. response is defined only with respect to the SCN/BPF system as a whole wherein the BPF has been tuned to the input frequency, and not with respect to the SCN by itself. We also emphasize that this definition is good for all frequencies and not just for those less than the Nyquist frequency. If the output of the BPF  $v'_4(t)$  is expressed in the form

$$v_4'(t) = B\cos(2\pi f_0 t + \theta), \text{ for all } t$$

(2.2)

where B is magnitude and  $\theta$  is the phase angle of the output waveform, then when A,  $f_0$ , and  $\phi$  are specified in s.s.s. analysis, the quantities B and  $\theta$  will be computed. Let us

Figure 2.4: Measuring Sinusoidal Steady-state Response.

say that we are interested in the s.s.s. response of the circuit from 0.01 Hz to 100 KHz at 15 frequency points (including the two end points) equally spaced on a logarithmic scale between these two frequency limits; and that we want a printout of the real and imaginary parts and a plot of the magnitude (in decibels) and phase of this response. We can specify these conditions to SWITCAP2 with the statements:

| 14 | ANALYZE SSS;               |

|----|----------------------------|

| 15 | INFREQ 0.01 100000 LOG 15; |

| 16 | SET V1 AC 1.0 0.0;         |

| 17 | PRINT $VR(4) VI(4)$ ;      |

| 18 | PLOT $VDB(4) VP(4);$       |

| 19 | $\mathrm{END};$            |

The keywords "ANALYZE" and "END" define an ANALYZE block. The keyword "SSS" indicates that we want s.s.s. analysis. The other statements specify the input and output conditions for the simulation:

#### INFREQ 0.01 100000 LOG 15;

This statement defines the input frequency values (the  $f_0$  in Eqn. 2.1). The keyword LOG causes the input frequency to be swept logarithmically. The other choice is to sweep linearly, which is specified by using LIN instead of LOG.

#### SET V1 AC 1.0 0.0;

This statement assigns a sinusoidal waveform to the independent voltage source V1. The independent source has been previously defined in the network section. The amplitude and phase (in degrees) of the input cosine waveform are 1.0 and 0.0 respectively. Thus the input waveform is given by

$$v_1(t) = 1.0\cos(2\pi(f_0t + 0.0/360))$$

If more than one independent sources are defined in the CIRCUIT block, then each source must be assigned with a separate SET statement.

#### PRINT VR(4) VI(4);

#### PLOT VDB(4) VP(4);

These statements specify the output variables to be printed and plotted. The variable VR(4) means the real part of the voltage on node (4), VI(4) means the imaginary part, and so forth. The key characters indicating the various parts of the output quantities are:

```

R real part

I imaginary part

M magnitude

P phase in degrees

DB magnitude in decibels

GD group delay (see page 31 for more details)

(omitted) real part by default

```

Each node listed in a PRINT or PLOT statement will be called an "output node". In general, output nodes in PRINT and PLOT statement may be different. (See Chapter 4 for other output options.)

To complete the input consisting of the statements (1-4), (5-13), and (14-19), we need to add only one more END statement as the last statement to indicate the end of the input file. Thus the following set of statements constitute a complete and acceptable input file to SWITCAP2.

```

TIMING;

PERIOD 8e-6;

CLOCK clk 1 (0 3/8);

END;

CIRCUIT;

S1 (1 2) clk;

S2 (2 3) \#clk;

C1 (2 0) 0.035;

C2 (1 3) 0.250;

C3 (3 4) 1.000;

```

```

E1 (4 0 0 3) 5500;

V1 (1 0);

END;

ANALYZE SSS;

INFREQ 0.01 100000 LOG 15;

SET V1 AC 1.0 0.0;

PRINT VR(4) VI(4);

PLOT VDB(4) VP(4);

END;

END;

```

This input file gives the output:

| frequency      | vr(4)       | vi(4)               |

|----------------|-------------|---------------------|

| 1.0000000D-02  | -5.4659D+03 | 4.3182D+02          |

| 3.16227766D-02 | -5.1769D+03 | 1.2933D+03          |

| 1.0000000D-01  | -3.3864D+03 | 2.6753D+03          |

| 3.16227766D-01 | -7.5967D+02 | 1.8973D+03          |

| 1.0000000D+00  | -8.6968D+01 | 6.8513D+02          |

| 3.16227766D+00 | -9.0466D+00 | 2.1978D+02          |

| 1.0000000D+01  | -1.1309D+00 | 6.9600D <b>+</b> 01 |

| 3.16227766D+01 | -3.3805D-01 | 2.2013D+01          |

| 1.0000000D+02  | -2.5875D-01 | 6.9611D+00          |

| 3.16227766D+02 | -2.5082D-01 | 2.2013D+00          |

| 1.0000000D+03  | -2.5003D-01 | 6.9611D-01          |

| 3.16227766D+03 | -2.4995D-01 | 2.2013D-01          |

| 1.0000000D+04  | -2.4994D-01 | 6.9611D-02          |

| 3.16227766D+04 | -2.4994D-01 | 2.2013D-02          |

| 1.0000000D+05  | -2.4994D-01 | 6.9611D-03          |

A letter "d" may sometimes appear next to a frequency, with the response at the frequency usually differing drastically from those at nearby frequencies. This indicates a frequency-overlap condition due to aliasing and can be seen whenever the input frequency is an integral multiple of half the sampling frequency. (See Section 3.2 for details.) Plot axes may sometimes be labeled with numbers prefixed by dollar (\$) signs, e.g., \$6.000. These are only the least significant digits of a number and are intended to show as much precision as possible in a limited space. (See Section 4.3 for details.)

#### 2.2.4 Input Format

Before we go further in describing the other types of analysis in SWITCAP2, let us state some general rules and features of the input format.

- 1. The three sections—TIMING, CIRCUIT, and ANALYZE—must be written in the order given. Statements within each block may, however, be written in any order.

- 2. The input may be free-formatted with an arbitrary number of spaces between words. More than one statements may be placed on the same line separated by semicolons (;).

- 3. A TITLE statement may be optionally added to the input file. A TITLE statement has the form:

#### TITLE:<anything>;

Everything between the colon and semicolon will be printed as a title in the output headings of the printout. The TITLE statement can be at most one line long. The statement can be anywhere<sup>1</sup> in the input file. Example:

#### TITLE:Switched-Capacitor Integrator (Fig. 2.2);

4. Comments may be inserted wherever a space is allowed. A comment is defined to be a character string that starts with the sequence /\*, followed by an arbitrary sequence of characters, and ends with the sequence \*/. Comment strings are allowed to cross line boundaries<sup>2</sup>. Comments do not affect the input processing and are treated simply as a string of blanks. Examples:

```

/* This is a valid comment */ (valid)

/* This comment

crosses a line boundary */ (also valid)

```

- 5. In the original SWITCAP, it was recommended that each statement be terminated with a semicolon (;). In SWITCAP2, the semicolon is not required for proper operation any more.

- 6. The input can be either in capital letters or in lower case letters.

- 7. All numerical values must be written in full as integers, rational numbers, or real numbers, whichever appropriate. Real numbers may be written in floating point notation, e.g. 1.2e3. Any scale factors such as MEG, P, etc. are *ignored*.

# 2.2.5 Piecewise-Constant Waveforms, Sampling, and Discrete-Time Frequency Response

So far we have considered sinusoidal steady-state analysis with a continuous sinusoidal input waveform for the circuit in Fig. 2.3. SWITCAP2 also has a set of built-in sampling functions for creating piecewise-constant waveforms and impulse-train waveforms for analysis. Using these functions, specifying input or output sampling amounts to adding just one statement in an ANALYZE block; no sampling circuitry need be added to the SCN. Moreover, sampling functions such as impulses, difficult to implement with real circuits but conceptually useful, may be simulated with ease.

<sup>&</sup>lt;sup>1</sup>The TITLE statement was required to be the first statement in the input file in the original SWITCAP.

<sup>&</sup>lt;sup>2</sup>This was not true in the original SWITCAP

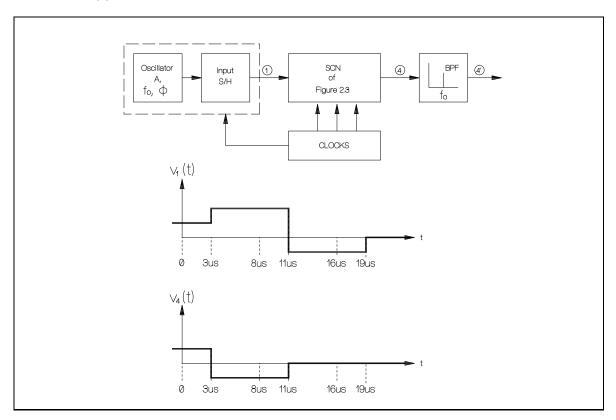

#### Input Sample-and-Hold

Suppose we have a laboratory setup as shown in Fig. 2.5 wherein a continuous sinusoidal waveform is first sampled-and-held by a sample-and-hold (S/H) circuit and then applied to the SCN in Fig. 2.3 at node (1). The waveforms v1(t) at node (1) and v4(t) at node (4) are also shown in Fig. 2.5. The input sampling instants are at 3 us, 11 us, and so forth with a period of 8 us. The waveform on node (4) changes only once per period because the input sampling instants have been chosen to coincide with the instants when switch S2 closes. In general, for other input sampling instants, this would not be the case. To produce the input waveform v1(t) in SWITCAP2, we can use the two statements:

Figure 2.5: Input Sample-and-Hold.

- 20 SET V1 AC 1.0 0.0;

- SAMPLE INPUT HOLD 1 3/8+;

Statement 20 defines a continuous sinusoidal waveform as before. Statement 21 effectively places an S/H circuit between this continuous-waveform source and node (1) as shown in Fig. 2.5. The "1" means that the period of the S/H is 1mcp or 8 us (mcp is defined by the PERIOD statement in Section 2.2.1). The "3/8+" means that a sampling action occurs at the instant just after the time 3/8mcp (3 us).

Our definition of sinusoidal steady-state response is still valid even with the input S/H circuit in place. Of course, the definition now applies to the total system consisting of the S/H, the SCN, and the BPF. To determine the s.s.s. response in Fig. 2.5 we can use the statements:

| 22 | ANALYZE SSS;               |

|----|----------------------------|

| 23 | INFREQ 0.01 100000 LOG 15; |

| 24 | SET V1 AC 1.0 0.0;         |

| 25 | SAMPLE INPUT HOLD 1 3/8+;  |

| 26 | PLOT $VDB(4) VP(4);$       |

| 27 | $\mathrm{END};$            |

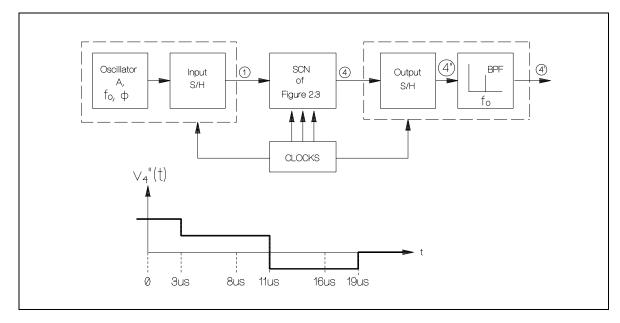

#### Output Sample-and-Hold

The waveform on node (4) may also be sampled with another sample-and-hold circuit before it is analyzed as shown in Fig. 2.6. Suppose v4(t) is now sampled-and-held with a period of 8 us at instants just before 3 us, 11 us, and so forth to produce the waveform v4''(t) shown in Fig. 2.6. Note that this is just a delayed version of the waveform v4(t) in Fig. 2.5. To simulate this sampling function, we can use the statement

This statement effectively places an S/H circuit between the output nodes of the SCN specified by the PRINT and PLOT statements and the BPF as shown in Fig. 2.6. The minus (-) sign after "3/8" means that the sampling action occurs at the instant just before the time 3/8mcp. Hence the values picked up by the output S/H at each of these sampling instants are the old values of the waveform on node (4).

To determine the sinusoidal steady-state response in Fig. 2.6 (s.s.s. response is now defined with respect to the total system consisting of the input S/H, the SCN, the output S/H, and the BPF) we can use the statements:

29 ANALYZE SSS;

```

30 INFREQ 0.01 100000 LOG 15;

31 SET V1 AC 1.0 0.0;

32 SAMPLE INPUT HOLD 1 3/8+;

33 SAMPLE OUTPUT HOLD 1 3/8-;

34 PLOT VDB(4) VP(4);

35 END;

```

Figure 2.6: Output Sample-and-Hold.

Input sampling and output sampling may be used independently of each other. Moreover, when used, the input and output sampling periods and sampling instants may be independent of each other and independent of the switch-controlling clock periods and clock times of the SCN. (More than one sampling instants per sampling period may be specified. See Section 3.1).

#### \* IMPORTANT NOTE \*

In each ANALYZE block, a SAMPLE INPUT statement applies to all SET statements and a SAMPLE OUTPUT statement applies to all PRINT and PLOT statements. Each ANALYZE block can have at most one SAMPLE INPUT statement and at most one SAMPLE OUTPUT statement.

#### **Output Impulse Sampling**

36

If we replace the output S/H in Fig. 2.6 with an impulse sampler (I/S), then the output of the BPF can, for a given timing relationship among the input S/H, the SCN, and the output I/S, be related to a discrete-time transfer function (DTTF) associated with the SCN. For example, suppose we use the statement

in place of statement 33. Then the output S/H in Fig. 2.6 becomes an I/S whose sampling instants are at the instants just after 3 us, 11 us, and so forth. The weight of each impulse is equal to the interval between successive pulses. Since the source oscillator's continuous sinusoidal waveform in Fig. 2.6 has unit amplitude and 0 phase and since both the input S/H defined by statement 31 and the output I/S defined by statement 36 have uniform sampling intervals and the same sampling instants, we have the following result: The magnitude and phase of the output v4'(t) of the BPF in Fig. 2.6 (with an output I/S in place of the output S/H), written in the form of Eq. 2.2, is simply the magnitude and phase of the DTTF

$$H(z) = \frac{V_4(z)}{V_1(z)} \tag{2.3}$$

where  $z = \exp(2\pi f_0 T)$  and where  $V_1(z)$  and  $V_4(z)$  are the z-transforms of the sequences  $v_1(t_0 + nT^+)$  and  $v_4(t_0 + nT^+)$ , with  $t_0 = 3$  us and T = 8 us. The DTTF in Eqn. 2.3 is only one of many DTTF's that can be implemented with the SCN in Fig. 2.3. We caution the reader that in general the particular DTTF implemented by an SCN is affected strongly by how the input sampling and output sampling are done in relation to the switch activities within the SCN, and the differences can be as drastic as having a lowpass response for one way of sampling and a highpass response for another. One should be precise in telling SWITCAP2 what to do.

In specifying sampling instants, the same rules apply to an output I/S as to an output S/H: An output I/S may be used without an input S/H, more than one sampling instants per sampling period may used, sampling intervals between successive impulses may unequal, and so forth. Of course, for these less restricted types of sampling, the output of the BPF we use for s.s.s. analysis may not correspond to any DTTF in the sense of Eq. 2.3. Nevertheless, the output of the BPF is well defined and may be computed.

#### Spectrum Analysis and Output Frequency Components

It has been noted that in sinusoidal steady-state analysis there is a bandpass filter (BPF) whose center frequency is matched to that of the input frequency, as shown in Fig. 2.4. It is quite possible to vary the center frequency of this BPF to pick up the other frequency

components in the output waveform. Of course, when this is done, the frequency of the sinusoid at the output of the BPF will not be the same as that of the input sinusoid, and we do not consider the output of the BPF a sinusoidal steady-state response in the strict sense of the definition we have given before. Nevertheless, the amplitude and phase of the sinusoid at the output of the BPF are well defined and may be computed. In SWITCAP2, to allow movement of the center frequency of the BPF, we must first specify

#### ANALYZE SPECTRUM;

This statement defines an ANALYZE block in a manner analogous to the ANALYZE SSS statement. All of the statements that are used in an ANALYZE SSS block can also be used in an ANALYZE SPECTRUM block, including SAMPLE INPUT and SAMPLE OUTPUT statements. In addition, we need one more statement to specify the output frequency components that we want to look at. This is done with the OUTFREQ statement. Let us say that we are interested in the spectral content of  $v_4(t)$  in the frequency range of 0 Hz to 300 KHz for two input frequencies,  $f_0 = 100$  Hz and  $f_0 = 1000$  Hz, for the circuit in Fig. 2.3. These frequency components can be computed with the statements

| 37 | ANALYZE SPECTRUM;        |

|----|--------------------------|

| 38 | INFREQ 100 1000 LOG 2;   |

| 39 | OUTFREQ 0 300e3 SCANNED; |

| 40 | SET V1 AC 1.0 0.0;       |

| 41 | PLOT $VDB(4)$ ;          |

| 42 | $\mathrm{END};$          |

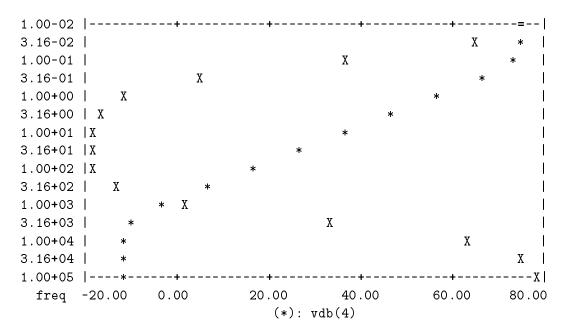

Statement 39 is the only new statement here. It specifies that the range of the output frequency components is 0 to 300 KHz. The keyword "SCANNED" indicates that the output frequency is to be scanned in a fashion similar to the operation of a spectrum analyzer. The statements (37-42) result in the output:

```

Output frequency component(s) at output frequencies <outfreq> related to fixed input frequency f0 by <outfreq> = <n>*fs + <s>*f0.

f0 = 1.00000000D+02

fs = 1.25000000D+05

```

```

(*): vdb(4)

outfreq -60.00

-40.00

-20.00

0.00

20.00

1 -1 1.2490+05 |========*

1 1.2510+05 |========

2 -1 2.4990+05 |======*

1 2.5010+05 |======*----+--

outfreq -60.00

-40.00

-20.00

0.00

20.00

(*): vdb(4)

Output frequency component(s) at output frequencies <outfreq> related

to fixed input frequency f0 by \langle \text{outfreq} \rangle = \langle \text{n} \rangle * \text{fs} + \langle \text{s} \rangle * \text{f0}.

______

f0 = 1.00000000D+03

fs = 1.25000000D+05

(*): vdb(4)

outfreq -60.00 -50.00

-40.00

-30.00

-20.00

-10.00

0.00

```

The magnitude and phase quantities computed in SPECTRUM analysis are those of the SINUSOIDAL WAVEFORM at the output of the BPF in Fig. 2.4. These quantities are related to the waveform by Eq. 2.2 (with  $f_0$  replaced by the actual output frequency). Note that apart from the uniform spacing of the frequency components, the SWITCAP2 output above corresponds to what one would observe on the screen of a laboratory spectrum analyzer.

1 2.5100+05 |=======\*+-----+-----+-----+

-40.00

-30.00

(\*): vdb(4)

-20.00

-10.00

0.00

1 -1 1.2400+05 |========\* 1 1 1.2600+05 |==========

outfreq -60.00 -50.00

2 -1 2.4900+05 |=======\*

Another way to analyze the output frequency components is to use the ANALYZE FRE-QCOMP statement. ANALYZE FRE-QCOMP is very similar to ANALYZE SPECTRUM although the point of view is slightly different. In both analyses, we consider the output

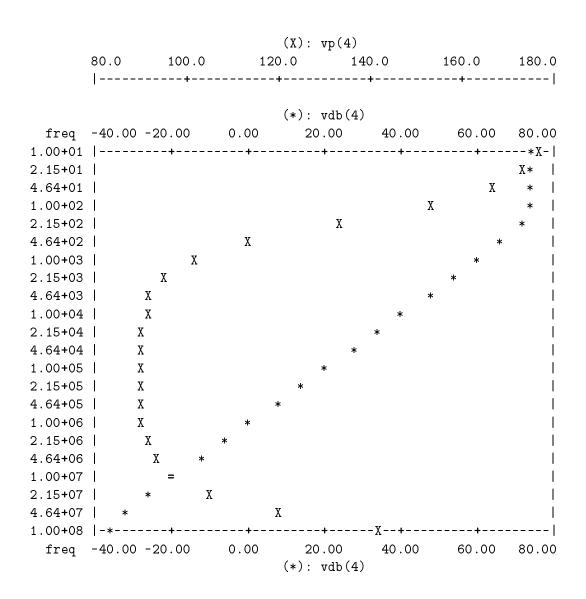

frequency components at frequencies  $nf_s + f_0$  and  $nf_s - f_0$ , where  $f_0$  is the input frequency,  $f_s$  is the switching frequency, and n is an integer. In SPECTRUM analysis, we view the input frequency  $f_0$  as being fixed while the index n is varied. In FREQCOMP analysis the index n is considered fixed while the input frequency  $f_0$  is varying. FREQCOMP analysis corresponds more closely with the viewpoint of using an SCN as a frequency modulator. For example, suppose we are interested in the output frequency components in the frequency range from 250 kHz to 300 kHz for inputs in the frequency range from 10 kHz to 50 kHz for the circuit in Fig. 2.3. This analysis can be obtained by the statements.

```

43 ANALYZE FREQCOMP;

44 INFREQ 10e3 50e3 LIN 9;

45 OUTFREQ 250e3 300e3 SCANNED;

46 SET V1 AC 1.0 0.0;

47 PLOT VDB(4) VP(4);

48 END;

```

The resulting output is

```

Output frequency component(s) at output frequencies related to input frequencies by:

<outfreq> = 2 * fs + <infreq> fs = 1.25000000D+05

```

```

(X): vp(4)

0.0 100.0

-200.0 -100.0

200.0

infreq outfreq

(*): vdb(4)

10**+03 10**+03 -52.75 -52.50 -52.25

-52.00

-51.75

-51.50 -51.25

15.000 265.00 | X

20.000 270.00

25.000 275.00 |

X

30.000 280.00 |

X

35.000 285.00 |

X

40.000 290.00 |

X

```

The discontinuity in the phase function in this plot is an artifact of the computation. Actually the phase is around 180 deg, which is the same as -180 deg.

#### Group Delay Analysis

SWITCAP2 can compute group delay of linear SCN's exactly without using any numerical method to compute derivatives. It is assumed in SWITCAP2 that group delay is defined only at the fundamental frequency that is the same as the input frequency. Let us first define group delay. Let a complex function be of the form  $F(\omega) = |F(\omega)|e^{j\phi(\omega)}$ . Then, the group delay of the function  $F(\omega)$  is defined as:

$$\tau(\omega) = -\frac{\partial \phi(\omega)}{\partial \omega} = -\operatorname{Im}\left[\frac{1}{f(\omega)} \frac{\partial F(\omega)}{\partial \omega}\right]$$

(2.4)

where  $Im[\cdot]$  denotes the operation "imaginary part of".

Since SWITCAP2 only computes group delay at the fundamental frequency, it is clear that SWITCAP2 computes the group delay of the output of the BPF in Fig. 2.4 ( $v'_4(t)$  in Eqn. 2.2), if node (4) is taken as an output. Therefore, the input format to request group delay computation is simply to add VGD in PRINT and PLOT statements in s.s.s. analysis. For example, if we want to compute the group delay of node (4) from 1 Hz to 10 Hz, we can specify the following statements instead of statements (14 - 19):

| 49 | ANALYZE SSS;                 |

|----|------------------------------|

| 50 | INFREQ 1 10 LIN 15;          |

| 51 | SET V1 AC 1.0 0.0;           |

| 52 | PRINT $VDB(4) VP(4) VGD(4);$ |

| 53 | PLOT $VDB(4) VP(4) VGD(4)$ ; |

| 54 | $\mathrm{END};$              |

The above input file gives the following output:

| freq                        | uency   |                     | vdb(4            | )     | νp    | (4)             | νę    | gd(4)             |                  |   |

|-----------------------------|---------|---------------------|------------------|-------|-------|-----------------|-------|-------------------|------------------|---|

| 1.00000                     | 000D+00 |                     | 5.6785D          | +01   | 9.72  | 34D+01          | 1.97  | 770D-02           |                  |   |

| 1.64285                     |         |                     | 5.2516D          |       |       |                 |       |                   |                  |   |

| 2.28571                     | 429D+00 |                     | 4.9660D          |       |       | 17D+01          | 3.78  | 368D-03           |                  |   |

| 2.92857                     | 143D+00 |                     | 4.7513D          |       |       |                 |       |                   |                  |   |

| 3.57142                     | 857D+00 |                     | 4.5792D          | +01   | 9.21  | 03D+01          | 1.52  | 202D-03           |                  |   |

| 4.21428                     | 571D+00 |                     | 4.4356D          | +01   | 9.18  | 07D+01          | 1.07  | 761D-03           |                  |   |

| 4.85714                     | 286D+00 |                     | 4.3123D          | +01   | 9.15  | 93D+01          | 7.96  | S15D-04           |                  |   |

| 5.50000                     | 000D+00 |                     | 4.2044D          | +01   | 9.14  | 31D+01          | 6.08  | 344D-04           |                  |   |

| 6.14285                     | 714D+00 |                     | 4.1085D          | +01   | 9.13  | 07D <b>+</b> 01 | 4.76  | 348D-04           |                  |   |

| 6.78571                     | 429D+00 |                     | 4.0221D          | +01   | 9.12  | 08D <b>+</b> 01 | 3.80  | 019D-04           |                  |   |

| 7.42857                     | 143D+00 |                     | 3.9435D          | +01   | 9.11  | 29D <b>+</b> 01 | 3.07  | 780D-04           |                  |   |

| 8.07142                     | 857D+00 |                     | 3.8714D          | +01   | 9.10  | 64D+01          | 2.51  | L99D-04           |                  |   |

| 8.71428                     | 571D+00 |                     | 3.8048D          | +01   | 9.10  | 11D+01          | 2.08  | 307D-04           |                  |   |

| 9.35714                     | 286D+00 |                     | 3.7430D          | +01   | 9.09  | 67D <b>+</b> 01 | 1.72  | 289D-04           |                  |   |

| 1.00000                     | 000D+01 |                     | 3.6853D          | +01   | 9.09  | 31D <b>+</b> 01 | 1.44  | 127D-04           |                  |   |

|                             |         |                     |                  | .00   |       | 03<br>10.0      |       |                   | 20.00<br>        |   |

|                             |         |                     |                  | ( X ) | ): vp | (4)             |       |                   |                  |   |

|                             | .00     | 92.<br><b>+</b>     | 00<br>           |       | 94.0  | 0               | 9     | 96.00<br><b>+</b> | 98.00<br>        | ) |

|                             |         |                     |                  | 5.00  |       | 50.0            |       |                   | 60.00<br>  8x-*- |   |

|                             |         |                     |                  |       |       |                 |       |                   |                  |   |

| 1.643                       |         |                     | 0/               |       |       |                 |       | •                 |                  | ı |

| 2.286                       |         | •                   | % X              | Λ     |       | Α.              |       | •                 | l                | İ |

| 2.929  <br>3.571            |         | •                   | / <sub>6</sub> A | . *   | *     | •               |       | •                 | <br>             | İ |

| 4.214                       |         | . X%                |                  | ·     |       | •               |       | •                 | <br>             | İ |

|                             |         |                     |                  | •     |       | •               |       | •                 | l<br>I           | ì |

|                             |         |                     | • • • •          | • •   | • •   | • • •           | • • • |                   | · · · ·          | ì |

|                             |         |                     | •                | •     |       | •               |       | •                 | <br>             | ì |

| 4.857  <br>5.500  <br>6.143 |         | . X % X . % X . % * | *<br>*           | •     | • •   | · · · ·         |       |                   |                  |   |

```

6.786

* . %

7.429 L

X

8.071

. . .*X . % . .

8.714

%

9.357 I

* X

10.000 |---*-X---%--

40.00

freq 35.00

50.00

55.00

60.00

(*): vdb(4)

```

It should be emphasized that a frequency overlap condition may occur whenever the input frequency is an integral multiple of half the sampling frequency. When this condition happens, group delay at the frequency becomes meaningless. See Section 3.2 for more details.

SAMPLE INPUT HOLD, SAMPLE OUTPUT HOLD, and SAMPLE OUTPUT IM-PULSE can also be used in group delay analysis.

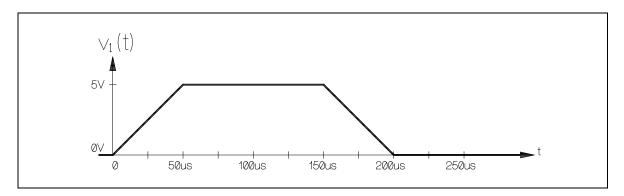

#### Transient Analysis

SWITCAP2 can also analyze the transient response of an SCN given a prescribed input waveform. Suppose now that the input to the circuit in Fig. 2.3 has a pulse waveform shown in Fig. 2.7. The transient response of the circuit to such an input can be analyzed with the statements

| 55 | ANALYZE TRAN;                                 |

|----|-----------------------------------------------|

| 56 | TIME $0+40\ 20/8$ ;                           |

| 57 | SET V1 PULSE 0 5 0 50e-6 50e-6 100e-6 500e-6; |

| 58 | PLOT $V(4) V(1)$ ;                            |

| 59 | END:                                          |

Here, the ANALYZE block starts with ANALYZE TRAN for transient analysis. Two new statements are used.

#### TIME $0+40\ 20/8$ ;

This statement specifies the range of time values for transient analysis. It is the time domain counterpart to the INFREQ statement for frequency domain analyses discussed previously. The time values are expressed in mcp (master clock period defined by the PERIOD statement in Sec. 2.2.1). This statement says: compute the response for time values from 0 mcp to 40 mcp at intervals of every 20/8 mcp. The

Figure 2.7: Input Pulse Waveform.

plus (+) sign appended to the "0" tells the program to output the values at the instants just after each output instant in case there are discontinuities in the output waveform. A minus (-) sign can also be used and it would mean "before each output instant". The time values for output must all be after the time  $\theta$ -.

#### SET V1 PULSE 0 5 0 50e-6 50e-6 100e-6 500e-6;

This statement assigns the pulse waveform shown in Fig. 2.7 to the independent voltage source V1. The sequence of numbers after the keyword PULSE are

**0** initial voltage of the pulse

5 peak voltage of the pulse

**0** delay time to the start of the pulse

50e-6 rise time

50e-6 fall time

100e-6 pulse width

500e-6 period for repeated pulses.

When specifying time-domain waveforms in a SET statement, all time values are expressed in absolute time units (not in mcp's).

SAMPLE INPUT HOLD and SAMPLE OUTPUT HOLD statements may also be used in an ANALYZE TRAN block. SAMPLE OUTPUT IMPULSE statements are not allowed. Other types of waveforms besides PULSE may also be defined (see Sec. 3.3).

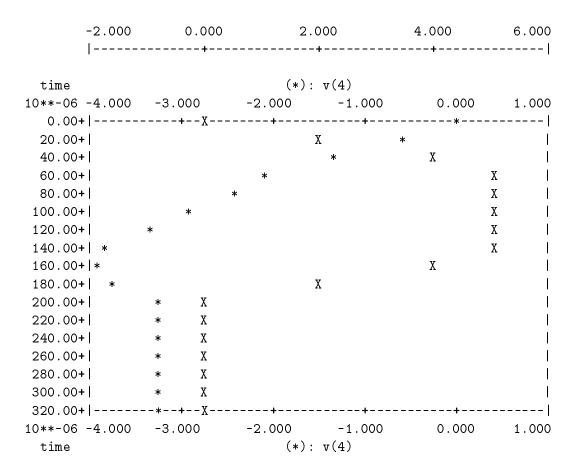

The statements (55-59) give the result

(X): v(1)

#### Subcircuits

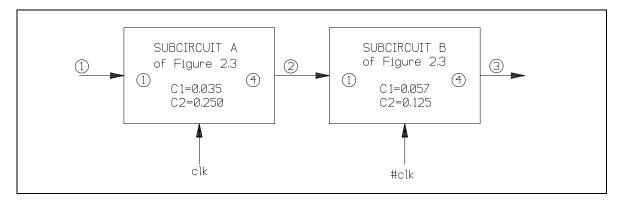

The subcircuit facility in SWITCAP2 allows large circuits to be built up from smaller subcircuits in a hierarchical manner. To see how this facility can be used, suppose now that we wish to cascade two circuits, each like the circuit in Fig. 2.3, to form one circuit as shown in Fig. 2.8. Let Subcircuit A have identical values as the circuit in Fig. 2.3. In Subcircuit B, let C1 and C2 have different values and let the switches be operated in the opposite phase from that of Subcircuit A, as shown in Fig. 2.8.

To simulate the circuit in Fig. 2.8, we can first define a subcircuit with the statements

60 SUBCKT (1 4) lowpass (K:phi P:cap1 P:cap2); 61 S1 (1 2) phi; 62 S2 (2 3) #phi;

Figure 2.8: Cascade of Two Circuits.

| 63 | C1 (2 0) cap1;     |

|----|--------------------|

| 64 | C2 (1 3) cap2;     |

| 65 | C3 (3 4) 1.000;    |

| 66 | E1 (4 0 0 3) 5500; |

| 67 | END;               |

The keywords "SUBCKT" and "END" define a SUBCKT block. Some of the features of statements (60-66) are as follows.

### SUBCKT (1 4) lowpass (K:phi P:cap1 P:cap2);

Nodes (1) and (4) are the "terminal" nodes through which the subcircuit may be connected to the outside world (besides the ground node). All nodes used within the subcircuit other than the ones declared here and other than the ground node are considered internal to the subcircuit and cannot be seen by rest of the world. For example, nodes (2) and (3) are internal nodes in this subcircuit. The names of the nodes (both the terminal nodes and the internal nodes) follow the same rules as node names used for elements (see Sec. 2.2.2) and may be arbitrarily chosen. One exception to the rules is the length of internal node names within a subcircuit block. This will be explained in page ??. Node names in different SUBCKT blocks are completely independent. The ground node, however, is always the node (0) and is always the same node in a subcircuit as the ground node in the main circuit. There is a restriction on the length of the name of nodes and elements. This will be explained in page 38.

"lowpass" is the name of the subcircuit. It is the name by which this subcircuit will be referred when it is later used.

The sequence "K:phi" says that phi is a *symbolic clock*. <sup>3</sup> The symbolic clock name, phi in this instance, may be arbitrarily chosen. This means that phi can be used anywhere in the subcircuit where a clock name would normally go in identifying the clock controlling a switch.

The sequences "P:cap1" and "P:cap2" say that cap1 and cap2 are *symbolic values*. <sup>4</sup> This means that cap1 and cap2 can be used anywhere in the subcircuit where a real number would normally go, e.g., a capacitance value.

Symbolic names such as phi and cap1 must be a string of 78 or fewer alphanumeric characters, the first of which must be a letter (a-z).

#### IMPORTANT NOTE

In the original SWITCAP, the first parentheses contain analog terminal nodes and the second parentheses contain parameters. However, in SWITCAP2, this format may be relaxed. The only restriction in SUBCKT definition is to keep two sets of parenthesis around the subcircuit name. For example, any of the following produces the same result.

```

SUBCKT (1 4) lowpass (K:phi P:cap1 P:cap2);

SUBCKT (1 4 K:phi P:cap1 P:cap2) lowpass ();

SUBCKT () lowpass (K:phi P:cap1 P:cap2 1 4);

```

- S1 (1 2) phi;

- S2 (2 3) #phi;

These switches are controlled by symbolic clocks. Note that it is ok to complement a symbolic clock.

- C1 (2 0) cap1;

- C2 (1 3) cap2;

- C3 (3 4) <u>1.000;</u>

Symbolic values and constant values can both be used within a subcircuit.

Now to cascade the two circuits together, we can use the statements

68 CIRCUIT;

<sup>&</sup>lt;sup>3</sup>In the original SWITCAP, the letter K was needed to tell SWITCAP that what comes after the colon (:) is a symbolic clock. However, "K:" is not required in SWITCAP2 any more.

<sup>&</sup>lt;sup>4</sup>Again, "P:" can be omitted.

```

69 Xa (1 2) lowpass (clk 0.035 0.250);

70 Xb (2 3) lowpass (#clk 0.057 0.125);

71 V1 (1 0);

72 END;

```

In statements 69 and 70, the key character "X" causes the subcircuit defined previously to be "pulled" into the circuit. We call this action a "subcircuit call." The terminal nodes of the subcircuits are now assigned to actual nodes and the symbolic parameters in the subcircuits are replaced by the actual values to be used. Note that it is ok to pass a complemented clock name to a subcircuit. The names "a" and "b" in statements 69 and 70 given to the subcircuit calls follow the same rules as element names (see Sec. 2.2.2) and may be arbitrarily chosen.

Subcircuit definitions may also contain subcircuit calls. In these definitions, symbolic parameters may also be passed to the subcircuit call. **Independent voltage sources are not allowed in SUBCKT blocks.**

#### IMPORTANT NOTE

Internally, element and node names within a subcircuit are resolved by concatenating names. For example, when the above subcircuit definition "lowpass" is called in CIRCUIT through statement 69, then the name for C1 in the subcircuit definition becomes C1.Xa and the internal node 2 becomes 2.Xa. Therefore, the length of the capacitor and node name is 5 and 4, respectively. SWITCAP2 currently allows the length of this *internal* name to be 78 characters. Thus, a caution must be taken when many layers of subcircuit calls are used.

SUBCKT blocks must be placed in an input file in the order

TIMING block

SUBCKT block(s)

SUBCKT block(s) CIRCUIT block ANALYZE block(s)

SUBCKT blocks may be written in any order among themselves so long as a subcircuit is first defined before is called.

## 2.2.6 Sensitivity Analysis

As in the case with group delay analysis, sensitivity is obtained only at the fundamental frequency that is the same as the input frequency. First, the definition of sensitivity is given.

Let a complex function be of the form  $F(\omega) = |F(\omega)|e^{j\phi(\omega)}$ . Then, the first order relative sensitivity of the function  $F(\omega)$  with respect to a network parameter  $\alpha_i$  is defined as:

$$S_{\alpha_{i}}^{F(\omega)} = \frac{\alpha_{i}}{F(\omega)} \frac{\partial F(\omega)}{\partial \alpha_{i}} = \frac{\partial \ln F(\omega)}{\partial \ln \alpha_{i}} = \frac{\alpha_{i}}{|F(\omega)|} \frac{\partial |F(\omega)|}{\partial \alpha_{i}} + j \alpha_{i} \frac{\partial \phi(\omega)}{\partial \alpha_{i}}.$$

(2.5)

The more meaningful forms of the above equation are the magnitude  $S_{\alpha_i}^{|F(\omega)|}$  and phase  $S_{\alpha_i}^{\phi(\omega)}$  sensitivities with respect to a network parameter  $\alpha_i$ . They are defined respectively as follows:

$$S_{\alpha_i}^{|F(\omega)|} = \frac{\alpha_i}{|F(\omega)|} \frac{\partial |F(\omega)|}{\partial \alpha_i} = \text{Re}\left[S_{\alpha_i}^{F(\omega)}\right]$$

(2.6)

and

$$S_{\alpha_i}^{\phi(\omega)} = \alpha_i \frac{\partial \phi(\omega)}{\partial \alpha_i} = \operatorname{Im} \left[ S_{\alpha_i}^{F(\omega)} \right]$$

(2.7)

where Re[·] and Im[·] denote the operations "real part of" and "imaginary part of", respectively. Note that if  $|F(\omega)|$  is zero then the magnitude sensitivity is defined as follows:<sup>5</sup>

$$S_{\alpha_i}^{|F(\omega)|} = \alpha_i \frac{\partial |F(\omega)|}{\partial \alpha_i} \tag{2.8}$$

## **IMPORTANT NOTE**

SWITCAP2 computes  $S_{\alpha_i}^{F(\omega)}$ , therefore, when selecting the form of the output the real part must be requested if magnitude sensitivity is desired and the imaginary part must be requested if the phase sensitivity is desired. (This corresponds to "VR" and "VI" in SWITCAP2)

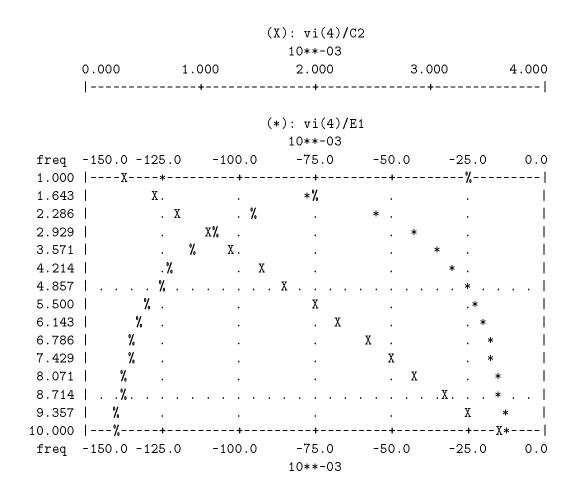

In SWITCAP2, the sensitivity analysis is invoked by specifying ANALYZE SENS block. Since the sensitivities are only computed at the fundamental frequency as explained before, the specification of ANALYZE SENS is almost the same as ANALYZE SSS block. For example, if we want to compute the magnitude and phase sensitivities of the circuit in Fig. 2.3 with respect to C1, C2, and E1 from 1 Hz to 10 Hz, we can specify the following statements:

- 73 ANALYZE SENS;

- 74 INFREQ 1 10 LIN 15;

- 75 SET V1 AC 1.0 0.0;

<sup>&</sup>lt;sup>5</sup>For more details on definition of sensitivity see: Jiri Vlach and Kishore Singhal: Computer Methods for Circuit Analysis and Design. Van Nostrand Reinhold, New York, 1983

| 76 | PERTURB C1 C2 E1      |

|----|-----------------------|

| 77 | PRINT $VR(4) VI(4)$ ; |

| 78 | PLOT $VR(4) VI(4)$ ;  |

| 79 | END;                  |

The descriptions of INFREQ, SET, PRINT, and PLOT are the same as in Sec. 2.2.3. More detailed descriptions are also available in Chap. 3. The only new statement is PERTURB.

#### PERTURB C1 C2 E1:

This line specifies the element names whose sensitivities are of interest. SWITCAP2 allows capacitor values and gain of VCVS's to be "perturbed". Despite the command name, PERTURB, numerical methods such as finite difference method are *not* used to compute derivatives. Rather, they are computed through analytical expressions.

An element within a subcircuit can be specified in PERTURB statement by concatenating names as explained in page 38. For example, if C1 in SUBCKT "lowpass" through a subcircuit call Xa (see page 38) is of interest, then type:

#### PERTURB C1.Xa

There must be only *one* PERTURB statement within ANALYZE SENS block. Multiple lines can be used to specify one PERTURB statement.

## PRINT VR(4) VI(4);

#### PLOT VR(4) VI(4);

The magnitude and phase sensitivities are requested at node 4.

**NOTE:** "VR" and "VI" were used to obtain magnitude and phase sensitivities respectively. If instead, "VM" and "VP" were used the output would be the magnitude and phase of the sensitivity  $(S_{\alpha_i}^{F(\omega)})$  itself. (see the above discussion on the definition of sensitivity)

#### IMPORTANT NOTE

Any sampling functions such as SAMPLE INPUT HOLD, SAMPLE OUTPOUT HOLD, and SAMPLE OUTPUT IMPULSE are currently *not* supported in ANALYZE SENS block.

Statements 73-79 produce the following output:

```

frequency

vr(4)/E1

vr(4)/C2

vr(4)/C1

1.0000000D+00

1.5994D-02 -4.4599D-05 9.8423D-01

1.64285714D+00

6.1297D-03 -4.4828D-05 9.9410D-01

2.28571429D+00

3.2867D-03 -4.4632D-05 9.9694D-01

2.92857143D+00

2.0944D-03 -4.4254D-05 9.9813D-01

3.57142857D+00

1.4845D-03 -4.3743D-05 9.9874D-01

4.21428571D+00

1.1314D-03 -4.3114D-05 9.9909D-01

4.85714286D+00

9.0885D-04 -4.2372D-05 9.9932D-01

5.5000000D+00

7.5960D-04 -4.1521D-05 9.9946D-01

6.5467D-04 -4.0560D-05 9.9957D-01

6.14285714D+00

6.78571429D+00

5.7812D-04 -3.9493D-05 9.9964D-01

7.42857143D+00

5.2056D-04 -3.8317D-05 9.9970D-01

8.07142857D+00

4.7619D-04 -3.7035D-05 9.9974D-01

4.4127D-04 -3.5645D-05 9.9978D-01

8.71428571D+00

9.35714286D+00

4.1330D-04 -3.4149D-05 9.9980D-01

1.0000000D+01

3.9054D-04 -3.2546D-05 9.9982D-01

vi(4)/E1

vi(4)/C2

vi(4)/C1

frequency

1.0000000D+00

-1.2455D-01 3.5338D-04 1.2422D-01

1.64285714D+00

-7.6571D-02 5.8637D-04 7.5999D-02

2.28571429D+00

-5.5193D-02 8.1815D-04 5.4385D-02

2.92857143D+00

-4.3129D-02 1.0495D-03 4.2087D-02

3.57142857D+00

-3.5387D-02 1.2807D-03 3.4113D-02

4.21428571D+00

-3.0000D-02 1.5117D-03 2.8494D-02

4.85714286D+00

-2.6035D-02 1.7427D-03 2.4297D-02

5.5000000D+00

-2.2995D-02 1.9737D-03 2.1026D-02

6.14285714D+00

-2.0591D-02 2.2046D-03 1.8390D-02

6.78571429D+00

-1.8642D-02 2.4355D-03 1.6210D-02

7.42857143D+00

-1.7030D-02 2.6664D-03 1.4366D-02

8.07142857D+00

-1.5674D-02 2.8972D-03 1.2780D-02

8.71428571D+00

-1.4518D-02 3.1281D-03

1.1393D-02

9.35714286D+00

-1.3521D-02 3.3589D-03 1.0165D-02

1.0000000D+01

-1.2652D-02 3.5898D-03 9.0647D-03

```

|       |      | \$85.00                     |   | 10**<br>\$90.   | .00           | \$95.<br>         |     |            |

|-------|------|-----------------------------|---|-----------------|---------------|-------------------|-----|------------|

|       |      | -42.50 -<br><b>+</b>        |   |                 | <-06<br>.50 - |                   |     |            |

|       |      |                             |   | (*): vi<br>10** | <-03          |                   |     |            |

| freq  | 0.00 | 5.00<br><b>%</b> - <b>+</b> |   | 10.             |               | 15 .              |     |            |

| 1.643 |      |                             | * |                 |               | <br>% .           |     | <br>       |

| 2.286 |      | * .                         | 7 |                 |               |                   | . % | l<br>İ     |

|       | X *  |                             |   | ·               |               | ·                 |     | <b>%</b> i |

|       | *X   | •                           |   |                 |               |                   |     | % i        |

|       | *    | Х .                         |   |                 |               |                   |     | <b>%</b>   |

| 4.857 | .*   | X                           |   |                 |               |                   |     | %          |

| 5.500 | *    | Х.                          |   | ,               |               | •                 |     | %          |

| 6.143 | *    |                             | X | •               |               | •                 |     | % I        |

| 6.786 | *    | •                           | X |                 |               |                   |     | % I        |

| 7.429 | *    | •                           |   | Х.              |               |                   |     | % I        |

| 8.071 | *    | •                           |   | ,               | X             | ,                 |     | % I        |

| 8.714 | *    |                             |   |                 |               | X                 |     | %          |

| 9.357 |      | •                           |   |                 |               | Х.                |     | % I        |

|       |      |                             |   |                 |               |                   |     |            |

| freq  | 0.00 | 5.00                        |   |                 |               | 15 .              | .00 | 20.00      |

|       |      |                             |   | 10**            |               |                   |     |            |

|       |      |                             |   | (*): VI         | c(4)/E1       |                   |     |            |

|       |      |                             |   | (%): vi<br>**01 | ·-03          |                   |     |            |

|       |      | 25.0<br><b>+</b>            |   | . 75<br>        |               | 100.0<br><b>+</b> |     |            |

# 2.3 Time-Domain analysis of Mixed SC/Digital Networks

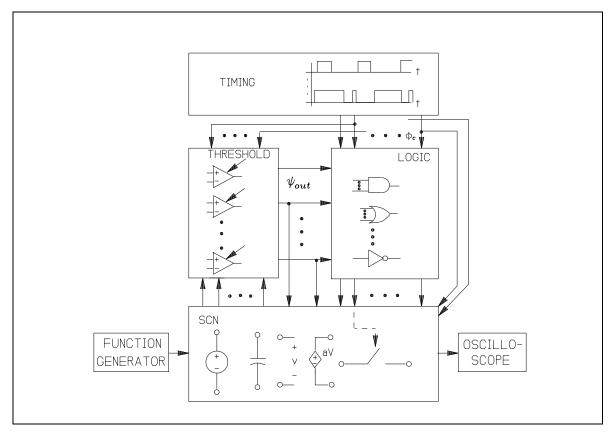

This section considers the time-domain simulation of mixed switched-capacitor/digital (SC/D) networks containing capacitors, independent and linear dependent voltage sources, switches, comparators, and logic gates. The switches, in particular, may be controlled by not only periodic waveforms but also non-periodic waveforms from the outputs of comparators and logic gates. Since this section explains considerably different types of SCN's from the previous example, we first define mixed SC/D networks, and then point out the syntax for new commands through several examples.

## 2.3.1 Definition of mixed SC/D networks

The structure of a mixed SC/D network defined in SWITCAP2<sup>6</sup> is shown in Fig. 2.9. The network is divided into four groups: SCN, THRESHOLD, TIMING, and LOGIC, which are interconnected as shown in the figure. The signal loop from the SCN to itself through the THRESHOLD and LOGIC allows signal-dependent modification of the SCN topology.

Figure 2.9: Structure of mixed SC/D network defined in SWITCAP2.

## SCN

The SCN may be composed of linear capacitors, independent voltage sources, linear voltage-controlled voltage sources, and ideal switches which are controlled by periodic or

<sup>&</sup>lt;sup>6</sup>More detailed discussions for the structure is published in [11, 12] in Chap. 1.

nonperiodic switch control signals. The switch control signals may be periodic or nonperiodic binary signals and they are supplied by the TIMING, THRESHOLD and LOGIC. The output variables of the SCN are node voltages; a subset of these voltages is monitored by the THRESHOLD as shown in Fig. 2.9. The topology of the network within the SCN can be set arbitrarily except for obvious pathological cases such as loops of voltage sources or disjoint networks.

#### THRESHOLD

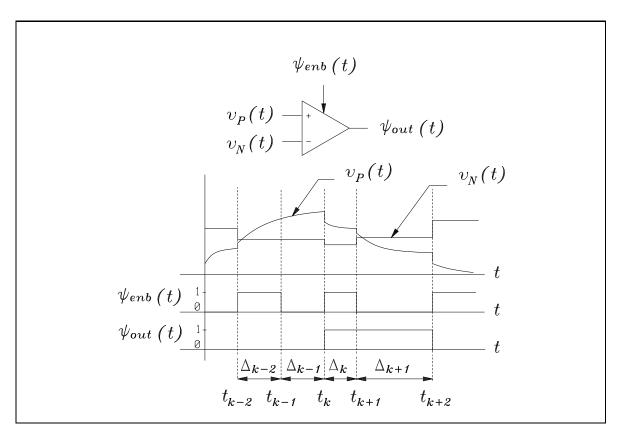

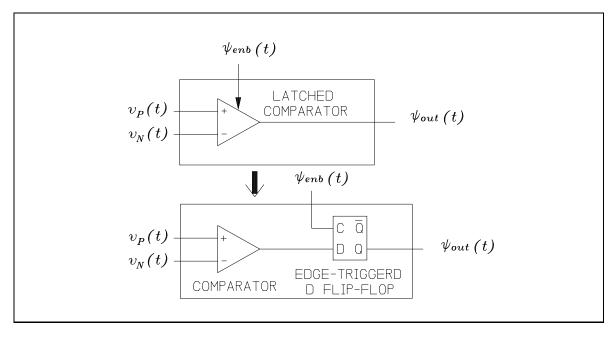

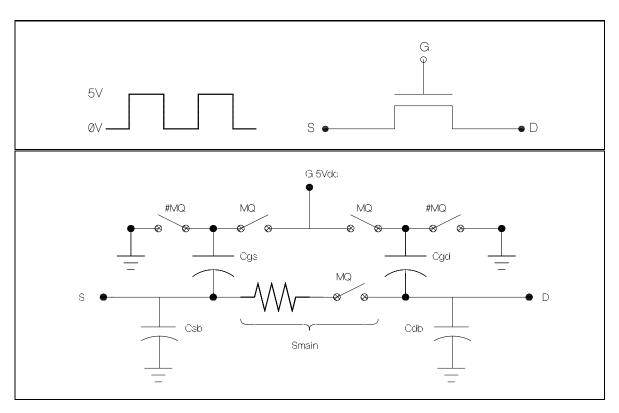

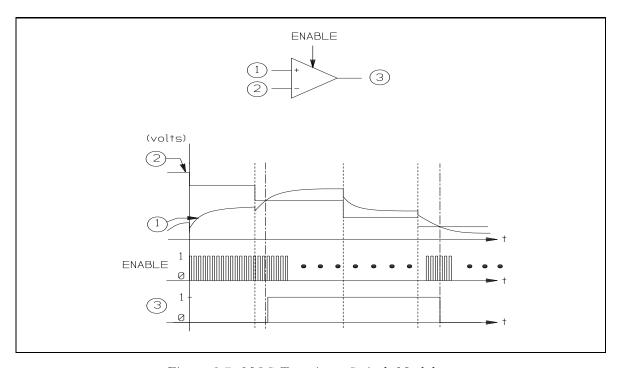

The THRESHOLD contains latched comparators which act as the interface from the SCN to the LOGIC. A latched comparator (Fig. 2.10) is a comparator with non-inverting and inverting input terminals (signals at the terminals are denoted as  $v_P(t)$  and  $v_N(t)$ , respectively as shown in Fig. 2.10), an enable terminal for a binary input  $\psi_{enb}(t)$ , and a binary output  $\psi_{out}(t)$ . The latched comparator samples its input signals  $v_P(t)$  and  $v_N(t)$  at the moment immediately before a switching instant  $t_k$  and, if warranted, changes its output value accordingly only when the enable signal  $\psi_{enb}(t)$  changes from 0 to 1 at  $t_k$ . Then, it latches the output value until the next rising edge is observed at the enable terminal. For example, in Fig. 2.10, the output  $\psi_{out}(t)$  of the latched comparator can change only at switching instants  $t = t_{k-2}, t_k$ , and  $t_{k+2}$ . Although the inputs  $v_P(t)$  and  $v_N(t)$  in Fig. 2.10 intersect at time instants within the intervals  $\Delta_{k-2}$  and  $\Delta_{k+1}$ , the output  $\psi_{out}(t)$  does not change at these instants. The enable signal must be periodic and is generated by the TIMING. It should be emphasized that the latched comparator can be modeled by a composite circuit which consists of an ideal comparator and an edge-triggered D-type flip-flop as shown in Fig. 2.11.

#### TIMING

This block generates periodic clock waveforms which may be used as enable signals for latched comparators in the THRESHOLD, inputs to the LOGIC, or switch control signals directly. Detail description of the SWITCAP2 syntax for clocks can be found in Sec. 2.2.1.

#### LOGIC

The LOGIC realizes boolean logic functions without internal clocks. Clocks should be provided by the TIMING. It consists of basic logic gates such as AND, OR, NOT, NAND, NOR, XOR, and XNOR. Multiple inputs are allowed for applicable gates. Arbitrary combinational and sequential logic circuits (with external clock signals supplied by the TIMING for the latter) can be designed using the available logic gates. All gates are assumed to have zero gate delay and, therefore, the outputs from the LOGIC are determined immediately at the instants that the inputs change their states. The inputs to the LOGIC may consist of

Figure 2.10: Latched comparator and its operation.

Figure 2.11: An equivalent model of a latched comparator.

the outputs of latched comparators in the THRESHOLD and of periodic clock waveforms generated by the TIMING as shown in Fig. 2.9.

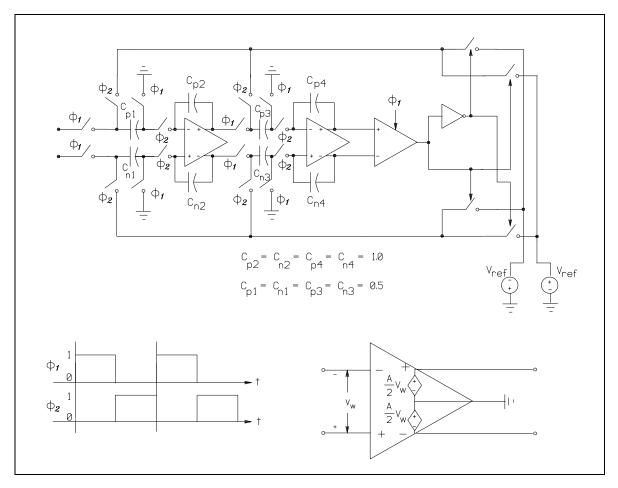

## 2.3.2 SC Sigma-Delta Modulator