wick, T. E. Seidel, and B. Y. Tsaur, Editors, p. 313, MRS, Pittsburgh (1986).

- 4. H. Z. Massoud, in Rapid Thermal Processing, R. B. Fair, Editor, p. 45, Academic Press, New York (1993). 5. D. K. Shih, W. T. Chang, S. K. Lee, Y. H. Ku, D. L.

- Kwong, and S. Lee, Appl. Phys. Lett., 52, 1698 (1988).

P. J. Wright, A. Kermani, and K. C. Saraswat, IEEE Trans. Electron. Devices, ED-37, 1836 (1990).

- 7. G. Weidner and D. Kruger, Appl. Phys. Lett., 62, 294 (1993)

- T. Y. Chu, W. T. Ting, J. Ahn, and D. L. Kwong, *This Journal*, **138**, L13 (1991).

- 9. U. Schwalke, M. Kerber, Ć. Mazure, and B. Breithaupt,

- J. Appl. Phys., 69, 1113 (1991).

R. Bienek and Z. Nenyei, *IEEE Trans. Electron Devices*, 40, 1706 (1993).

J. Ahn, W. Ting, T. Chu, S. N. Lin, and D. L. Kwong, *This Journal*, 138, L39 (1991).

Y.S. Kim, V. Okoda, K.M. Chang, D. Makin, D. Mart

- Y. S. Kim, Y. Okada, K. M. Chang, P. J. Tobin, B. Morton, H. Choe, M. Bowers, C. Kuo, D. Chrudimsky, A. S. Ajuria, and J. R. Yeargain, IEEE Electron Device Lett., EDL-14, 342 (1993)

- 13. H. Fukuda, T. Arakawa, and S. Ohno, Electron. Lett.,

26, 1505 (1990).

- 14. G. Eftekhari, This Journal, 140, 787 (1993).

- 15. H. Fukuda, M. Yasada, T. Iwabuchi, and S. Ohno, IEEE Electron. Device Lett., EDL-12, 587 (1991).

- 16. E. C. Carr and R. A. Buhrman, Appl. Phys. Lett., 63, 54 (1993).

- 17. T. S. Chao, W. H. Chen, S. C. Sun, and H. Y. Chang, This Journal, 140, 2905 (1993)

- 18. A. T. Wu, V. Murali, N. Cox, M. R. Frost, B. Triplett, and T. Y. Chan, Appl. Phys. Lett., 55, 1665 (1989)

- 19. U. Uchiyama, H. Fukuda, T. Hayashi, T. Iwabuchi, and S. Ohno, IEDM Tech. Dig., p. 425 (1990).

- 20. W. Ting, H. Hwang, J. Lee, and D. L. Kwong, Appl.

- *Phys. Lett.*, **57**, 2808 (1990). 21. M. L. Green, D. Brasen, K. W. Evans-Lutterodt, L. C. Feldman, K. Krisch, W. Lennard, H-T. Tang, L. Manchands, and M-T. Tang, Appl. Phys. Lett., 65, 848 (1994).

- 22. G. W. Yoon, A. B. Joshi, J. Kim, and D. L. Kwong, IEEE Electron. Device Lett., EDL-14, 231 (1993). 23. K. K. Hing and Y. C. Cheng, This Journal, 134, 2814

- (1987).

# A Kinetics Study of the Bond Strength of Direct Bonded Wafers

S. N. Farrens\* and C. E. Hunt\*

Electrical and Computer Engineering Department, Engineering Unit II, University of California, Davis, California 95616

# B. E. Roberds and J. K. Smith

Mechanical, Aeronautical, and Materials Engineering Department, Engineering Unit II, University of California, Davis, California 95616

### ABSTRACT

In order to determine whether low temperature wafer bonding is thermodynamically prohibited or simply a slow kinetic reaction, a systematic evaluation of the interface bond kinetics of silicon direct wafer bonding was performed over the temperature range of 200-1000°C for annealing times ranging from 15 min to 45 days. The tensile, shear, and torsion tests were developed to monitor the strength kinetics of silicon and silicon dioxide bonded wafers. The strength evolution is found to obey an Arrhenius relationship over the temperature range of 200-1000°C. Tensile strength of Si-Si bonded substrates varies from a minimum of 0.08 MPa at contact to a maximum of 4.25 MPa after high temperature thermal annealing. The failure of low temperature annealed samples to develop strong bonding in short periods of time has been correlated to microvoid formation at the interface as determined by TEM examination. Geometrical studies indicate that the microvoid formation is the result of trapped gases and can be reduced by appropriate choices of bonded geometries.

The unique geometry of bonded wafers can result in anomalous experimental measurements of interfacial strength. Misalignment of the test apparatus and stress intensity sites included in the tested interface region are the primary causes of erroneous measurements. Stress intensity sites include microvoids, wafer bevel at the extremities of a whole wafer, or regions which have developed locally strong bonds relative to adjacent areas of the wafer. In addition, the common measurements of the surface energy by the blade insertion technique has not been shown to be sensitive to small changes in the strength of the interface as a function of annealing conditions.<sup>1</sup> The tensile tests used in this work are very sensitive to kinetic changes and very reproducible. A further advantage of these tests is the direct measurement of the strength of the material under various loading conditions rather than attempting to measure the surface energy.

This work has focused on designing a grip system and sample geometry which maintains uniaxial loading of the specimen and eliminates or minimizes stress concentration sites in the sample. The isolation of the bonded area to a free standing mesa greatly enhances the reproducibility of the measurements and focuses the measurement to a welldefined region. This is not the case with other pull tests<sup>2</sup> or hydrostatic oil tests<sup>3</sup> in which supporting material in close proximity to the test area affects the experimental results.

The geometry described for these tests isolates the bonded interfaces, confines the strength measurement to that immediate area, and eliminates the stress intensity sites. This results in an overall improvement in reliability of the tests.

# Experimental

Materials selection .--- These experiments were designed to determine the kinetics of bond strength development for silicon to silicon (Si-Si), silicon to silicon dioxide (Si-Ox), and silicon dioxide to silicon dioxide (Ox-Ox) direct bonded wafers. The silicon wafers were all (100) oriented, n-type, silicon wafers. The silicon dioxide was a 0.4 µm thick thermal oxide grown in a water vapor atmosphere at 1100°C

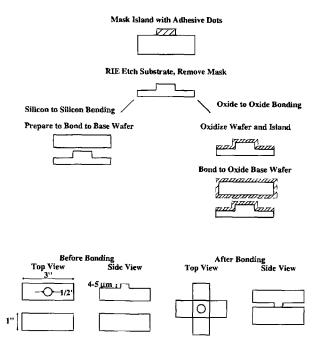

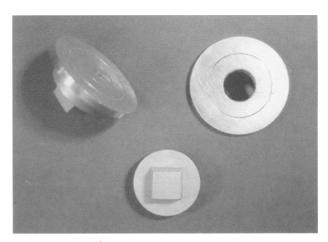

Sample geometry.--The test geometry that we have developed is simple to fabricate, eliminates the effects due to edge beveling and coding, repeatably produces samples which are void free, and is rotationally symmetric (does not require upper and lower wafer alignment). The standard sample geometry consists of a 0.5 in. diam circle etched into one of the wafers while the remaining wafer remains flat. The height of the mesa is typically 4 µm which ensures that only the fabricated feature region is bonded.

The mesas can be produced by chemical etching or reactive ion etching (RIE). The first technique requires photolithographic procedures which include the growth and removal of a mask oxide and photoresist. Because the ef-

\* Electrochemical Society Active Member.

Downloaded on 2019-09-30 to IP 169.237.45.91 address. Redistribution subject to ECS terms of use (see ecsdl.org/site/terms use) unless CC License in place (see abstract).

Fig. 1. Mechanical test sample fabrication method.

fects of microroughness and residual organic contamination on the surface play a significant role in the quality of the bonded interface, this technique was abandoned in the study of interfacial kinetics. The RIE sample technique, outlined in Fig. 1, limits the contamination possibilities and has a turnaround time of approximately 90 min. Adhesive labels are used as the mask and therefore allow for a variety of feature shapes and sizes to be studied.

The samples in these experiments were prepared for bonding by an RCA base bath process following a standard RCA clean. The following steps were used in this process: RCA clean; 1. base bath (NH<sub>4</sub>OH:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O, 1:1:6) 10 min at 75°C, 2. DI water rinse, 3. acid bath (HCl:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O, 1:1:5) 10 min at 75°C, 4. DI water rinse, 5. HF dip; base bath surface activation step; 6. base bath  $(NH_4OH)$ :  $H_2O_2:H_2O$ , 1:1:6) 5 min at 75°C, 7. DI water rinse and spin dry. Following surface activation, the 1 in. square samples are placed in a table top portable spinner (Laurell Technologies, Model No. WS200-6) which has been modified to hold two samples face to face but separated by 5 mm. This creates a micro-cleanroom environment similar to the one described by Mitani.<sup>4</sup> In this manner the two test samples are rinsed, spun dry, and contacted with a reduced possibility of particle contamination. Bonded area is determined by transmission infrared photography.

All heat-treatments above 300°C were conducted in tube furnaces with flowing dry nitrogen while the low temperature anneals were done in atmospheric box furnaces. In all cases a temperature variation of  $\pm 3$ °C was maintained. Samples slated for transmission electron microscopy (TEM) examination were prepared in pairs. The fracture strength of one of the samples in the pair was determined by a mechanical pull test and compared with expected values<sup>5</sup> to ensure that the wafer lot was not contaminated. The remaining sample was prepared for cross section examination in the TEM.

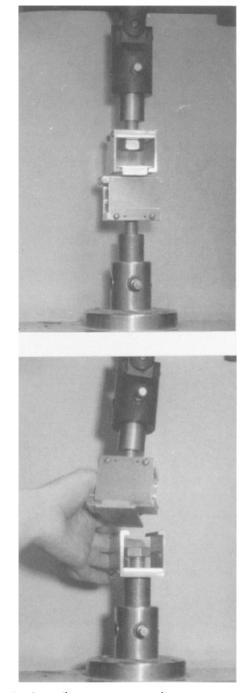

*Mechanical grip systems.*—The measured interfacial strength of a bonded wafer pair is very sensitive to the alignment of the force axis with respect to the interface normal. The sample grips and chuck modifications we have made ensure uniaxial loading of the specimen during mechanical testing. Because the specimens are thin it is necessary to attach an aluminum sample grip to each bonded pair as shown in Fig. 2. This is done using a commercially

available,<sup>a</sup> high strength, room temperature curing epoxy such as J.B. Weld<sup>®</sup>. The sample grips are T-shaped and slide horizontally into a sample chuck on the testing machine as shown. The pivotal motion of the upper chuck assembly and the rotational freedom of both the upper and lower chucks allows the sample to be slid into position and aligned precisely with the force axis. It should also be noted that because the bonded feature is smaller than the total sample size there is a uniform layer of adhesive underlying the bonded feature. When whole wafers are tested the adhesive cannot uniformly extend to the wafer's edge without risk of gluing the grips together. Hence the bonded region is not uniformly supported during the test and this increases the possibility of a reduced strength measurement due to localized bending of the interface.

<sup>a</sup> J.B. Weld<sup>®</sup> is commercially available at hardware stores or through the company. Inquiries can be addressed to J.B. Weld, PO Box 483, Sulphur Springs, TX 75482, (903) 885-7696. European Office: Unit 3 Polygon Business Center, Blackthorne Rd., Poyle Trading Estate, Colnbrook, Slough, SL3 OTF, England.

Fig. 2. Tensile test apparatus and mounting process.

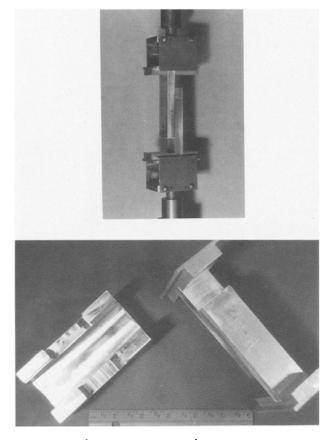

Fig. 3. Shear test apparatus and mounting process.

The shear tests are performed using the same tensile testing apparatus although the bonded interface is aligned parallel to the sample grips and chuck assembly. A special holder is used when the samples are epoxied to the sample grips which ensures that the upper and lower grips are parallel. It is important to note that because the test area is circular it is not necessary to be concerned about rotation of the sample on the sample grip unless crystallographic orientation is studied. The shear test apparatus is shown in Fig. 3.

Whole wafer testing is also possible although the results are less repeatable due to the presence of stress intensity factors such as the inevitable void near the wafer periphery due to the wafer beveling and coding and the adhesive problems discussed previously. The circular sample grips contain annular alignment rings as shown in Fig. 4 and 5, and slide into position on the tensile testing chucks.

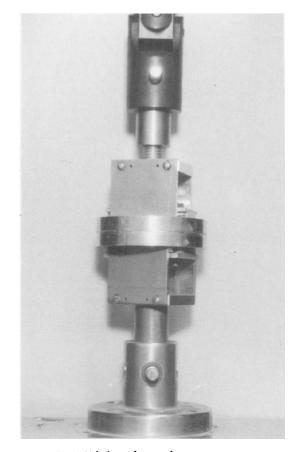

Torsion tests are performed on bonded wafers by centering the circular bonded region on aluminum mounts similar to the ones used for whole wafer tensile tests. The aluminum sample grips are then attached to the chuck assembly of a torsion test machine. These mounts are shown in Fig. 5.

Mechanical testing is done on Instron test machines equipped with load cells which vary from 100 g to 50 kN. The crosshead speed is maintained at 0.0508 cm/min (0.022 in./min) and the data are recorded on a computer and chart recorder. The fracture strength is computed as force per unit area based on the bonded feature size and load at fracture. The systematic errors include  $\pm 2$  pound resolution on the load cell readout and a 5% error in determination of the bonded area using digital image analysis of transmission infrared photographs of the interface. The systematic errors account for less than 4% error in the measured fracture strength. The actual error due to reproducibility between samples is 10% at a maximum. The data presented are the average values from several lots of samples. No fewer than three samples were tested at each time and temperature. In most cases, 5-10 samples were pulled at each condition. The measured errors result from contam-

Fig. 4. Whole wafer tensile test apparatus.

inated samples, poor alignment of the test apparatus, and flaws which initiate in weaker areas of the interface. The apparent localization of fully bonded areas that ultimately consume the interface are the primary cause of poor reproducibility and certainly indicate that a composite model of the strength should be developed.

#### Results

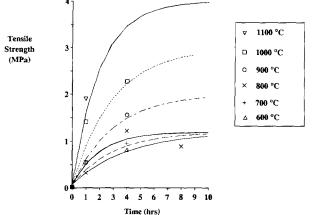

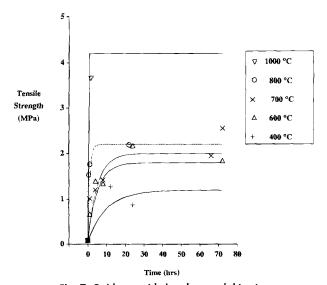

The strength of bonded Si-Si wafers has been found to vary from 0.08  $\pm$  0.043 MPa at contact to a maximum of 4.25 MPa after a several hour 1000°C anneal. The kinetics for Si-Si bonded wafers are shown in Fig. 6. The ultimate strength of the bonded SiO<sub>2</sub>-SiO<sub>2</sub> wafers was significantly less and the kinetics are much slower as shown in Fig. 7. The contact bond strength of the Ox-Ox material was determined to be  $\leq 0.02$  MPa (at the resolution limit of our equipment) and the maximum interfacial strength measured was 2.7 MPa. Extended time anneals were not performed on the Ox-Ox material to determine the ultimate

Fig. 5. Torsion test apparatus.

Mostly Interface Failure

Fig. 6. Slicon to silicon bond strength kinetics.

strength limit. These results are consistent with the mechanical pull strength values of Abe *et al.*, which range from 20-70 MPa, <sup>2</sup> and those of Shimbo *et al.*, in the 5-20 MPa range.<sup>3</sup> These values are necessarily higher due to the test geometry used.

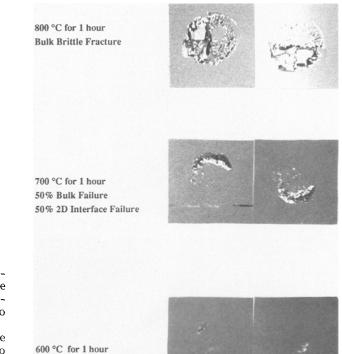

Figure 8 shows the progression of the fracture surface features from a purely two-dimensional interface failure to a typical three-dimensional fracture surface which occurs in fully bonded areas. Empirically, the onset of a three-dimensional fracture surface was found to occur at 1.25-1.5 MPa in localized regions. Close examination of the beach marks on the fracture surface indicated that the fractures originate at interfacial sites as well as bulk sites.

Shear and torsion tests were performed on high temperature annealed Si-Si bonded materials. Preliminary results revealed a shear strength of 10.86  $\pm$  0 MPa for a pair of samples which had been annealed at 900°C for 1 h. Similar bonded wafer pairs were tested in torsion and were found to fracture at 9.19  $\pm$  0.52 N m.

#### **Discussion of Results**

The fitted lines to the kinetics data shown in Fig. 6 and 7 are the result of assuming that the interfacial bond strength is proportional to the number of Si-O-Si bonds formed. Using the model proposed by Stengl *et al.*, <sup>6</sup> the concentration of interfacial oxide bonds is given by the decomposition of silanol bonds

$$\frac{d[\text{SiOSi}]}{dt} = k(n_{o} - [\text{SiOSi}])$$

[1]

where *k* is the rate constant given by the Arrhenius expression,  $1/\tau \exp(E_a/k_BT)$ . The rate constant contains an empir-

Fig. 7. Oxide to oxide bond strength kinetics.

Fig. 8. Fracture surfaces of 0.5 in. circular bonded mesas.

ical delay time,  $\tau$ , and  $E_{a}$ ,  $k_{\rm B}$ , and T have the usual meaning of activation energy, Boltzmann's constant, and absolute temperature, respectively. The Si-O-Si concentration is given by [SiOSi] and  $n_{o}$  is the initial number of bonding sites. Integration of this equation results in<sup>6</sup>

$$[SiOSi](t) = n_0 [1 - \exp(-kt)]$$

[2]

where *t* is time. Assuming that the surface energy is directly proportional to the evolution of SiOSi bonds the theory anticipates that the surface energy should increase proportionately from  $634 \text{ erg/cm}^2$ , the value for the hydroxylated surface, to the value for quartz, 1930 erg/cm<sup>2</sup>. The equation for this relationship is given by<sup>6</sup>

$$W = [(1960 - 634) \times (1 - \exp(-kt)) + 634]$$

[3]

Assuming that the interfacial bond strength is proportional to number of bonds, the fracture strength,  $\sigma(t)$ , will increase from the contact bond strength of  $\sigma_0$  to a maximum value of  $\sigma_{max}$  according to the following expression<sup>6</sup>

$$\sigma(t) \approx (\sigma_{\max} - \sigma_{o}) \times \left(1 - \exp\left(\frac{-t}{\tau}\right)\right) + \sigma_{o}$$

[4]

Using this relationship the bond strength data were theoretically modeled using the following fitting parameters found in Table I.

This kinetic information can be used to compare the time necessary to achieve a given strength value to the time limit imposed by thermal processes. For instance, Fig. 9 compares the thermal budget imposed by a 0.01  $\mu$ m diffusion length limit to the time necessary to initiate three-dimensional fracture (~1.25 MPa). This strength value is sufficient to allow for grinding and thinning processes for SOI applications. Subsequent annealing can be used to strengthen the interface after removal of the etch stop if increased strength is required. Clearly, Fig. 9 illustrates the

| Table I. Fitting parameters | for kinetic | s data of Fi | g. 7 and 8. |

|-----------------------------|-------------|--------------|-------------|

|-----------------------------|-------------|--------------|-------------|

| Temp. (°C)                                                                                       | 1100 | 1000                              | 900        | 800                        | 700                        | 600                        | 400                                     |

|--------------------------------------------------------------------------------------------------|------|-----------------------------------|------------|----------------------------|----------------------------|----------------------------|-----------------------------------------|

| $\sigma_{max}$ (Si-Si) MPa<br>$\tau$ (Si-Si) h<br>$\sigma_{max}$ (Ox-Ox) MPa<br>$\tau$ (Ox-Ox) h | 4.0  | $4.2 \\ 0.1 \\ 3.0 \\ 3.0 \\ 3.0$ | 2.0<br>3.0 | $2.2 \\ 1.0 \\ 1.2 \\ 2.0$ | $2.0 \\ 5.0 \\ 1.2 \\ 3.0$ | $1.8 \\ 5.0 \\ 1.2 \\ 4.0$ | $\begin{array}{c} 1.2\\10.0\end{array}$ |

Downloaded on 2019-09-30 to IP 169.237.45.91 address. Redistribution subject to ECS terms of use (see ecsdl.org/site/terms\_use) unless CC License in place (see abstract).

Fig. 9. Thermal budget comparison. The time necessary to initiate three-dimensional fracture vs. the time limit imposed by a 0.01  $\mu$ m diffusion length for boron dopants. The diffusion length was determined by  $x = (Dt)^{1/2}$ .

desire to reduce annealing temperatures to below 800°C for strict compliance with dopant profile configurations but also shows that the times necessary to achieve even the minimal strength requirements are very long at low temperature.

The plateaus reached by the strength kinetics data below 700°C indicate that either the final stage of the bonded reaction in not being fully realized or there is another mechanism responsible for the strength behavior. We have found that even at 200°C wafer bonded materials do achieve pull strengths equivalent to high temperature annealed samples if very long anneals, in excess of several weeks, are used. We therefore conclude that the oxidation process at the interface is thermodynamically probable but kinetically slow. The primary cause for the low strength with short annealing times at low temperatures can be determined by microstructural evaluation of the bonded interface. This result is contradictory to previous experimental evidence and theory which suggested that strong bonds did not develop at low temperatures. This work dramatically shows that although the kinetics are slow, it is possible to achieve interfacial bonds with sufficient strength to fracture the bulk substrate material when tested. This implies that the process is not limited by temperature but rather by time.

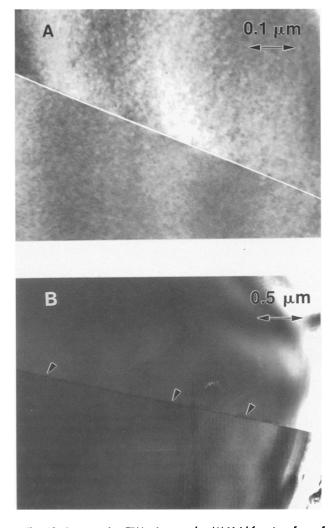

Cross-sectional TEM analysis of the bonded interfaces has shown that the interfacial region which develops between the bonded materials is riddled with microvoids in the low temperature bonded materials as shown in Fig. 10b while high temperature bonded materials have uniform, continuous interfaces as in Fig. 10a. This is undoubtedly the result of trapped volatiles. Data by Harendt *et al.*, where the trapped gases were released in vacuum by cleavage of the sample and analyzed with a mass spectrometer, determined that the gaseous byproducts were primarily water and oxygen.<sup>7</sup>

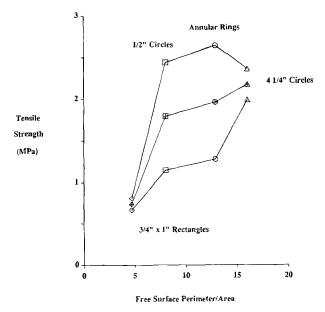

Further evidence to support the trapped gases hypothesis is found when the bond strength is studied as a function of bonded area geometry. If the mean free distance to a free surface is minimized then the strength of the interface should develop more rapidly. To test this hypothesis we compared four different geometries of bonded areas, four 1/4" diam circles, 1/2" diam circles, 5/8" diam annular rings with 1/4" wall thicknesses, and 3/4"  $\times 1/2$ " oblong rectangles. Figure 11 is a plot of the bond strength after 72 h of

Fig. 10. Cross section TEM micrographs. (A) Void free interface of a sample annealed at 100°C for 1 h. (B) Typical low temperature sample annealed at 600°C for 2 h. Numerous microvoids shown along the bonded interface.

annealing time at  $600^{\circ}$ C vs. the free surface perimeter to bonded area ratio. As demonstrated in the figure, samples with short mean free paths to a free surface such as the 1/4''circles bond very well, while the large area samples do

Fig. 11. Geometry effects in low temperature bonding kinetics.

not. We suggest that this is further evidence that the trapped gases are the cause of poor low temperature bonding strength.

#### Conclusions

This work has systematically determined the evolution of the interfacial bond strength of silicon to silicon and silicon dioxide to silicon dioxide bonded wafers. The ability of low temperature anneals to initiate the formation of Si-O-Si bonding at the interface has been shown. However, the interfacial regions fail to achieve full strength over large areas due to trapped gases. These kinetics can be used to predict appropriate thermal annealing treatments for a desired strength requirement. The annealing times necessary to achieve good bond strength at temperatures below 600°C are prohibitively long unless small bonded geometries are used. However, excellent results can be achieved at 700-750°C in very reasonable times without the risk of diffusional broadening of dopant layers.

# Acknowledgments

The authors wish to acknowledge funding by the UC MICRO program and Harris Semiconductor. The authors are grateful to Tony Burton and Lance Tom for their help in the shear and torsion testing.

Manuscript submitted Aug. 30, 1993; revised manuscript received July 21, 1994.

Dr. Farrens assisted in meeting the publication costs of this article.

#### REFERENCES

- W. P. Maszara, G. Goetz, A. Caviglia, and J. B. McKitter-ick, J. Appl. Phys., 64, 4943 (1988).

T. Abe, T. Takei, A. Uchiyama, K. Yoshizawa, and K.

- Tanzawa, Jpn. J. Appl. Phys., 29, L2311 (1990). 3. M. Shimbo, K. Furukawa, K. Fukuda, and K. Tanzawa,

- J. Appl. Phys., 60, 2987 (1986).

4. K. Mitani, V. Lehmann, R. Stengl, D. Feijoo, U. M. Gösele, and H. Z. Massoud, Jpn. J. Appl. Phys., 30, 615 (1991).

- 5. S. N. Farrens, B. Roberds, M. C. Boettcher, M. S. Ismail, R. W. Bower, C. A. Desmond, and C. E. Hunt, in Thin Films: Stresses and Mechanical Properties III, W. D. Nix, J. C. Bravman, E. Arzt, and L. B. Fruend, Editors, p. 239B.

- p. 239B.

R. Stengl, T. Tan, and U. Gösele, Jpn. J. Appl. Phys., 28, 1735 (1989); MRS Proc., 287 (1992).

C. Harendt, B. Hofflinger, H. Graf, and E. Pentaker, Sen-

- sors and Actuators, A26-A27, 87 (1991).

# Effect of Plasma Etching Edge-Type Exposures on Si Substrates: A Correlation Between Carrier Lifetime and Etch-Induced Defect States

# Tieer Gu, O. O. Awadelkarim, S. J. Fonash, J. F. Rembetski,<sup>a</sup> and Y. D. Chan<sup>b</sup>

Electronic Materials and Processing Research Laboratory, The Pennsylvania State University, University Park, Pennsylvania 16802

# ABSTRACT

Recently there has been increasing evidence that poly-Si gate reactive ion etching produces gate  $SiO_2$  edge damage in MOS transistors in addition to the well-known areal plasma charging stress damage. This edge damage is believed to be due to direct exposure of these regions to plasma photon and particle fluxes. To explore this edge type damage further, the effect of this direct exposure on Si substrate is studied using blanket SiO<sub>2</sub>/Si structures subjected to poly-Si overetches. These structures were then characterized using capacitance-voltage and deep level transient spectroscopy measurements. Defect states are found in the Si substrate and at the  $SiO_2/Si$  interface after this type of overetch exposure. Their presence is shown to correlate with the degradation of the minority carrier generation lifetime and surface generation velocity observed by Zerbst measurements.

While plasma charging stress during poly-Si gate reactive ion etching (RIE) is well known to cause MOSFET gate oxide degradation,<sup>1-5</sup> there is increasing evidence that SiO<sub>2</sub>-Si degradation can also occur at the gate edges due to exposure of these regions to plasma photon and particle fluxes and this effect can become even more important for shorter channel FETs.<sup>5.6</sup> In this study we look to see if such direct plasma exposures could also potentially introduce damage to the underlying Si substrate, especially in cases where the gate oxide may become too thin to protect the Si substrate underneath. In addition, we look to see if this Si substrate damage correlates with plasma exposure-induced degradation of SiO<sub>2</sub>-Si interface. To undertake this study we use blanket etching of  $SiO_2/Si$  structures and we find that, in spite of the Si substrate being covered by the thin oxide layer ( $\sim 120$  Å), defects can still be created by these exposures in the Si substrates with concentrations that are significant enough to degrade carrier generation lifetime.

## **Experimental Procedure**

Six inch, n- and p-type wafers with  $1\text{--}3\times10^{14}\,\text{cm}^{-3}\,\text{dop-}$ ing concentrations were used in this study. A 120 Å thick gate oxide was thermally grown on these wafers at 900°C in a dry O<sub>2</sub> ambient. To simulate the direct plasma exposure type of situation which occurs at gate edges of MOSFET devices in poly-Si overetching, the blanket SiO<sub>2</sub>/Si material systems were exposed to poly-Si overetch plasmas in two different etching tools. One of the tools was a magnetically enhanced reactive ion etcher (MERIE), while the other one was a conventional RIE etcher. A Cl<sub>2</sub>-based poly-Si etch chemistry was used in the conventional RIE tool

#### Table I. Process conditions used in RIE and MERIE tools.

| Tool                                                                                      | RIE                                                                       | MERIE                                                                        |  |  |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|

| Chemistry<br>Gas flow rates (sccm)<br>Pressure (mTorr)<br>Power (W)<br>Magnetic field (G) | $\begin{array}{c} {\rm Cl_2/He/O_2}\\ 200/400/8\\ 425\\ 275\\\end{array}$ | $\begin{array}{c} {\rm Cl_2/HBr/O_2}\\ 30/30/5\\ 100\\ 150\\ 75 \end{array}$ |  |  |

<sup>a</sup> On assignment to SEMATECH from IBM, Burlington, Vermont. <sup>b</sup> On assignment to SEMATECH from Rockwell International, Newport Beach, California.

Downloaded on 2019-09-30 to IP 169.237.45.91 address. Redistribution subject to ECS terms of use (see ecsdl.org/site/terms use) unless CC License in place (see abstract).